# EDN Design ideas 2009

#### January 2009

Digitally programmable-gain amplifier uses divergent-exponential curve

Circuit indicates ac-mains-fuse failure

Isolation MOSFET-driver IC gets improved power efficiency at lighter loads

Synthesize variable resistors with hyperbolic taper

Increase the range of memorized voltage for a sample-and-hold device

Inexpensive self-resetting circuit breaker requires few parts

Sinusoid generator uses dual-output current-controlled conveyors

Perform timing for microcontrollers without using timers

#### February 2009

Convert signals to proper logic levels

DDR-differential-clock source on SOC drives two DDR-memory chips

Flying capacitor and negative time constant make digitally programmable-gain instrumentation amplifier

MOSFET prevents battery damage

Voltage doubler improves accuracy

Digital controller compensates analog controller

Circuit provides constant-current load for testing batteries

MOSFET-based, analog circuit calculates square root

"Hippasian" nonlinear VFC stretches dynamic range

Decoder lights the way

#### March 2009

Microcontroller converts digital-temperature-sensor readings without floating-point arithmetic

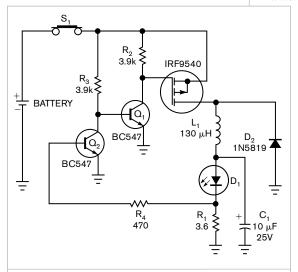

Discrete-component buck converter drives HB LEDs

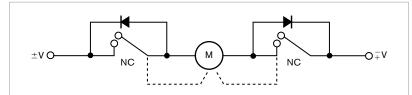

Drive a single-coil latching relay without an H-bridge circuit

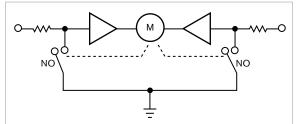

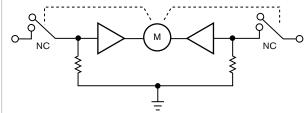

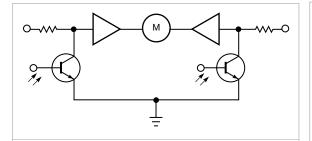

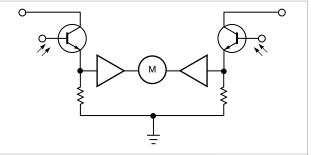

Limit switches control dc-motor H bridge

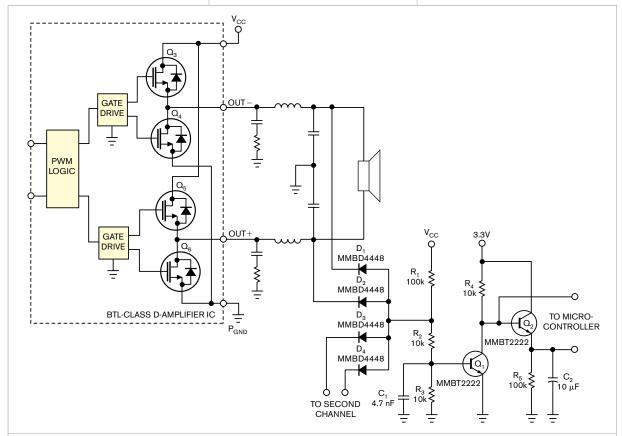

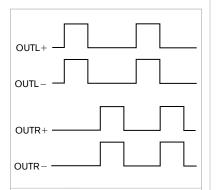

Implement a clip-detection circuit for BTL Class D amplifiers

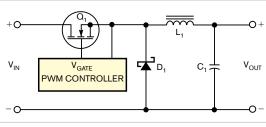

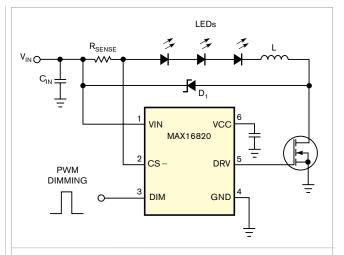

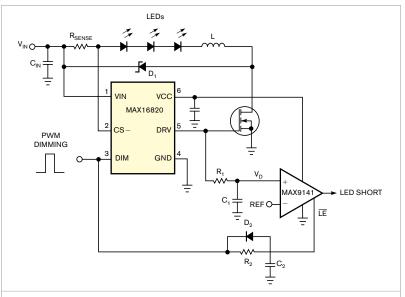

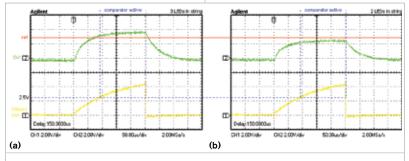

Buck converter uses low-side PWM IC

Isolated clock source acts as test generator

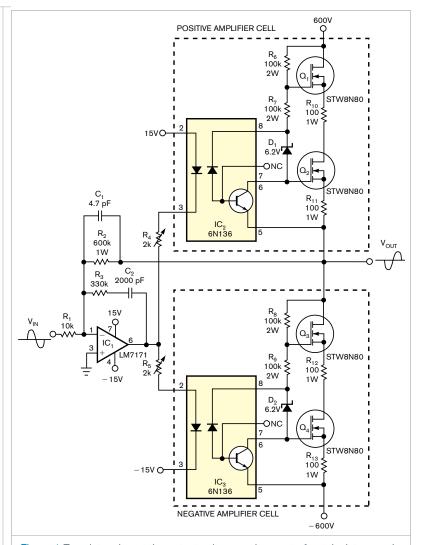

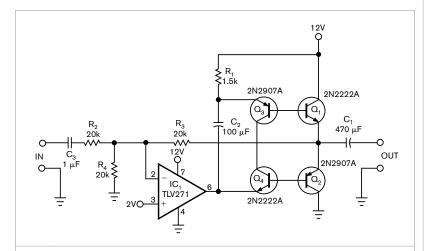

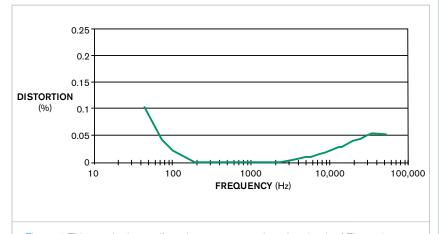

Class AB inverting amp uses two floating-amplifier cells

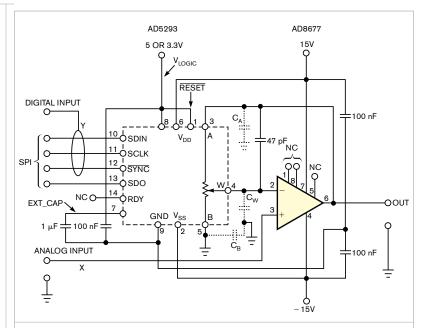

DPGA conditions signals with negative time constant

Instrumentation amplifier compensates system offset from single supply

#### April 2009

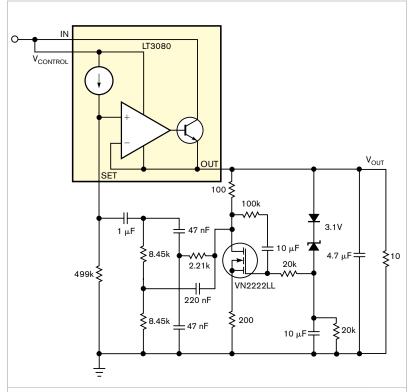

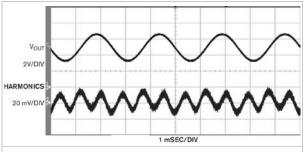

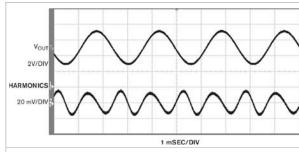

Twin-T power oscillators work as dc-biased ac sources

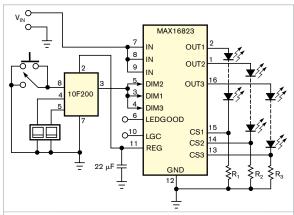

Diagnose LEDs by monitoring the switch-mode duty cycle

Single pin controls relay, intermittent buzzer, and status LED

Simple two-transistor circuit lights LEDs

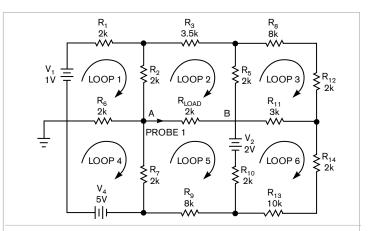

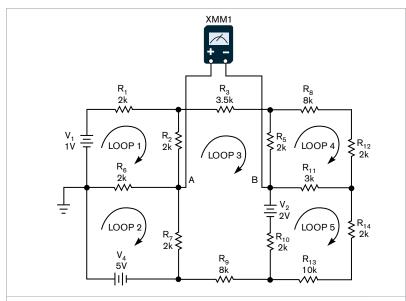

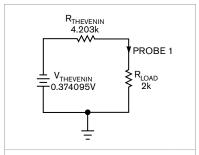

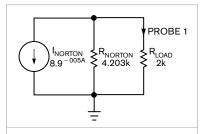

Simple method uses PSpice for Thevenin-equivalent circuits

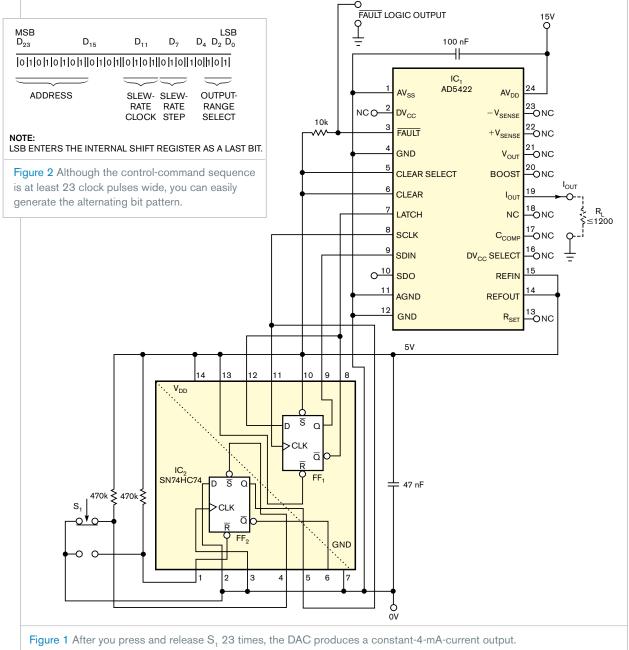

DAC and flip-flops form constant-current source

Convert negative inputs to positive outputs

May 2009

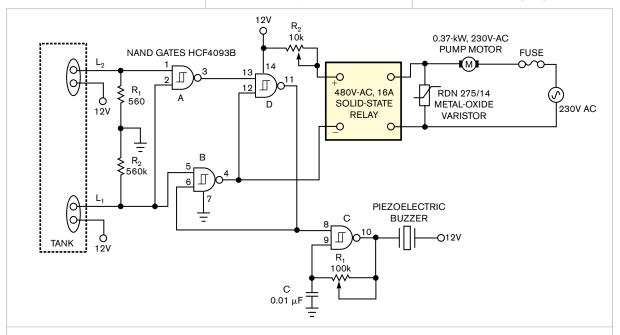

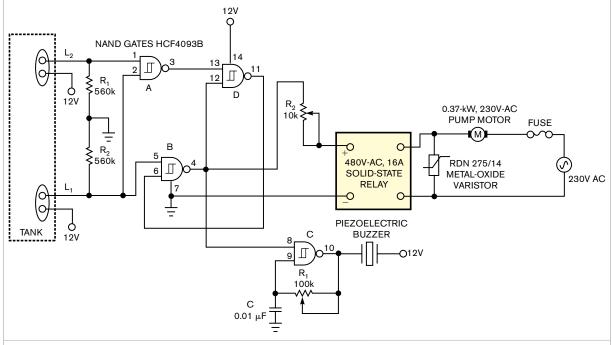

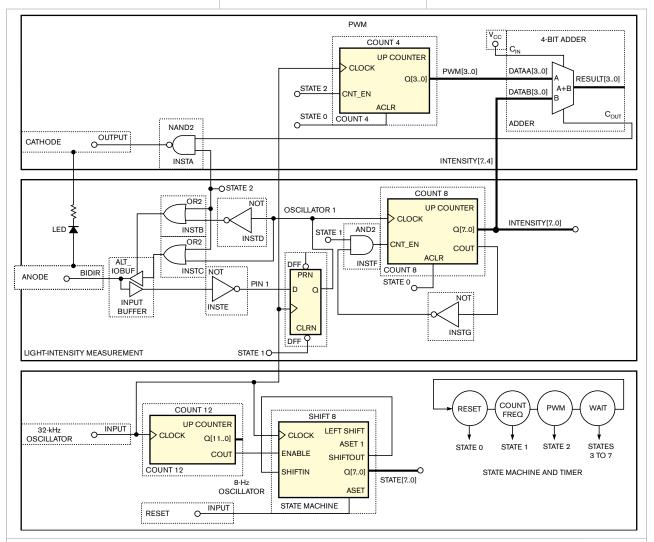

CMOS-NAND gates control sump pump

Use an LED to sense and emit light

Two instrumentation amps make accurate voltage-to-current source

Simple circuit indicates health of lithium-ion batteries

Current-sense monitor and MOSFET boost output current

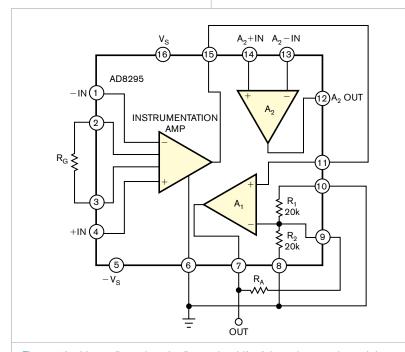

Multiplexed, programmable-gain, track-and-hold amplifier has instrumentation inputs

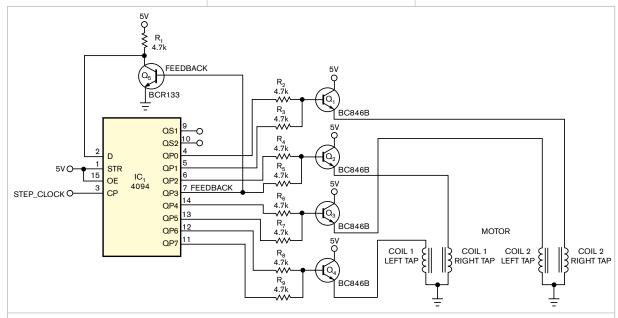

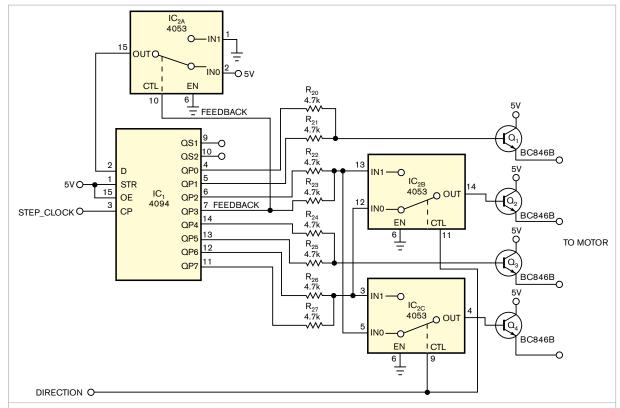

Simple circuit smoothly drives stepper motors

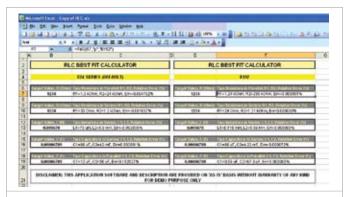

Excel spreadsheet yields RLC best-fit calculator

Automatically turn secondary lamp on or off

#### June 2009

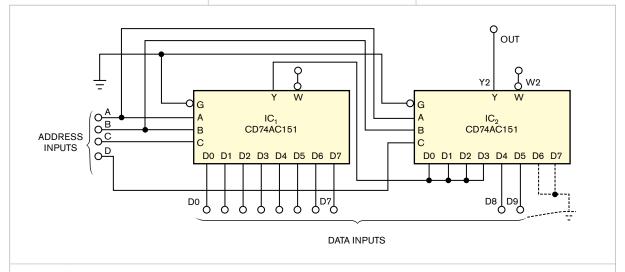

Fast 10-line-to-one-line data selector/multiplexer comprises only two ICs

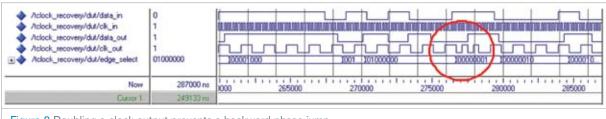

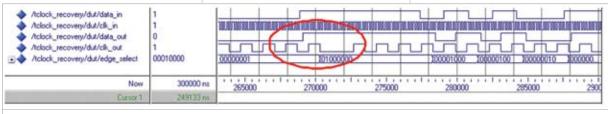

Implement a simple digital-serial NRZ data-recovery algorithm in an FPGA

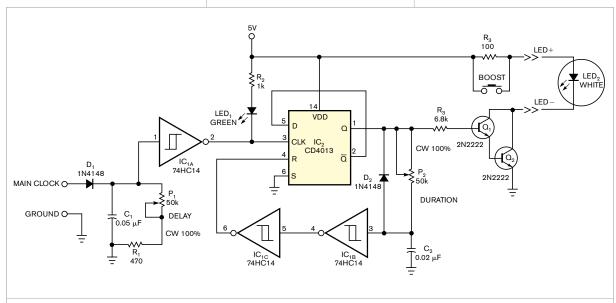

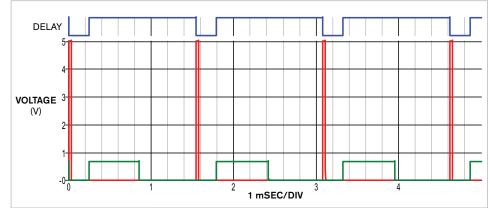

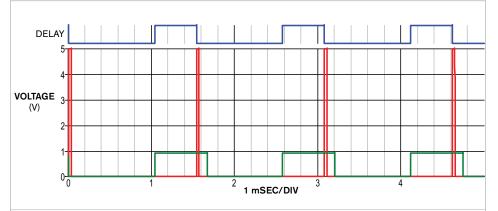

LED strobe has independent delay and duration

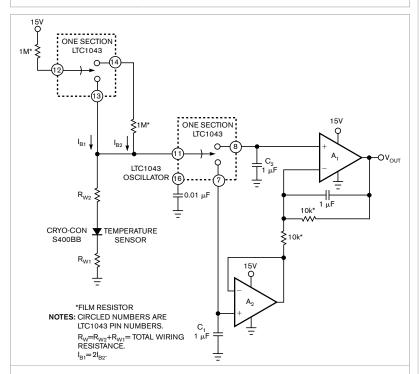

Cancel sensor-wiring error with bias-current modulation

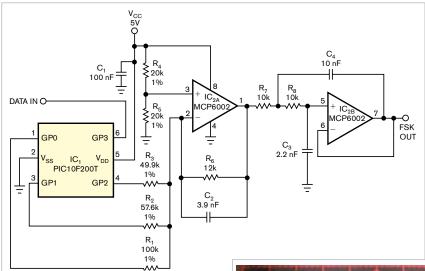

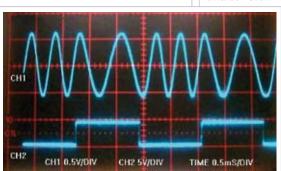

Simple FSK modulator enables data transmission over low-speed link

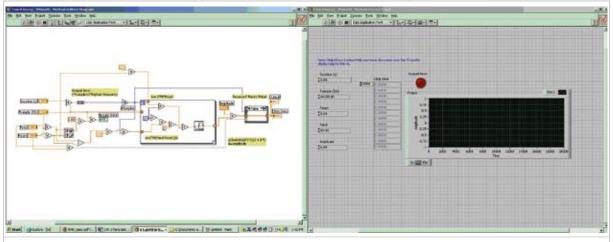

Create a swept-sine function in LabView with just one virtual instrument

Charlieplexing at high duty cycle

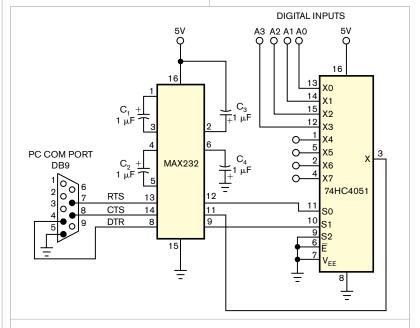

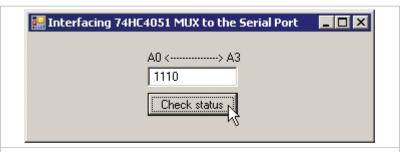

Serial port tests digital circuits

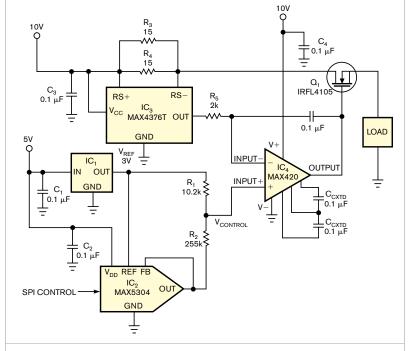

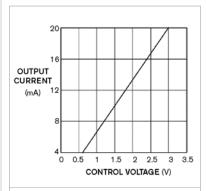

DAC calibrates 4- to 20-mA output current

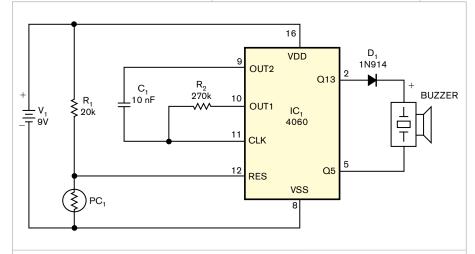

Alarm tells you to close the refrigerator door

#### July 2009

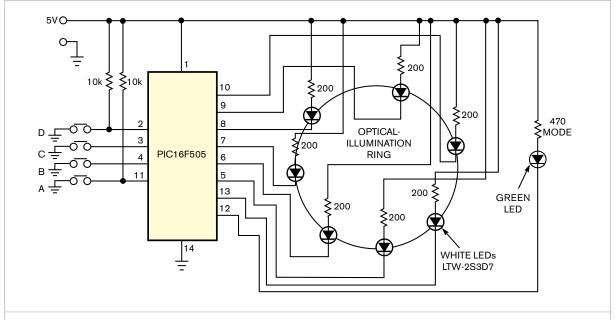

Illumination ring provides focused intensities

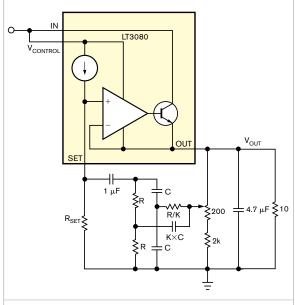

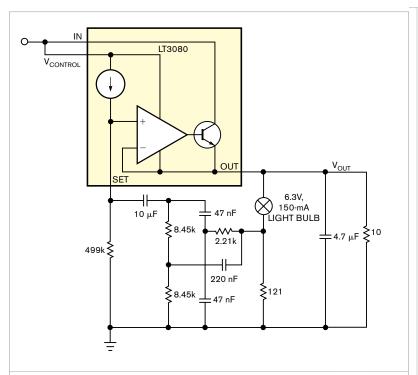

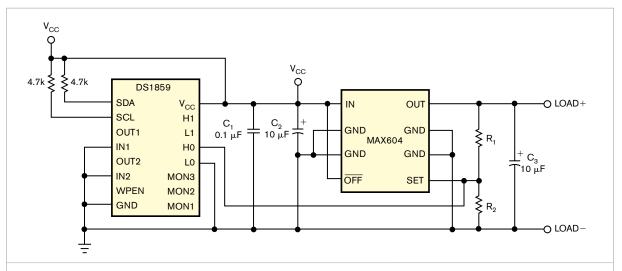

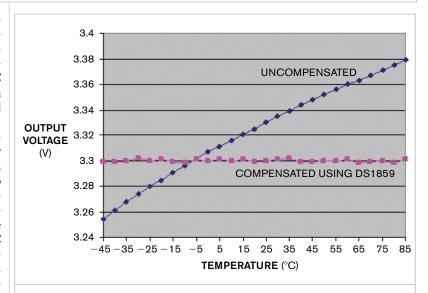

Digital variable resistor compensates voltage regulator

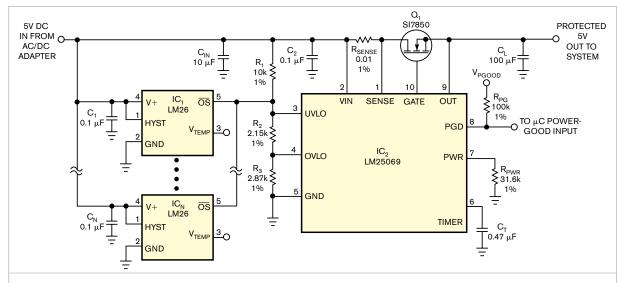

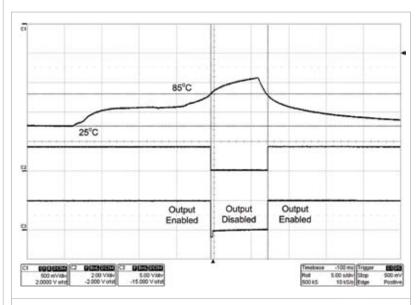

Hot-swap switch provides easy thermal protection

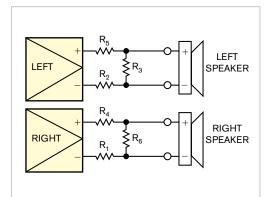

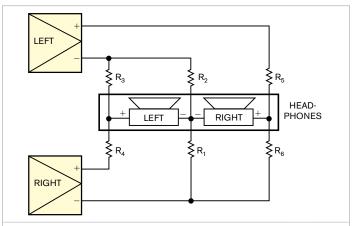

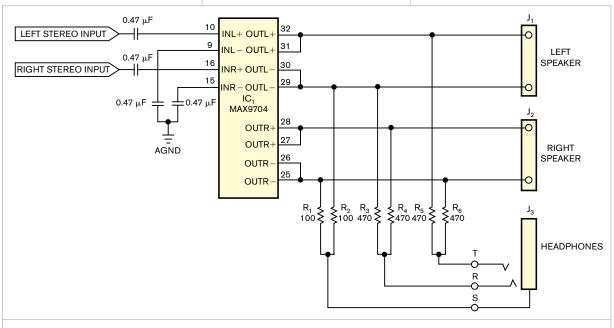

Add headphones to a Class D amplifier

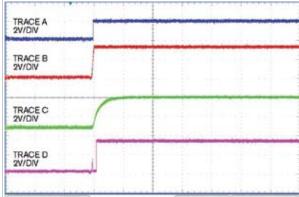

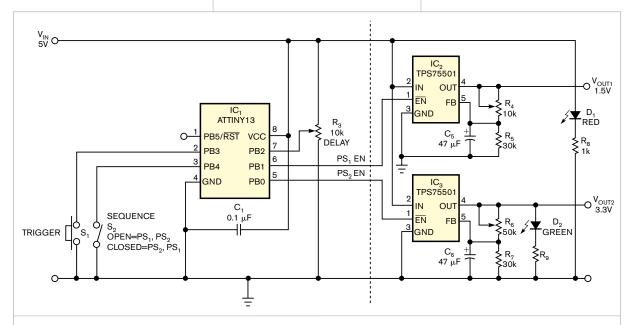

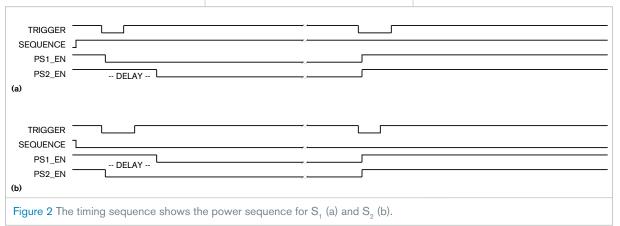

Circuit eases power-sequence testing

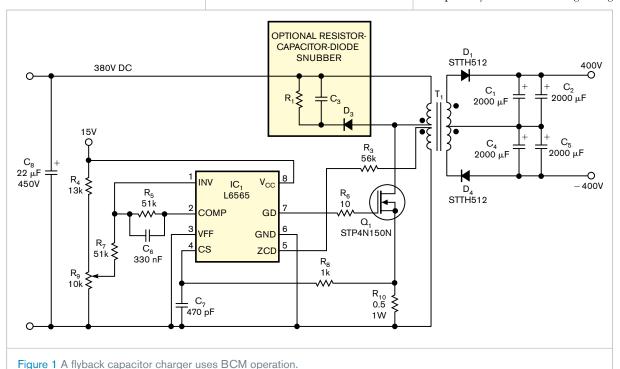

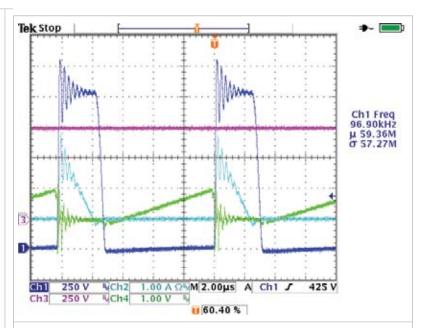

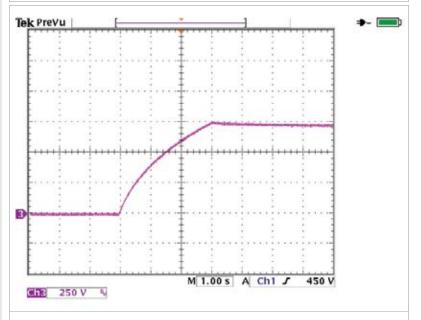

Quasiresonant flyback converter easily charges energy-storage capacitors

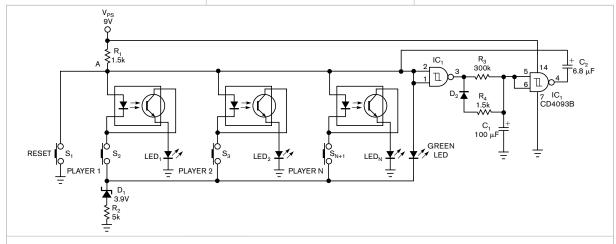

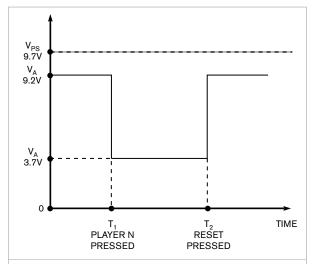

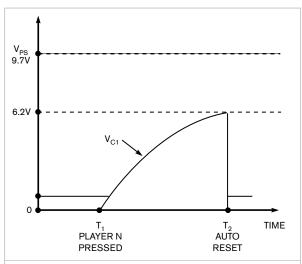

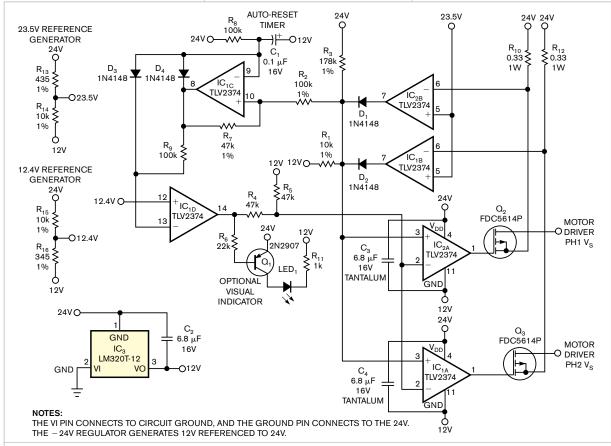

First-event detector has automatic-reset function

Signal-powered linear optocoupler provides isolated control signal

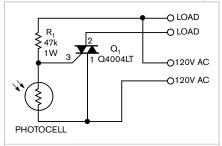

Dark-activated switch needs only three components

#### August 2009

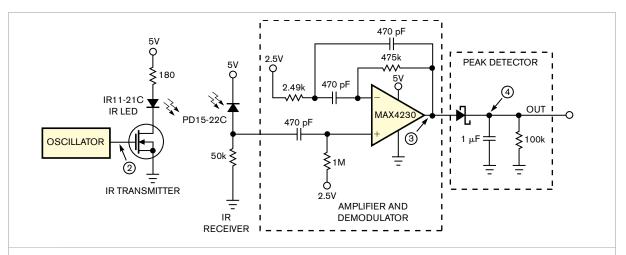

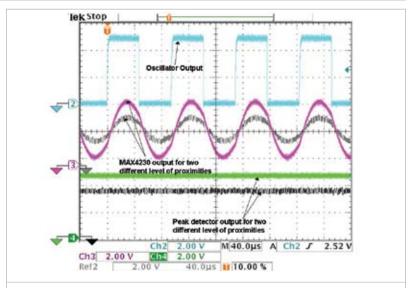

High-speed op amp enables IR-proximity sensing

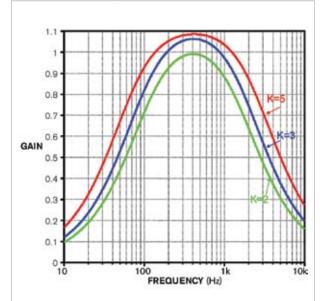

Set your lights to music

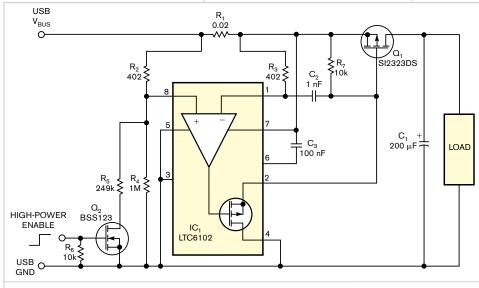

Current limiter allows large USB bypass capacitance

High-speed pulse modulator retains signal envelope

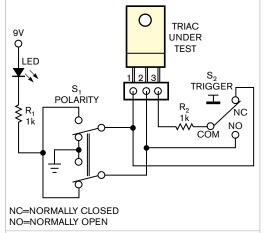

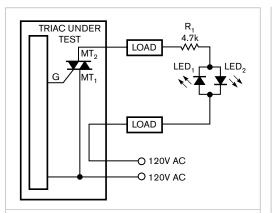

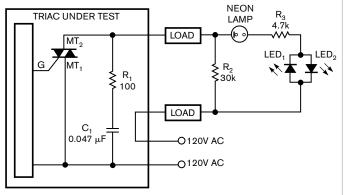

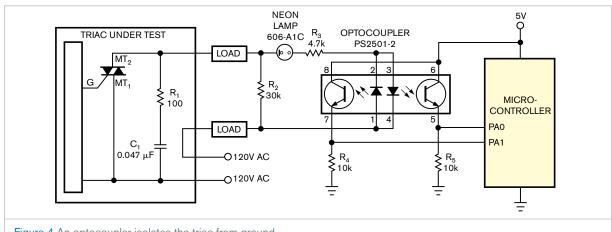

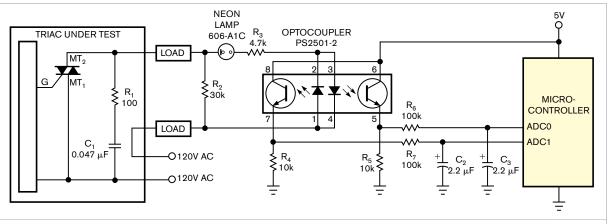

Triac tester allows for manual or automatic operation

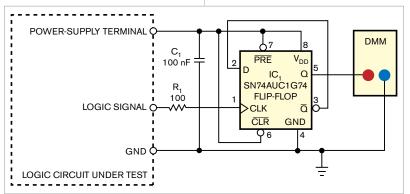

Handheld DMM copes with logic nanosecond-pulse-width waveforms

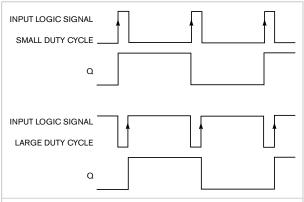

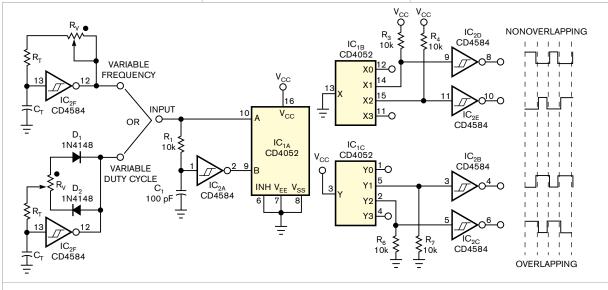

Build a simple complementary-bracket-pulse generator

Power-miserly voltage reference needs just one pin

#### September 2009

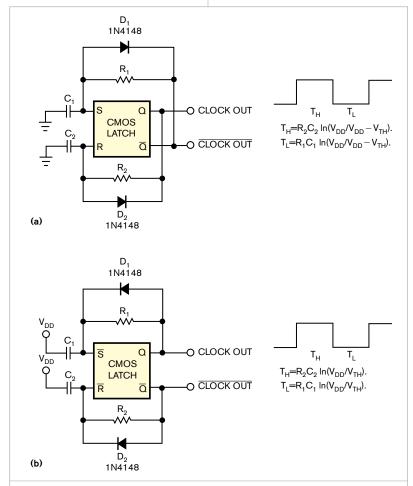

Turn a set/reset latch into an astable/monostable multivibrator

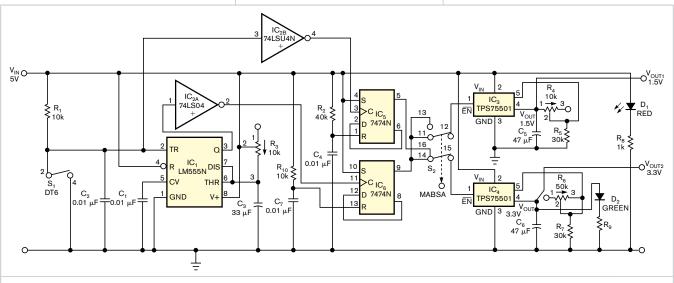

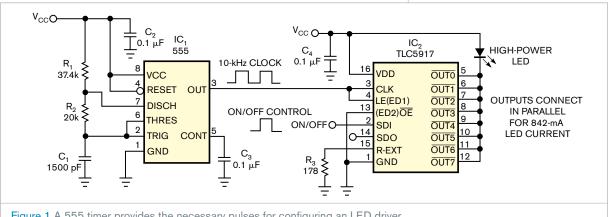

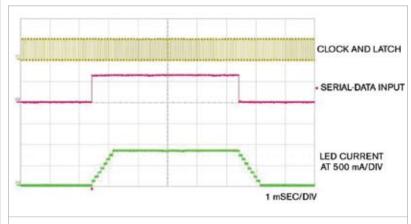

555 timer eliminates LED driver's need for microprocessor control

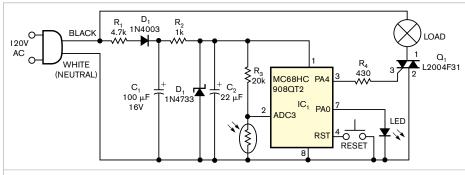

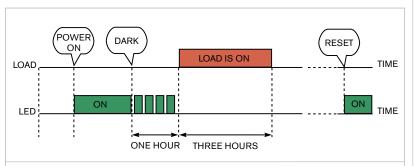

Smart photoresistor timer needs few components

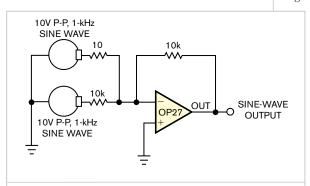

High-performance adder uses instrumentation amplifiers

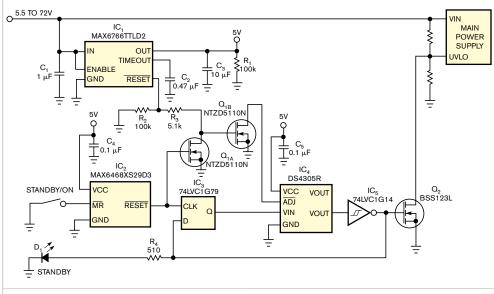

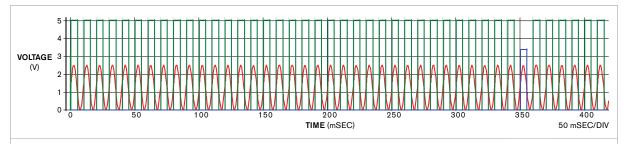

Nonvolatile standby/on switch remembers its state

Missing pulse detects position or produces a delay

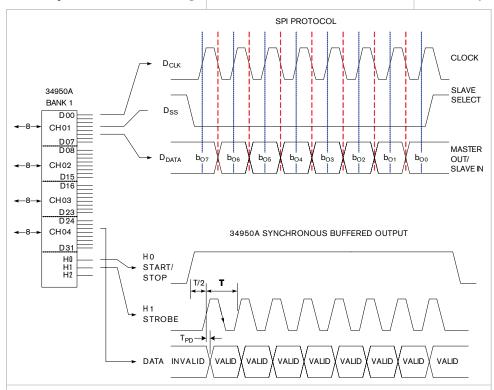

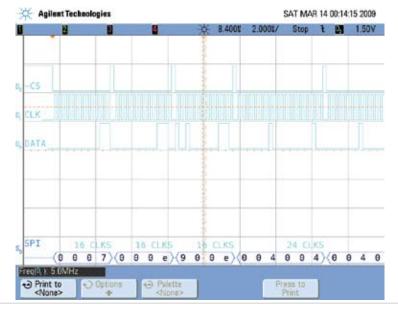

Emulate SPI signals with a digital-I/O card

Resistive DAC and op amp form hybrid divider

Connect two buttons with just two wires

#### October 2009

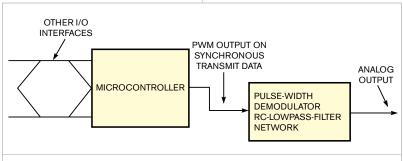

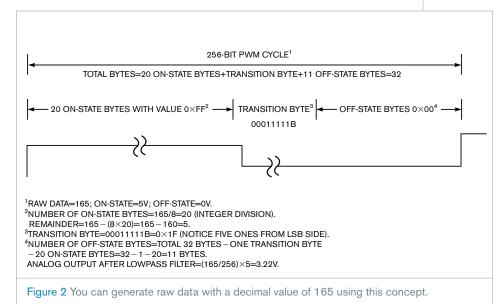

Unused port adds a PWM/analog channel to a microcontroller

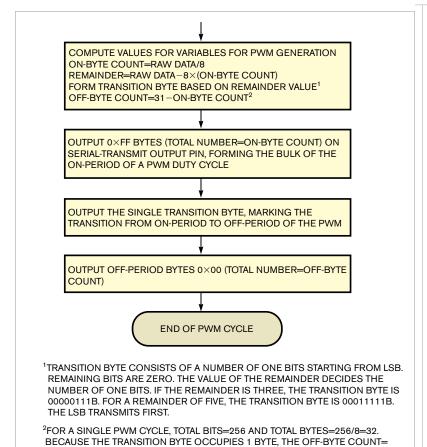

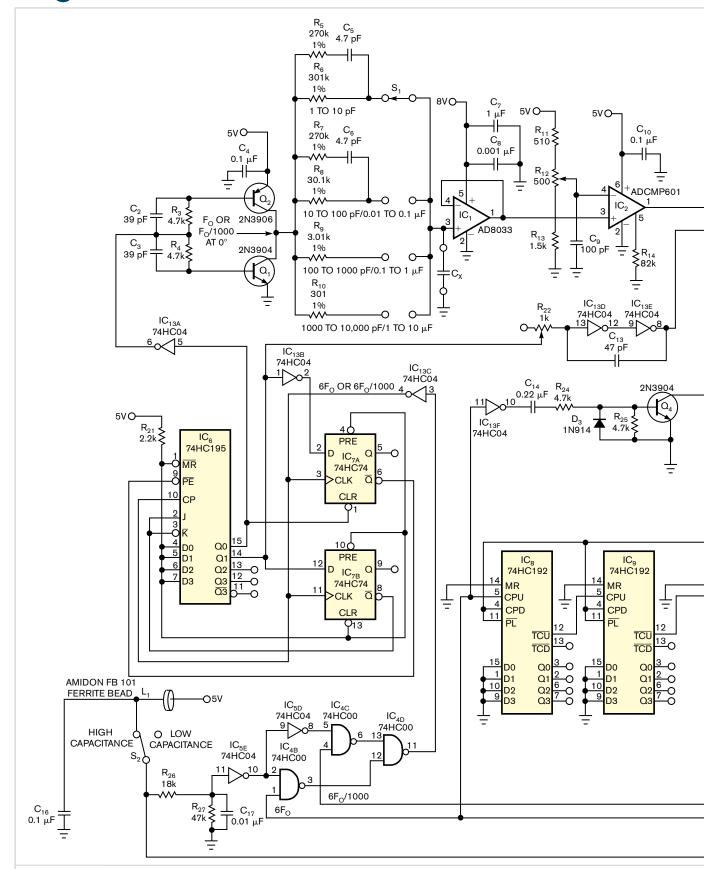

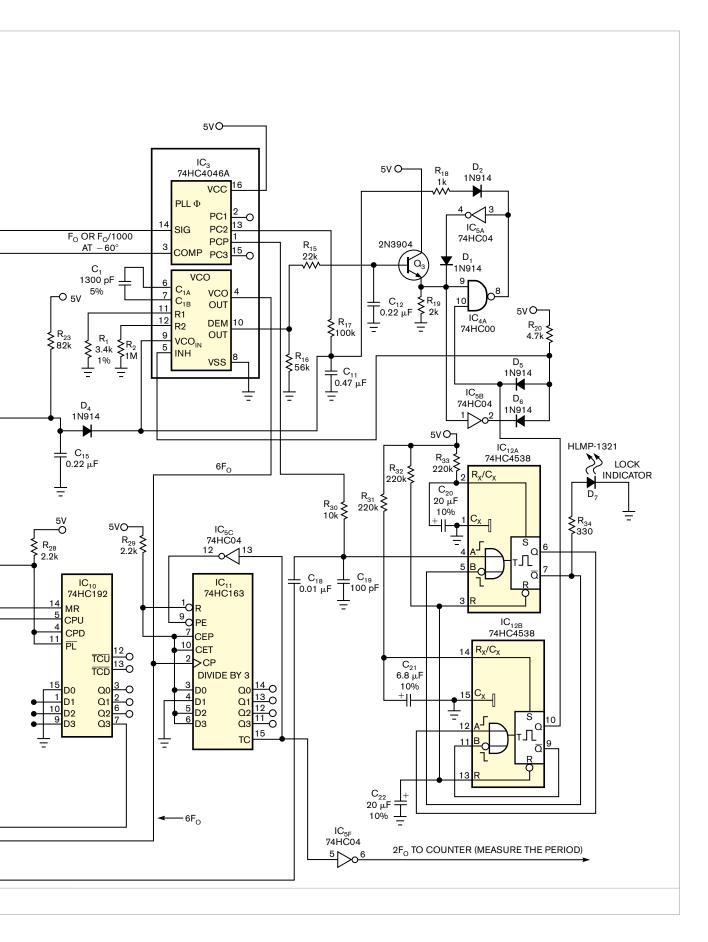

Capacitance meter uses PLL for high accuracy

Resistor compensates for instrumentation-amp gain drift

Astable multivibrator gets hysteresis from positive-feedback stage

Class B amplifier has automatic bias

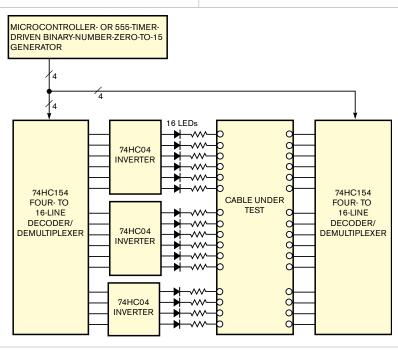

Cable tester uses LEDs to find faults

Dual-coil relay driver uses only two MOSFETs

#### November 2009

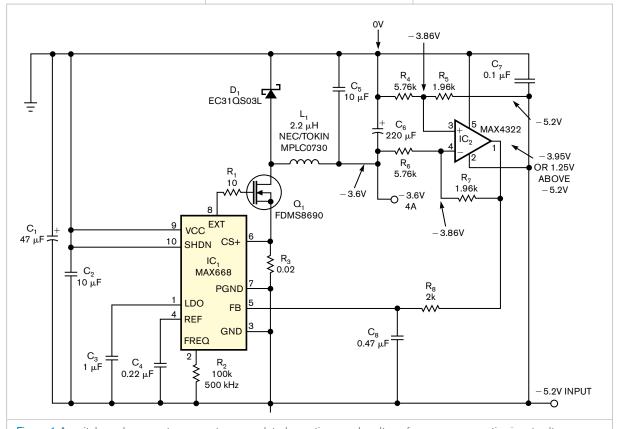

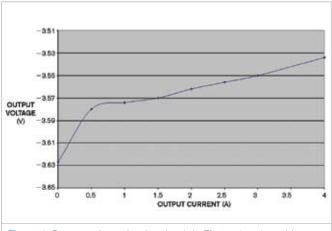

Negative-to-negative switch-mode converter offers high current and high efficiency

ADC for programmable logic uses one capacitor

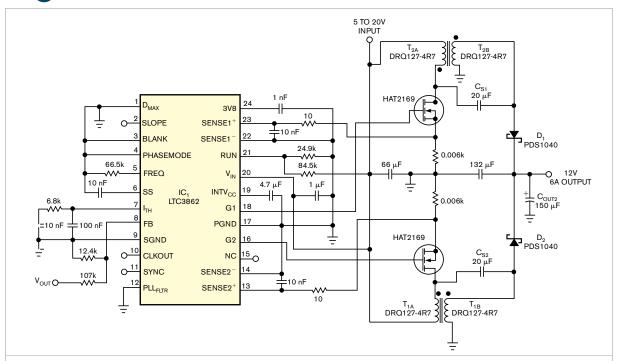

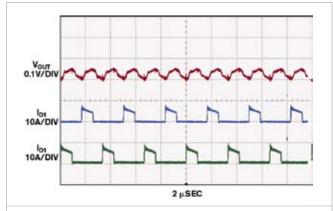

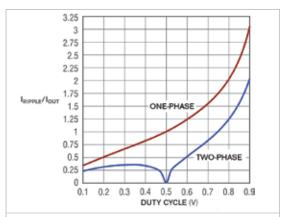

Use two phases to cut current and improve EMI

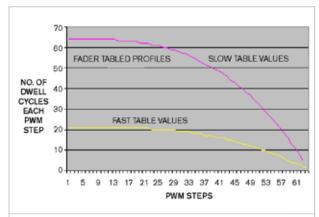

Fader switch uses inexpensive controller

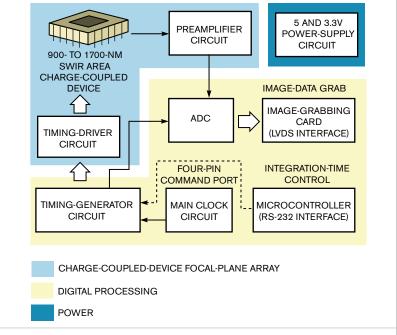

Inspect solar cells without a microscope

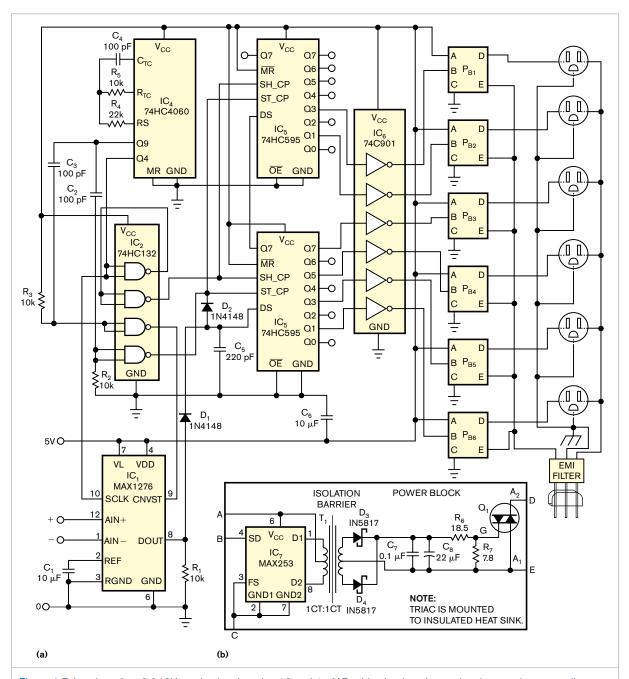

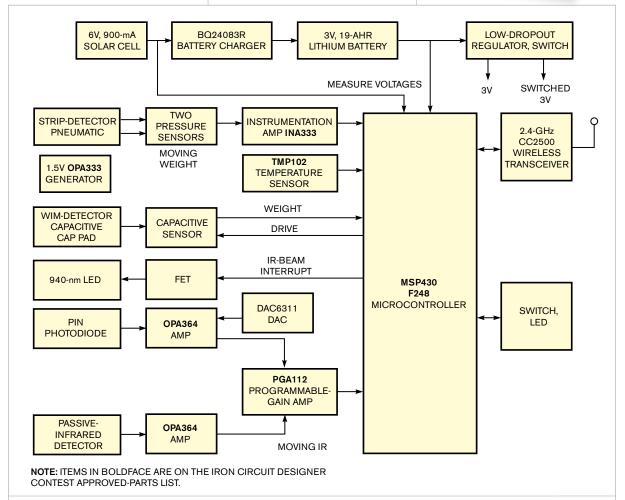

Solar-powered sensor controls traffic

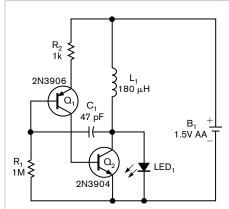

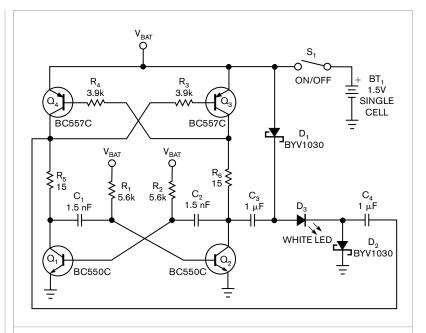

Self-oscillating H bridge lights white LED from one cell

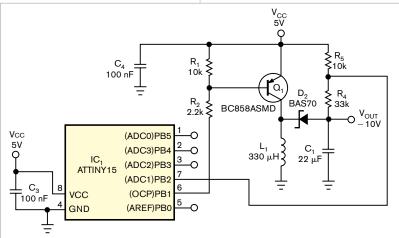

Low-cost LCD-bias generator uses main microcontroller as control IC

#### December 2009

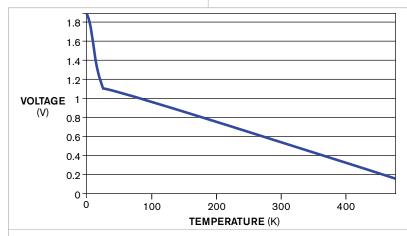

Precision tilt/fall detector consumes less than 1.5 mW

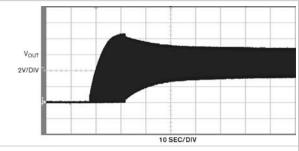

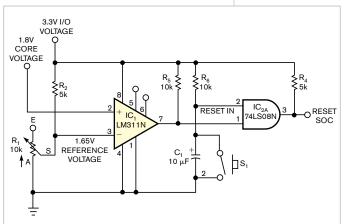

Reset an SOC only when power is ready

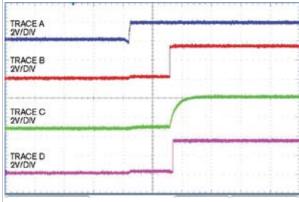

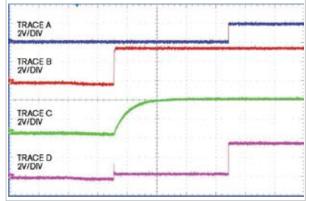

Circuit provides simpler power-supply-sequence testing

Inexpensive power switch includes submicrosecond circuit breaker

Create a DAC from a microcontroller's ADC

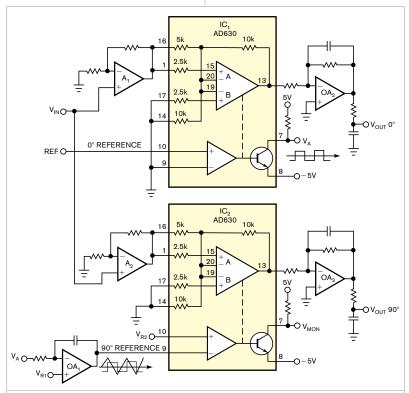

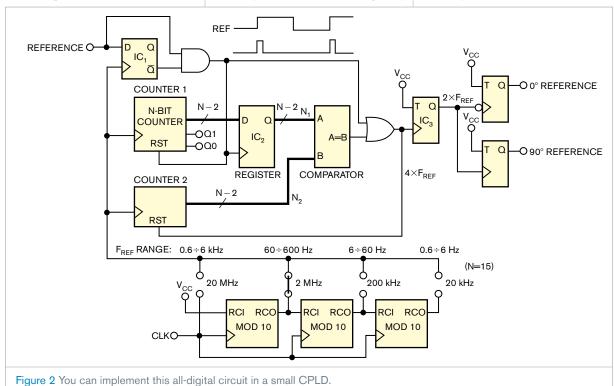

Compact, four-quadrant lock-in amplifier generates two analog outputs

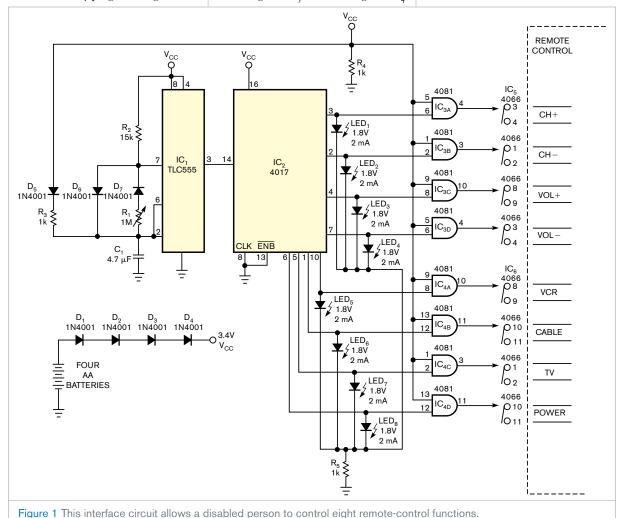

Eight-function remote uses one button, no microcode

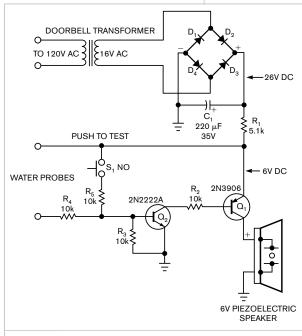

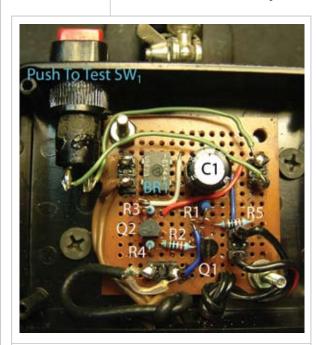

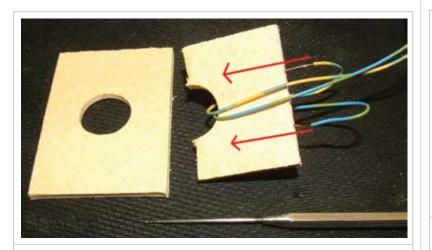

Doorbell transformer acts as simple water-leak detector

Inverted regulator increases choice and reduces complexity

Debug a microcontroller-to-FPGA interface from the FPGA side

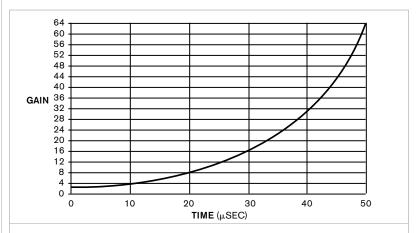

## Digitally programmable-gain amplifier uses divergent-exponential curve

W Stephen Woodward, Chapel Hill, NC

DPGAs (digitally programmable-gain amplifiers) are handy signal-processing components whenever ADCs must acquire signals with a wide dynamic range. Without the

ability to accommodate input-signal amplitude to match and efficiently use ADC span, low-level inputs may not be digitized with adequate resolution, and high-level inputs may overrange

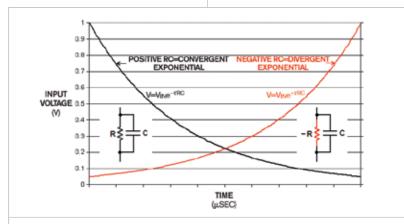

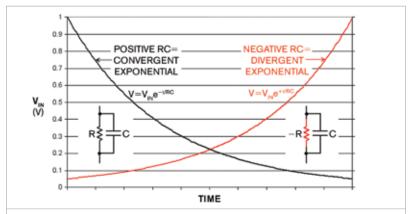

Figure 1 The behavior of the RC topology is still simple when you replace R with an active circuit that synthesizes a negative resistance.

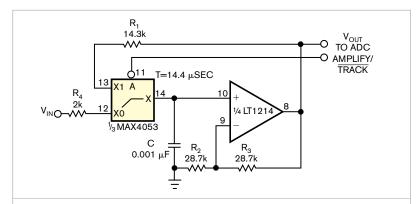

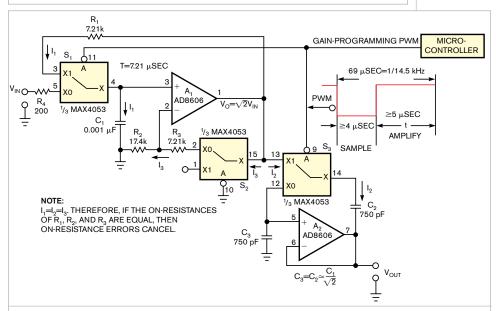

Figure 2 The divergent-exponential and negative time constants are the core concepts of the DENT (divergent-exponential-negative-time-constant) DPGA topology.

#### DIs Inside

- 50 Circuit indicates ac-mains-fuse failure

- 52 Isolation MOSFET-driver IC gets improved power efficiency at lighter loads

- 54 Synthesize variable resistors with hyperbolic taper

- ►To see all of EDN's Design Ideas, visit www.edn.com/design ideas.

the ADC and be lost altogether.

Currently available DPGA designs typically incorporate a multiplying DAC into an op-amp-feedback loop, so that the input code to the multiplying DAC sets the amplifier's closedloop gain. Several available monolithic DPGAs, such as Linear Technology's (www.linear.com) LTC6910 and National Semiconductor's (www.national. com) LMP8100, employ this topology. But the DPGA's digital-gain-control bits are sometimes inconvenient to provide, and these devices' output span may be inadequate, for example, to interface to  $\pm 10V$  ADC-input spans. Also, the resolution of these devices' available gain settings is usually coarse—for example, 2-to-1 per gain step—and their power consumption is sometimes large. In contrast, this Design Idea describes a new DPGA that employs the concept of the divergentexponential curve.

No waveform is simpler or more familiar than the e<sup>-t/RC</sup>-convergent exponential—the asymptotic discharge to zero of an elementary RC circuit initially charged to the input voltage,  $V_{IN}$ , in which  $V=V_{IN}/2$  at  $t=T=\log_e(2)RC$ ,  $V_{IN}/4$  at t=2T,

$V_{IN}/8$  at 3T, and so forth. Less familiar, but just as simple, is the behavior of the same RC topology when you replace R with an active circuit that synthesizes a negative resistance (Fig**ure 1**). Replacing R with -R makes the RC time constant negative: -RC and the waveform function yield the divergent exponential,  $V_{IN} \times e^{+t/RC}$ . Then, instead of converging to zero, the waveform diverges theoretically to infinity, and  $V=2V_{IN}$  at t=T,  $4V_{IN}$ at 2T, 8V<sub>IN</sub> at 3T, and so forth. Therefore, no matter how small the input voltage might be, you can amplify it as much as you desire to any voltage by simply waiting the right amount of  $time = t = log_2(V/V_{IN})T$  after starting the negative discharge.

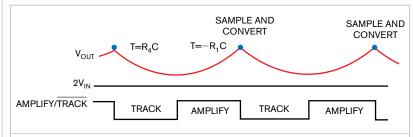

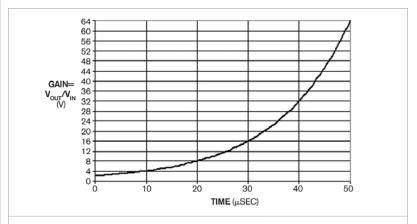

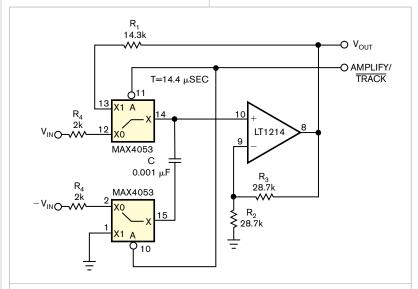

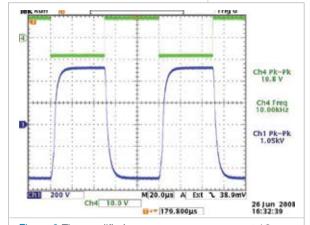

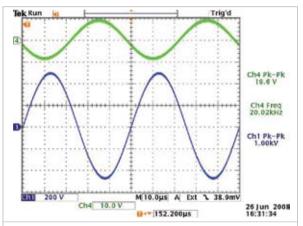

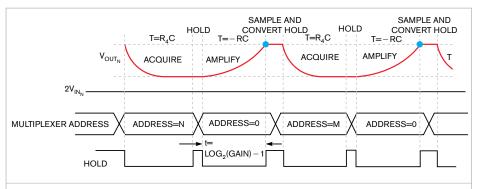

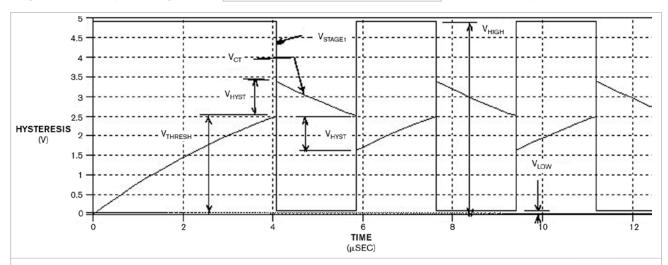

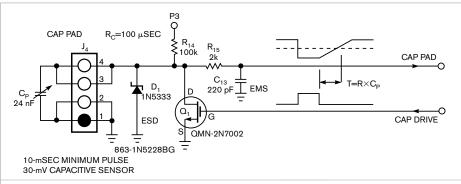

The divergent-exponential and negative time constants are the core concepts of the DENT (divergentexponential-negative-time-constant) DPGA topology (Figure 2). When the amplify/track-control bit goes to logic one, the two-times-noninverting gain of the op-amp follower creates a negative time constant:  $-(R_1 + R_{ON})$  $(C+C_{STRAY}) = -14.4 \mu sec$ , where  $R_{ON}$  is the on-resistance of the CMOS switch, and  $C_{\text{STRAY}}$  is the parasitic capacitance surrounding C (Figure 3). It also creates a diverging exponential:  $V_{OUT}(t) = V_{IN} \times 2^{(t/10 \, \mu sec + 1)}$ . Thus, gain =  $2^{(t/10 \, \mu sec + 1)}$ . The 1- $\mu$ sec timing resolution in the amplify-control bit provides 1.07-to-1=0.6 dB=33 steps/ decade gain-programming resolution. Figure 4 graphs the voltage gain versus the time elapsed since the track/ amplify-logic transition.

Unlike monolithic PGAs, DENT uses discrete components, such as op

Figure 3 When the amplify/track-control bit goes to logic one, the two-times-noninverting gain of the op-amp follower creates a negative time constant.

Figure 4 This graph shows the voltage gain versus the time elapsed since the track/amplify-logic transition.

amps and switches, so it can easily accommodate parameters such as I/O-voltage spans—negative inputs and 10V amplitudes—by choosing appropriate parts and power supplies. The accuracy and repeatability of the timing of exponential generation, ADC sampling, and RC-time-constant stability limit the practical performance of the amplifier in gain-programming accuracy and jitter. In the sample circuit, with T=14.4  $\mu$ sec, 1 nsec of amplify-timing error or jitter equates to

0.007% of gain-programming error. Fortunately, the near ubiquity of programmable timer/counter hardware in popular microcontroller and data-acquisition peripherals usually makes the digital generation of a precisely repeatable amplify/track control an easy matter. On the analog side, possibilities exist for self-calibration algorithms that preserve gain-setting accuracy and relax RC-component-precision requirements, but they lie beyond the scope of this Design Idea. EDN

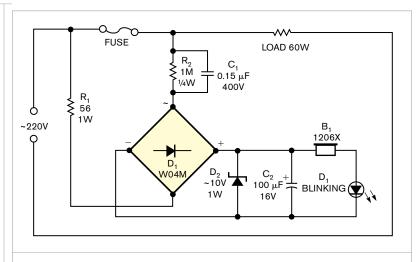

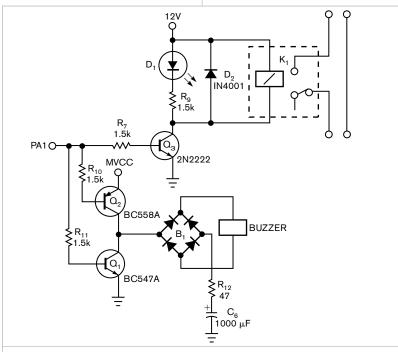

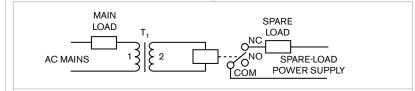

### Circuit indicates ac-mains-fuse failure

By Vladimir Oleynik, Moscow, Russia

Fuses are essential parts of power-distribution systems because they prevent fire or damage to electronic equipment. Fuses have the disadvantage of requiring replacement after every burnout, but they have the advantages of being inexpensive and

widely available. It is difficult to determine the failure time of fuses with ceramic or sand-filled bodies to prevent arcing. This Design Idea presents a simple circuit that solves this problem (Figure 1). It visually and audibly indicates ac-mains-fuse failure; in most

cases, audible indication is sufficient. The circuit works with a range of loads, and you can change its components to adapt to particular ac mains and load specifications.

When a fuse is in good order, the indication circuit is off because the fuse shunts it. When a fuse burns out, the indication circuit starts working. Capacitor C<sub>1</sub> reduces the ac-mains volt-

age, and bridge diode D<sub>1</sub> rectifies the ac voltage. Resistor R<sub>1</sub> limits inrush current when capacitor C<sub>1</sub> is discharged. Zener diode D, and capacitor C, form a dc voltage to operate a buzzer- and blinking-LED network. The blinking LED flashes, and buzzer B<sub>1</sub>, which has a built-in generator, sounds.

Like most other simple circuits, this circuit also has a disadvantage: It is incompatible with some load-power and ac-mains-voltage values. When a fuse burns out, the load stays connected to the ac mains, and the ac voltage divides between the circuit and the load. When the load is highly resistive or the ac-mains voltage is 110V rather than 220V, the circuit's operating voltage may be too low to drive the circuit. In that case, decrease the value of capacitor C<sub>1</sub> to 47 or 68 nF, after which the circuit's resistance rises. With the com-

Figure 1 This circuit visually and audibly indicates ac-mains-fuse failure.

ponent values in Figure 1, the tested circuit operated with resistive loads of 20 to 200W. With higher-power loads,

the circuit operates well because, with higher load-power values, the circuit's load resistance is lower.**EDN**

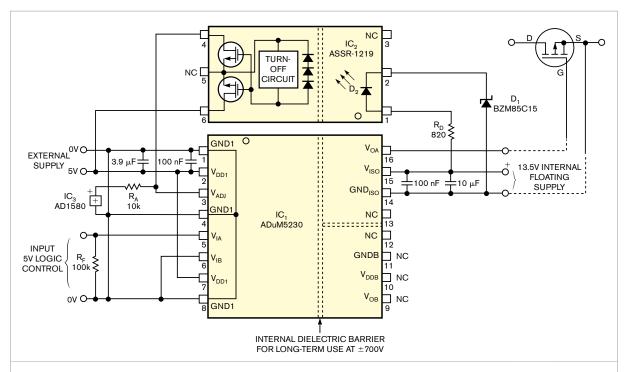

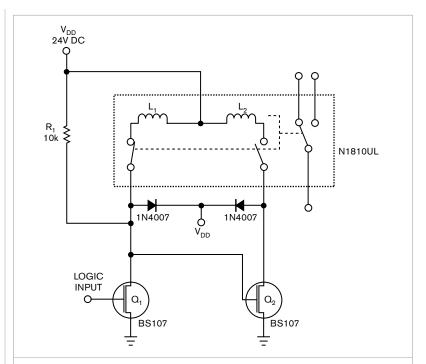

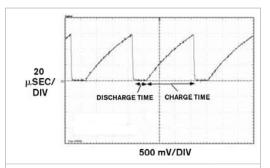

### Isolation MOSFET-driver IC gets improved power efficiency at lighter loads

Marián Štofka, Slovak University of Technology, Bratislava, Slovakia

Many modern power MOSFETs reach low values of on-resistance at 5V even when the gate-to-source voltage is 5V. For heavy-duty power MOSFETS and, especially, IGBTs (insulated-gate bipolar transistors), however, engineers prefer gate-to-source voltages of 12 to 15V because the onresistance of those power switches further decreases at higher gate-to-source voltages. The 17A-rated IRFR024 power MOSFET from International Rectifier (www.irf.com), for example, has an on-resistance of  $0.075\Omega$  (Reference 1). When the gate-to-source voltage is 12V, the device's on-resistance drops to 41% of its value compared to a case of a gate-to-source voltage of 5V. At a switching current of 10A, the device dissipates 6W less when the gateto-source voltage is 12V.

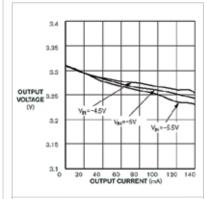

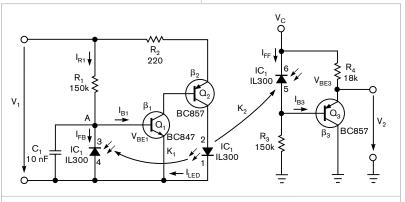

IC, an Analog Devices (www.analog. com) ADuM5230 IC isolation driver, can boost a 5V input to a level that's high enough to drive a MOSFET's onresistance to a low value, minimizing power dissipation (Figure 1). At low switching frequencies, however, the IC's high-side, internal 18V clamping dissipates the energy that the IC draws from the low-side 5V supply (Reference 2).

The ADuM5230's output is, however, unregulated. Fortunately, this IC has an adjustment pin that you can use to control the duty cycle of the device's internal PWM (pulse-width modulator) to reduce the duty cycle from a value of 1 to approximately 0.1. The default duty cycle has the value of 0.55 when the adjust pin is open. The lowest value of duty cycle occurs when connecting the adjust pin to the 5V supply. IC,, an ASSR-1219 advanced photo-MOSFET device from Avago Technologies (www.avagotech.com), controls the voltage at the adjust pin. The photo-MOSFET has 0V saturation voltage between its output terminals. As a classical optocoupler has a bipolar phototransistor, using it as IC, would be less suitable in this case. A bipolar phototransistor has a saturation voltage of 0.4V, and, further, the CTR (current-transfer ratio) of a common optocoupler would decrease significantly when operating close to output saturation. Pulling the voltage at the adjustment pin to the external voltage-supply level comes into account when the high-side output of IC, has light or negligible loading.

At some point,  $V_{ISO}$ , the high-side output voltage of  $IC_1$ , will exceed the value of approximately  $V_z(I_F) + V_{FLED} \sim 13.5 \text{V}$ , where  $V_z(I_F)$  is the voltage of zener diode  $D_1$  at  $I_p$ , the forward current of  $D_2$ , and  $V_{ELED}$  is the minimum forward voltage at D<sub>2</sub>, the LED of IC<sub>2</sub>. IC<sub>1</sub> exceeds this value, current starts to flow through the D2, and the MOSFET at the output of IC, becomes conductive. The manufacturer of IC, designed it for on/off operation and recommends a forward current of at least 0.5 mA (Reference 3).

At signal-level loading of the MOS-FET at the output of IC2, a few tens of microamperes of forward current through the LED cause the photo MOSFET's on-resistance to change

Figure 1 Connecting optical feedback by opto-MOSFET IC, in the power-MOSFET-driver IC, stabilizes the high-side output voltage to 13.5V at values of loading current down to 3.7 mA. The power efficiency of the circuit increases for a loading current of less than 7 mA.

from an almost-infinite value to a value of kilohms. The voltage level at the adjust pin then increases, and the duty factor of both the PWM in IC, decreases. This action establishes an isolated negative-voltage feedback. Thus, the temperatures of both the MOSFET and the LED in IC, have little effect on the properties of the circuit. At lighter loads, the current drain of the 5V supply is much lower than that of IC, with its adjust pin open.

Under test, the default supply current of the unloaded IC, was approximately 94.6 mA. This value decreases to 31.7 mA with the feedback in the circuit.

At heavy loading, the high-side output current of IC<sub>1</sub> rises to approximately 20 mA, and the duty factor rises automatically to a proper value that's higher than at the default supply current. Thus, the output voltage is roughly 13.5V within the range of approximately 3.7 to 22.6 mA. The power efficiency of the circuit is 20% or greater. At an output current of 4.5 mA, the power efficiency is 20.5%, and the power efficiency for IC, is approximately 15%. At a current of 3.7 mA, the circuit reaches 20% efficiency, a value that's considerably higher than the 13% in  $IC_1$  with its adjust pin open.EDN

#### REFERENCES

- "IRFR/U024 HEXFET Power MOSFET," International Rectifier, www.irf.com/product-info/datasheets/ data/irfr024n.pdf.

- "ADuM5230, Isolated Half-Bridge Driver with Integrated High-Side Supply," Analog Devices Inc, 2008, www. analog.com/static/imported-files/ data\_sheets/ADuM5230.pdf.

- "ASSR-1218, ASSR-1219 and ASSR-1228, Form A, Solid State Relay (Photo MOSFET) (60V/0.2A/  $10\Omega$ )," Avago Technologies, July 18, 2007, www.avagotech.com/docs/ AV02-0173EN.

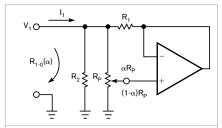

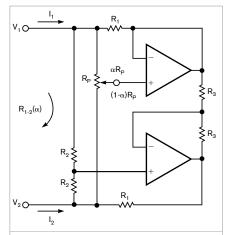

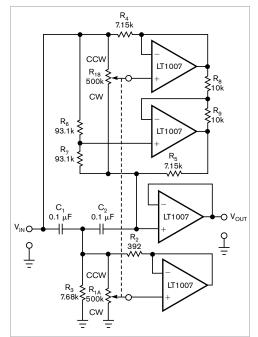

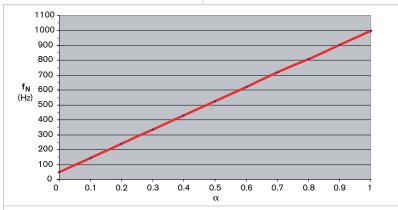

## Synthesize variable resistors with hyperbolic taper

TL Flaig, Clinton, WA

In adjustable, frequency-selective RC networks, the reciprocal of an RC product,  $\omega_{C}=1/RC$ , determines the corner frequencies of the

network. If the adjustable elements are potentiometers with a linear-control characteristic—that is, taper- $R(\alpha) = \alpha R_{D}$ , where  $\alpha$  is the normalized

wiper position,  $0 \le \alpha \le 1$ , and  $R_p$  is the potentiometer's end-to-end resistance, then the corner frequencies are reciprocal functions of the potentiometer's wiper position, and the frequency scale compresses at the high end of the adjustment range. This situation is usually undesirable because it complicates adjustment of the network at the high

Figure 1 This simple circuit synthesizes a grounded variable resistance with a hyperbolic-control characteristic.

Figure 2 You can realize a floating variable resistance, with hyperbolic taper, with this circuit. Note that fixed resistors with the same number are matched pairs.

end. To make the frequency scale linear requires a control element with a hyperbolic taper—that is, something in the form  $R(\alpha) = R_p/(A + \alpha B)$ . Such variable resistances are not generally available from manufacturers, but you can synthesize them using a linear taper potentiometer and a few other components.

Figure 1 shows a simple circuit for producing a ground-referenced variable resistance having the desired hyperbolic-control characteristic. Analysis of this circuit yields the following relationship between the control setting and the resistance from Node 1 to ground:  $R_{1,0}(\alpha) = R_1 R_2 R_p$  $(R_1R_2+R_1R_p+\alpha R_2R_p)0 \leq \alpha \leq 1.$ If you use this resistance in series or in parallel with a capacitor, the resulting corner frequency will be a linear function of  $\alpha$ :  $\omega_C = (R_1 R_2 + R_1 R_p + \alpha R_2 R_p)/$ R<sub>1</sub>R<sub>2</sub>R<sub>2</sub>C. The minimum and maximum values for  $R_{1-0}$  are  $R_{1-OMIN} = R_1 R_2 R_p / (R_1 R_2 + R_1^{1/2} R_p + R_2 R_p)$  and  $R_{1-OMAX} = R_2 R_p / (R_2 + R_1^{1/2} R_p + R_2^{1/2} R_p + R_2^{1/2}$  $R_{\rm p}$ ).

To design this circuit for specific values of  $R_{\text{1-OMIN}}$  and  $R_{\text{1-OMAX}}$ , choose R<sub>p</sub>>R<sub>1-0MAX</sub> and then com- $\begin{array}{c} \text{pute } R_1 = R_{1-0\text{MAX}} R_{1-0\text{MIN}} / (R_{1-0\text{MAX}} - R_{1-0\text{MIN}}) \\ \text{and} \quad R_2 = R_p R_{1-0\text{MAX}} / R_{1 (R_P - R_{1-OMAX}).$

You can extend the basic circuit of Figure 1 to produce a floating variable resistance with hyperbolic taper (Figure 2). The value of the floating resistance between nodes 1 and 2 is  $R_{1-2}(\alpha) = 2R_1R_2R_p$  $(2R_1R_2 + R_1R_p + 2\alpha R_2R_p)0 \le \alpha \le 1$ , and the minimum and maximum values for R<sub>1.2</sub> are R<sub>1.2MIN</sub>= $2R_1R_2R_p$ / ( $2R_1R_2+R_1R_p+2R_2R_p$ ) and R<sub>1.2MAX</sub>=  $2R_{p}R_{p}/(2R_{p}+R_{p})$ . To design the circuit of Figure 2 for specific values of

Figure 3 The basic circuits of figures 1 and 2 have been used in the design of a bridged-T notch filter with a variable notch center frequency and a linear frequency scale.

$R_{1\text{-2MIN}}$  and  $R_{1\text{-2MAX}}$ , choose  $R_p{>}R_{1\text{-2MAX}}$  and then compute  $R_1{=}R_{1\text{-2MAX}}R_{1\text{-2MIN}}/(R_{1\text{-2MAX}}{-}R_{1\text{-2MIN}})$  and  $R_2{=}\frac{1}{2}R_pR_{1\text{-2MAX}}/(R_p{-}R_{1\text{-2MAX}})$ . Note that the value of the R, resistors does not directly affect the value of  $R_{1,2}(\alpha)$ . You should choose resistors that are large enough to not excessively load the op-amp outputs.

Figure 3 illustrates the application of the circuits in figures 1 and 2 to the design of an adjustable bridged-T notch filter with a linear frequency scale. The filter has a notch center frequency that is adjustable from 50 to 1000 Hz and a notch depth of -20 dB. These requirements and the choice of 0.1-µF capacitors for C<sub>1</sub> and  $C_2$  dictate that  $R_{1.0}$  varies from  $3\overline{7}5$  to  $7503\Omega$  and that  $R_{1.2}$  varies from 6752 to  $135,047\Omega$ . (A side benefit of using this technique is that it frees the designer from the restrictions of the limited number of standard end-to-end resistance values that potentiometer manufacturers offer.)

Figure 4 plots the Spice-simulated notch center frequency for the circuit of Figure 3 against the normalized wiper position. The notch center frequency is a linear function of the control position.**EDN**

Figure 4 The Spice-simulated notch center frequency for the circuit of Figure 3 versus the normalized wiper position shows that the notch center frequency is a linear function of the control position.

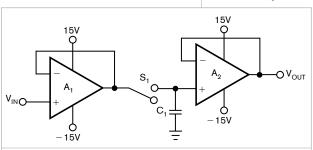

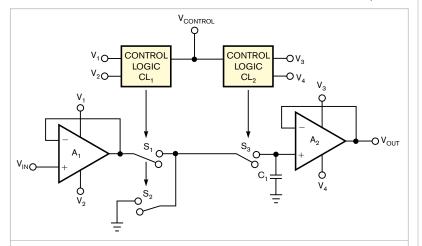

### Increase the range of memorized voltage for a sample-and-hold device

Yakov Velikson, Lexington, MA

Sample-and-hold devices find use in front of ADCs. The basic sample-and-hold circuit comprises two op amps,  $A_1$  and  $A_2$ ; a switch,  $S_1$ ; and a capacitor,  $C_1$  (Figure 1). For many low-power op amps, the values of the input and output voltages can be only  $\pm 10$  to  $\pm 14$ V using a standard  $\pm 15$ V power supply. Enabling these devices

to handle greater voltage can significantly improve the resolution of an ADC.

You can increase the memorized voltage that amplifiers A<sub>1</sub> and A<sub>2</sub> can reach by using a variable power supply (references 1 and 2). This approach places additional voltage requirements on S<sub>1</sub>, however. To continue

> using switches with the same range as the original, you must add two switches and independent control-logic blocks, CL, and CL, for switches  $\hat{S}_1$ ,  $S_2$ , and S, (Figure 2). The

Figure 1 A basic sample-and-hold circuit comprises two op amps, a switch, and a capacitor.

Figure 2 To continue using switches with the same voltage range as that of Figure 1, you must add two switches and two independent control-logic blocks

#### **DIs Inside**

- 48 Inexpensive self-resetting circuit breaker requires few parts

- 54 Sinusoid generator uses dual-output current-controlled conveyors

- 56 Perform timing for microcontrollers without using timers

- ►To see all of EDN's Design Ideas, visit www.edn.com/design ideas.

two parts of the circuit may have independent power supplies. You apply the same variable voltages to amplifiers A, and A, as you do to controllogic blocks CL<sub>1</sub> and CL<sub>2</sub>, respectively. When S<sub>1</sub> and S<sub>3</sub> are closed, S<sub>7</sub> is open, and vice versa.

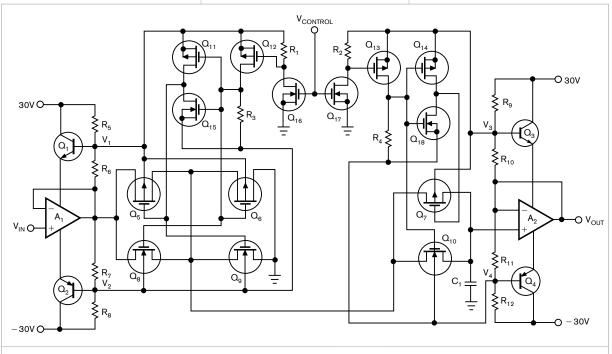

The resulting circuit keeps the voltages connected to the gate and substrate for the MOS transistors of each switch within the desired 30V range (Figure 3). (You derive this value from the sum of absolute-voltage values:  $|V_1|+|V_2|$  and  $|V_3|=|V_4|$ .) Voltages  $V_1$  and  $-V_2$  connect to amplifier A<sub>1</sub>, control-logic block CL<sub>1</sub>, and the substrates of the transistors of switches  $S_1$  and  $S_2$ . Voltages  $V_3$  and  $-V_4$  connect to amplifier A2, control-logic block CL<sub>2</sub>, and the substrates of the transistors of switch  $S_3$ .

You create the changing voltages of  $V_1$  and  $V_2$  using resistor dividers R<sub>5</sub> and R<sub>6</sub> and R<sub>7</sub> and R<sub>8</sub>, which connect to the 30 and the -30V power supplies and the output of amplifier follower A<sub>1</sub> (Figure 3). Transistors  $Q_1$  and  $Q_2$  create the change to the power supply of amplifier A<sub>1</sub>. Volt-

ages V<sub>1</sub> and V<sub>2</sub> also supply power to control-logic block CL<sub>1</sub> and the substrates of the transistors of switches S<sub>1</sub> and S<sub>2</sub>. CL<sub>1</sub> comprises transistors Q<sub>11</sub>,  $Q_{12}$ ,  $Q_{15}$ , and  $Q_{16}$ . It creates a control signal for gates  $Q_5$  and  $Q_6$  of switch  $S_1$ and the inverse signal for gates  $Q_8$  and  $Q_9$  of  $S_2$ .

Resistor dividers  $R_9$  and  $R_{10}$  and  $R_{11}$ and R<sub>12</sub> connect to the 30 and the -30V power supplies, and the output of amplifier follower A2 creates the

changing voltages V<sub>3</sub> and V<sub>4</sub>. Transistors  $Q_3$  and  $Q_4$  create the change to the power supply of amplifier  $A_2$ . Voltages V<sub>3</sub> and V<sub>4</sub> also supply power to control-logic block CL, and the substrates of the transistors of switch  $S_3$ .  $CL_2$  is made up of transistors  $Q_{13}$ ,  $Q_{14}$ ,  $Q_{17}$ , and  $Q_{18}$ . It creates a control signal for gates  $Q_7$  and  $Q_{10}$  of switch  $S_3$ . Transistors  $Q_5$  through  $Q_{10}$  and  $Q_{11}$  through  $Q_{18}$  of  $CL_1$  and  $CL_2$ , respectively, are complementary pairs of MOS logic transistors.**EDN**

#### REFERENCES

- Velikson, Yakov, "Controlled power supply increases op amp's outputvoltage range," EDN, March 15, 2007, pg 72, www.edn.com/article/ CA6421438.

- Velikson, Yakov, and Igor Ribkin, "Analog switch, 1385288," Bulletin of Izobreteny (Copyrights and Patents), No. 12, 1988.

Figure 3 You can create the changing voltages of V<sub>1</sub> and V<sub>2</sub> using resistor dividers R<sub>5</sub> and R<sub>6</sub> and R<sub>7</sub> and R<sub>8</sub>.

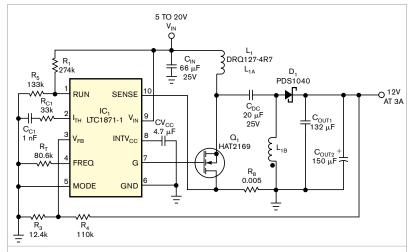

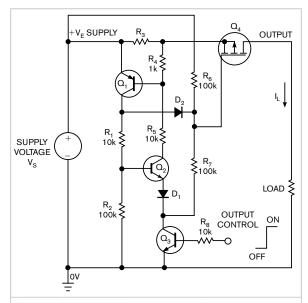

### Inexpensive self-resetting circuit breaker requires few parts

Anthony H Smith, Scitech, Bedfordshire, England

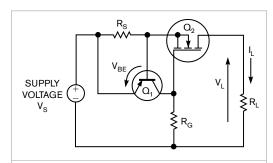

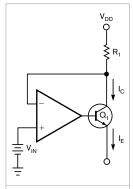

Most readers are familiar with the current-limiting circuit in Figure 1, in which the load current,  $I_L$ , is limited to a value of  $I_L \approx V_{BE}/R_S$ , where V<sub>BE</sub> is the base-to-emitter voltage and R<sub>s</sub> is the sense resistance. Under normal conditions, in which the base-to-emitter voltage is too small to bias Q<sub>1</sub> on, P-channel MOSFET Q<sub>2</sub>'s gate resistor, R<sub>Q</sub>, biases Q<sub>2</sub> fully on, and

only the load resistance,  $R_1$ , and the load voltage, V<sub>1</sub>, determine the load current. However, if the load current increases to a point at which the baseto-emitter voltage is approximately 0.7V, Q<sub>1</sub> starts to conduct and reduces  $Q_{1}$ 's gate-to-source voltage,  $V_{GS}$ , to a level that holds the load current roughly constant at a value you derive from  $I_{LMAXIMUM} \approx 0.7 \text{V/R}_{\text{S}}$ .

This linear current limiter is effective for applications in which the maximum load current, the supply voltage, or both are relatively small. However, the power that the circuit's pass transistor,  $Q_{2}$ , dissipates limits the circuit's applicability. For example, if the maximum load current is 200 mA and the supply voltage,  $V_{\scriptscriptstyle S}$ , is 24V, a short circuit across the load would dissipate almost 5W into Q, Q, must handle this power with adequate margin, and additional heat-sinking may be necessary to keep its junction temperature at a safe level. Using larger values of

maximum load current, supply voltage, or both exacerbates this problem. In many applications, the cost, size, and weight of the components necessary to handle the short-circuit power dissipation may be prohibitive.

However, by adding a few inexpensive components, you can adapt the circuit to provide effective current limiting with none of the power-dissipation headaches. The resulting circuit functions as a self-resetting circuit breaker

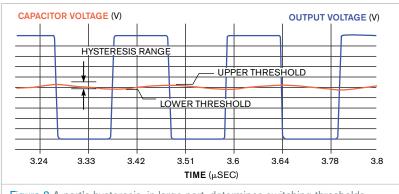

(**Figure 2a**). Again,  $Q_1$  and  $R_S$  provide a current-monitoring function in which the sense voltage  $V_{\text{SENSE}}$ =  $I_1 \times R_s$ . In this circuit, however,  $Q_7$  is either fully on or fully off and never biases into its linear region. Because Q<sub>1</sub>'s base current is normally small, the voltage drop across base resistor R<sub>B</sub> is also small, such that the base-to-emitter voltage is approximately equal to the sense voltage.

To understand how the circuit works,

Figure 1 A conventional two-transistor current limiter prevents excessive current from reaching the load.

assume that the load current is initially low and the base-to-emitter voltage is less than 0.7V. Under these conditions,  $Q_1$  is off and timing capacitor  $C_1$ remains uncharged such that  $V_{IN}$ , the voltage at the input of Schmitt inverter IC<sub>1</sub>, is 0V. Thus, IC<sub>1</sub>'s output is approximately 5V, biasing Q<sub>3</sub> on, which in turn provides gate bias for Q, through R<sub>4</sub>, allowing current to flow from the supply voltage into the load through the sense resistor and Q,'s on-resistance.

SENSE R<sub>3</sub>

10k SUPPLY 10k VOLTAGE 2N7002 100 nF (a)  $t_{ON}$ toff (b)

Figure 2 Adding a few components turns the current-limiting circuit into a pulser that reduces heat in the pass transistor, Q<sub>o</sub> (a). The circuit's waveforms show the relationship between the input voltage and the load voltage (b).

If a fault now causes the load current to increase to a level at which the base-to-emitter voltage is approximately 0.7V, Q<sub>1</sub> turns on and its collector current rapidly charges C<sub>1</sub>. The input voltage now quickly rises toward the Schmitt inverter's upper threshold voltage,  $V_{TU}$ , at which point IC<sub>1</sub>'s output goes low, turning off  $Q_3$  and  $Q_2$ . The load current now falls to 0Å and the base-to-emitter voltage falls to 0V, thereby causing  $Q_1$  to turn off.  $C_1$  now begins to discharge through R<sub>1</sub>

and R<sub>2</sub>, and the input voltage slowly falls toward the Schmitt inverter's lower threshold voltage,  $V_{TL}$ . At this point, IC<sub>1</sub>'s output again goes high, Q<sub>3</sub> and Q, turn on, the circuit breaker resets itself, and the process repeats until vou remove the fault.

The circuit's waveforms show the relationship between the input voltage and the load voltage (Figure 2b). Because load current flows into Q, only during the on-time, the average power it dissipates is directly proportional to the duty cycle:  $P_{AVG} \propto t_{ON}$  $(t_{ON} + t_{OFF})$ , where  $P_{AVG}$  is the average power in watts,  $t_{ON}$  is the on-time, and  $t_{\text{OFF}}$  is the off-time. Provided that  $C_1$ ,  $R_1$ , and  $R_2$  set a large enough time constant, the off-time will normally be much greater than the on-time, and the resulting power that Q, dissipates will be low. Like the linearcurrent limiter, the sense resistor sets the circuit breaker's current limit:

$\begin{array}{l} {\rm I_{LMAXIMUM}}{\approx}0.7{\rm V/R_{_S}}\,({\rm A}). \\ {\rm R_{_1}}\,{\rm and}\,\,{\rm R_{_2}}\,{\rm form}\,\,{\rm a}\,\,{\rm potential}\,\,{\rm divider} \end{array}$ that ensures that the input voltage can never exceed IC1's maximum input voltage. Select values such that the input voltage is 5V or less when  $Q_1$  is fully on, where the voltage of C<sub>1</sub> is roughly equal to the supply voltage. Also, choose values that are large enough to provide a large time constant without requiring an excessively large value of C<sub>1</sub>. The selection of transistor Q<sub>1</sub> isn't critical, but you should select a device with good current gain and make sure that its maximum collector-to-emitter voltage is greater than the supply voltage. When choosing a P-channel MOSFET for Q2, re-

member that it must withstand the full supply voltage when you bias it off, so make sure that the maximum drain-tosource voltage is greater than the supply voltage. When choosing a value for the sense resistor, ensure that the baseto-emitter voltage is less than 0.5V at the maximum normal value of the load current.

Loads such as filament bulbs, ca-

pacitive loads, and motors that exhibit a large inrush current can cause the circuit breaker to trip on powerup. You can avoid these problems by adding capacitor  $C_X$ , diode  $D_X$ , and resistor  $R_x$ . On power-up,  $C_x$  is initially uncharged and pulls the input voltage toward 0V through  $D_x$ . This action prevents the circuit breaker from tripping until the inrush current subsides.  $C_X$  and  $R_X$  determine a delay, after which the voltage on C<sub>X</sub> eventually rises to the supply voltage, D<sub>x</sub> becomes reverse biased, and the circuit breaker is then free to respond to overcurrent faults. Be prepared to experiment with the values of C<sub>v</sub> and  $R_v$  to get the right delay time. Values of 10  $\mu$ F and 1 M $\Omega$ , respectively, are good starting points.**EDN**

### Sinusoid generator uses dual-output current-controlled conveyors

Abhirup Lahiri, Netaji Subhas Institute of Technology, New Delhi, India

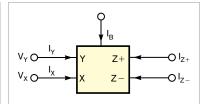

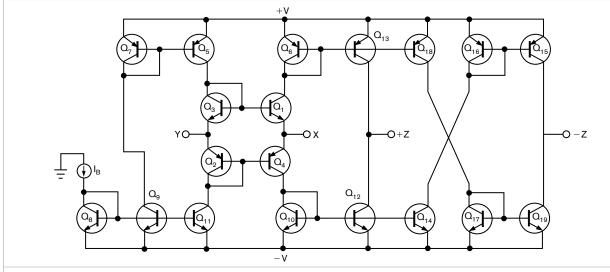

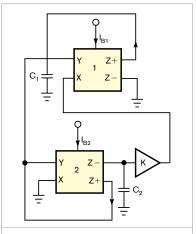

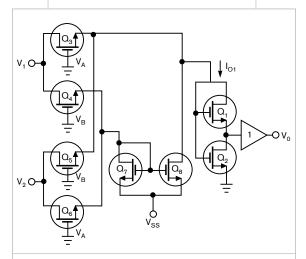

Second-generation current conveyors feature wide signal bandwidth, linearity, wide dynamic range, simple circuitry, and low power consumption. Hence, designers employ several implementations of current mode in these devices for realizing various functions. A previous Design Idea introduced a second-generation dualoutput current-controlled conveyor to create oscillators (Reference 1). Unfortunately, these circuits aren't available as ICs, but you build them from discrete components. Figure 1 illustrates an active building block of such a circuit, which the following equations characterize:  $I_y=0$ ,  $V_x=V_y+I_xR_x$ ,

$I_{z_{+}}=I_{x}$ , and  $I_{z_{-}}=-I_{x}$ . You can express the parasitic resistance at terminal X as  $R_X = V_T/2I_B$ , where  $V_T$  is the thermal voltage and I<sub>B</sub> is the bias current of the conveyor that is tunable over several decades. Figure 2 shows the bipolar implementation of the circuit.

The circuit provides an extra degree of freedom in the sense that the control over the frequency of oscillation can be through both current and voltage. The circuit in the previous Design Idea provides various advantages, it this new circuit not only retains all those essential advantages, it also provides an extra feature of voltage controllability of frequency of oscillation.

Figure 1 Second-generation current conveyors feature wide signal bandwidth, linearity, wide dynamic range, simple circuitry, and low power consumption.

Additionally, you can control the condition of oscillation using the conveyors' bias currents.

Figure 3 shows the proposed sinusoid-oscillator circuit. You can obtain the characteristic equation for the circuits as follows: S<sub>2</sub>C<sub>1</sub>C<sub>2</sub>  $R_{x_1}R_{x_2} + SC_2R_{x_2} - SC_2R_{x_1} + K = 0$ ,

Figure 2 A current-controlled circuit uses no internal resistors or capacitors.

where K is the voltage multiplier. Satisfying Barkhausen's criteria—that the loop gain is unity or greater and that the feedback signal arriving back at the input is phase-shifted 360°—the required condition for oscillation is  $R_{x_1}=R_{x_2}$ , and the frequency of oscillation is  $\hat{f} = 1/2\pi\sqrt{k/(C_1C_2R_{x_1}R_{x_2})}$ .

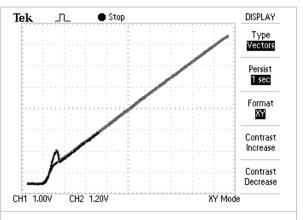

Clearly, you can use the gain buffer to vary the frequency of oscillation, which is the area in which this circuit differs from the earlier Design Idea. You can use both current and voltage to control the voltage multiplier. The circuit lets you vary the voltage multiplier by adjusting bias currents  $I_{B3}$  or  $I_{B4}$  (Figure 4). For voltage control over K, you can use another circuit simply by using a noninverting op amp and replacing the resistors with MOSFETs working in that triode region. That approach simulates voltage-controlled resistors.

The circuit in Figure 2 underwent testing with a PR100N PNP transistor and an NPN NP100N transistor of the bipolar arrays ALA400 and a dc supply of  $\pm 3V$  (Reference 2).

The circuit requires only two current-controlled conveyors, two grounded capacitors, and a voltage multiplier; it requires no floating capacitors and no external resistors, which makes the circuit's power consumption lower than that of RC oscillators. For a conventional bipolar-transconductance operational amplifier, the transconductance,  $g_m$ , is  $I_B/2V_T$ . Comparing

Figure 3 This configuration creates an oscillator from two current-controlled conveyor circuits.

this figure with the equivalent value of I<sub>B</sub>, the transconductance of the bipolar-transconductance op amp is four times less than that of a dual-output current-controlled conveyor. Thus, the power consumption of the current-controlled-conveyor-based circuit is about four times less per active device than that of the op-amp-based circuit. The sensitivity study shows that  $S^{\omega C}_{K;RX1;RX2;C1;C2}$  = -1/2;  $\omega c$  sensitivities are hence less than unity, which is an attractive feature of this circuit. Remember that creating an accurate oscillator model requires modeling equations to be nonlinear, and meeting the Barkhausen criteria is a necessary

Figure 4 This circuit lets you vary the voltage multiplier by adjusting bias currents I Ray

condition for oscillation. Oscillator circuits may latch up and never oscillate even if you satisfy the Barkhausen criteria.EDN

#### REFERENCES

- Lahiri, Abhirup, "Oscillator uses dual-output current-controlled conveyors," EDN, Nov 13, 2008, pg 62, www.edn.com/article/CA6611645.

- 2 Frey, DR, "Log-domain filtering: an approach to current-mode filtering," Circuits, Devices and Systems, IEE Proceedings G, 1993, Volume 140, pg 406, http://ieeexplore.ieee.org/ Xplore/login.jsp?url=/iel1/2211/ 6397/00250002.pdf?arnumber= 250002.

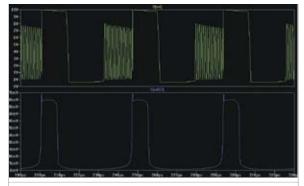

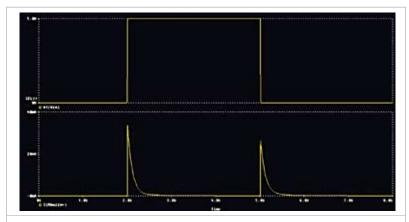

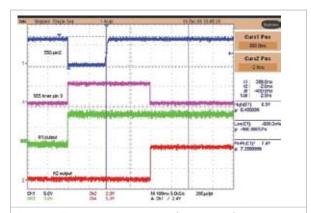

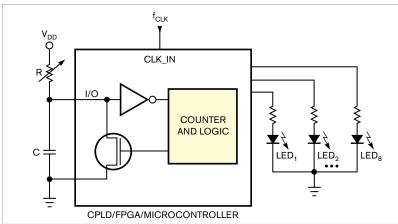

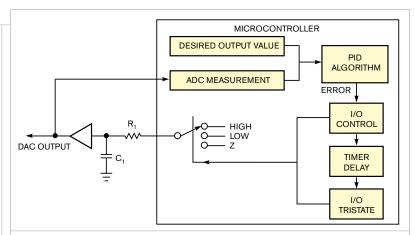

### Perform timing for microcontrollers without using timers

Ganeshkumar Krishnamoorthy, NTERA Ltd, Dublin, Ireland

Microcontrollers now find use in every walk of life. Their peripherals vary from the general-purpose I/Os to the USB interface, making them versatile for a range of products. Timing is one key part of a typical microcontroller application. Low-cost microcontrollers have one or two built-in timers and often also have a watchdog timer.

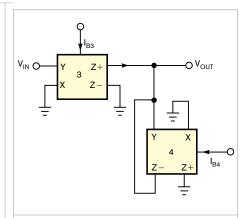

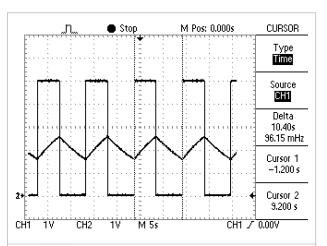

Figure 1 The RC filter along with I/O 's interrupt-onchange feature provides a simple and cost-effective approach for a variety of time-scale measurements from microseconds to minutes.

Sometimes, the design requires more timers without a significant cost increase. Software timers are not suitable for time-critical application because the controller is fully occupied. The

> circuit in this Design Idea uses the I/O "interrupt-on-change" feature that is common in most microcontrollers to implement a medium-precision, long-period timer with low additional

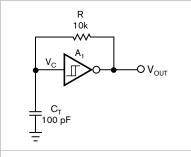

> The circuit in **Figure 1** uses I/O<sub>1</sub>, a typical I/O pin, to drive an RC filter. The circuit feeds the output of the RC filter to a Schmitt-trigger inverter whose

output goes back to I/O<sub>2</sub>, which has the interrupton-change feature. After power-up, I/O<sub>1</sub> is low and the output of the Schmitttrigger inverter is high. After initialization, I/O<sub>1</sub> goes high. Capacitor C charges up with the time constant R<sub>1</sub>C<sub>1</sub>. Once it reaches logic-high voltage, the output of the Schmitttrigger inverter goes low and triggers an interrupt on I/O<sub>2</sub>. In the ISR (interrupt-service routine), a counter increments, driving I/O<sub>1</sub> low. Now, C<sub>1</sub> discharges through R<sub>1</sub>. The voltage reaches logic low,

again triggering an interrupt. As the cycle repeats, the value in the counter indicates time=counter $\times R_1C_1$ . The Schmitt-trigger inverter serves as a debouncer.

Listing 1, which is available in the Web version of this Design Idea at

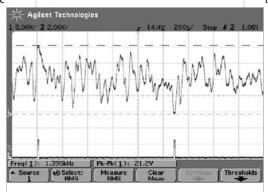

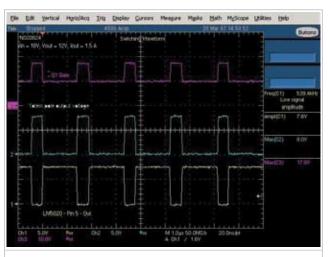

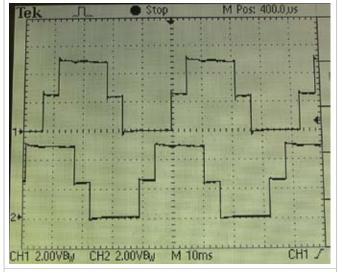

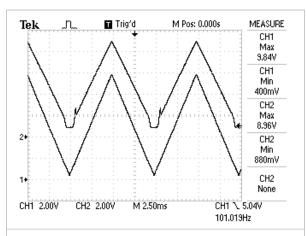

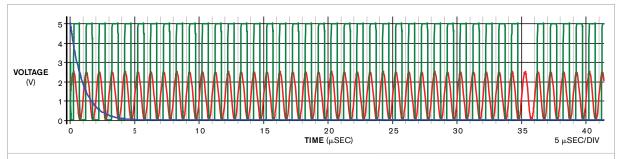

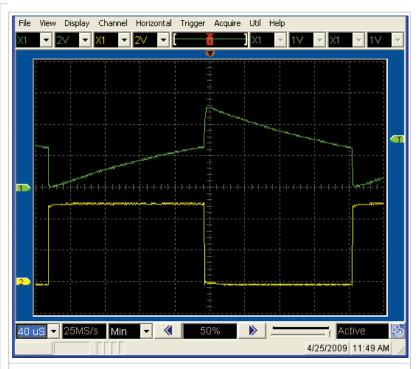

Figure 2 Channel 1 shows I/O,'s waveform, and Channel 2 shows the capacitor's charging/discharging waveform. The time period of the waveform is 10.4 sec.

www.edn.com/090122dia, includes the software routine for the ATMEGA64 microcontroller from Atmel (www. atmel.com). In the listing, Port D, Pin 5 plays the role of I/O<sub>1</sub> and Pin 3, whose alternate function is INT3, plays the role of I/O, in **Figure 1**. The trigger-edge interrupt in this case changes from falling-rising-falling edge in a cycle. Most microcontrollers don't require this feature because any logic change will trigger an interrupt. Figure 2 shows the timing waveform of the circuit with the ATMEGA64 and the 74HC14.

The circuit's advantages are its low cost, a microcontroller-clock-independent time period, and the ability to achieve time periods of minutes to hours by tuning resistance and capacitance. For example, with a resistance of 10 M $\Omega$ , a capacitance of 10 µF, and a 16-bit

register as a counter, you can achieve a maximum count of 75.85 days.EDN

#### **ACKNOWLEDGMENT**

This work is part of a system design in a project funded by the European Union under the Marie Curie Project.

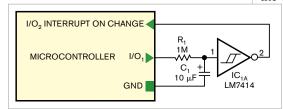

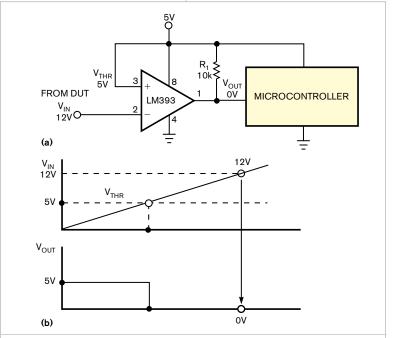

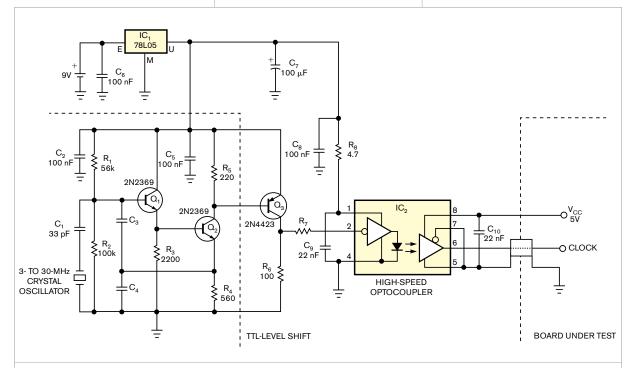

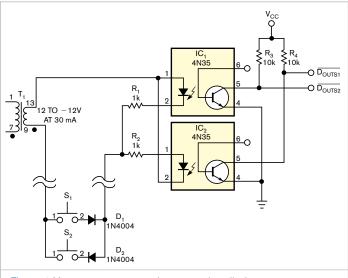

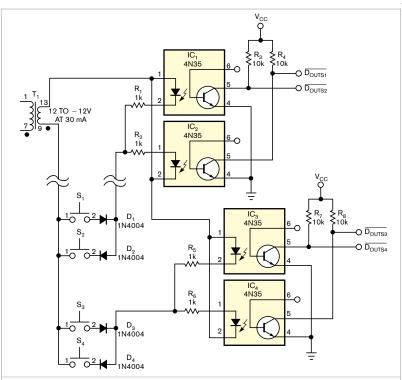

### Convert signals to proper logic levels

Abel Raynus, Armatron International Inc, Malden, MA

When designing a test station incorporating a microcontroller, you often face voltages in the test that exceed the maximum input level permitted for the microcontroller. For example, if a microcontroller uses a 5V power supply, then the maximum input signal should also be 5V. When a test voltage exceeds 5V, you might think to reduce the voltage with a voltage divider. A voltage divider can influence the DUT (device under test), however. So, a signal conditioner needs high input impedance. Also, the signal conditioner's output signals should match the logic levels of the microcontroller despite some fluctuation of the measured signal. It allows you to use the regular microcontrollerinput pins instead of ADC ones.

Engineers often use a noninverting op amp to bring signal voltages in line. However, most op amps have differential-input-voltage ranges matching their power-supply voltages. Thus, you need one more power-supply voltage with a higher voltage and several extra resistors to lower the op amp's

FROM DUT MICROCONTROLLER

Figure 1 You can use a small-signal MOSFET to provide overvoltage-signal conditioning

output to the microcontroller level. Moreover, the output will follow the measured input-signal variations, so it needs analog-to-digital conversion in the microcontroller.

A better approach is to use a smallsignal MOSFET in the voltage-repeater configuration (Figure 1). You can use the BS107A from On Semiconductor (www.onsemi.com) for this task. You can consider the gate-tosource area of the MOSFET as a capacitor with a value of approximately 60 pF. To discharge it in the absence of the DUT, connect a resistor of ap-

#### **DIs Inside**

- 44 DDR-differential-clock source on SOC drives two DDR-memory chips

- 48 Flying capacitor and negative time constant make digitally programmable-gain instrumentation amplifier

- 50 MOSFET prevents battery damage

- 51 Voltage doubler improves accuracy

- ►To see all of EDN's Design Ideas, visit www.edn.com/design ideas.

Figure 2 Another approach to signal conditioning is to use dual- or quadvoltage comparators (a). The 5V power-supply voltage acts as the positivethreshold voltage. The output is 5V for input signals lower than this level. If the input signal exceeds 5V, the output voltage drops to 0V (b).

proximately 1 M $\Omega$  between the gate and ground. Also, the input voltage should be more than the MOSFET's gate-threshold voltage,  $V_{THR}$ , of 3V dc but less than the maximum rated gateto-source voltage,  $V_{GS}$ , of 20V dc. In this figure, the output voltage never exceeds the power-supply voltage, and variations of the input voltage have no effect on output as long as they happen in the saturation region. A drawback of this approach is that you must use as many transistors as the number of testpoints in the DUT.

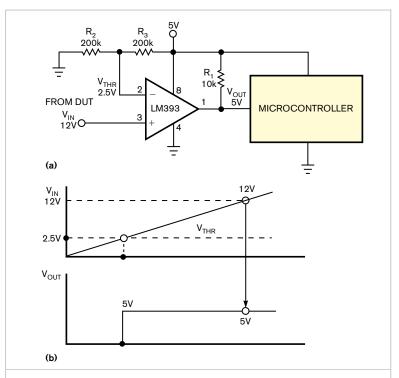

Another good option is to use any dual- or quad-voltage comparator. You can use an LM393 from National Semiconductor (www.national.com) because it's inexpensive and widely available. Figure 2 shows a simple configuration with few components. The 5V power-supply voltage acts as the positive-threshold voltage. The output is 5V for input signals lower than this level. If the input signal exceeds 5V, the output voltage drops to 0V. Resistor R, connects an open collector of the LM393 to the supply voltage.

Sometimes, a zero-output signal is undesirable. A missing power-supply voltage, a bad solder joint, or a broken wire in the test fixture could cause this zero-output signal. Use a logic high level when the signal under test is present and logic low when it's absent. At first glance, it seems that just

Figure 3 Use the voltage divider comprising R<sub>2</sub> and R<sub>3</sub> for the threshold voltage.

switching the comparator pins of the input and the threshold voltages provides an acceptable approach. However, that assumption is invalid because the positive input voltage may exceed the power-supply level only as long as the other voltage remains within the common-mode range. The upper limit of common-mode input voltage for the LM393 is 1.5V less than the powersupply voltage, or 3.5V. Thus, you should use the voltage divider comprising R, and R, for the threshold voltage (Figure 3).EDN

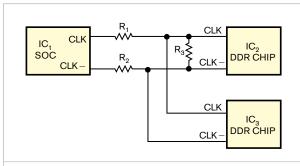

### DDR-differential-clock source on SOC drives two DDR-memory chips

Goh Ban Hok, Infineon Technologies, Singapore

Many system engineers assume that a differential-clock source should drive just one chip. If a system design requires driving two DDR-memory chips, however, the design would inevitably need a differential-clock buffer. This Design Idea describes a circuit that drives two DDR chips without a clock-source buffer yet does not sacrifice much of the signal integrity.

The cost-saving nature of an SOC

(system-on-chip) design dictates the need for fewer pins. Such designs typically have only one pair of differential signals available for external-memorychip connection. When the system design requires more than one DDR chip, designers typically use a clock buffer.

Figure 1 shows an SOC with an embedded DDR controller, which connects the SOC's differential clock to two DDR-memory chips. Differential signals CLK and CLK- from SOC chip IC, connect to series resistors R, and R<sub>2</sub>, respectively. The differential traces then connect to DDR-memory chips IC, and IC, with a  $120\Omega$  termination resistor near IC,.

Figure 2 shows the equivalent PCB (printed-circuit-board) layout. The PCB comprises a four-layer FR4 material with a ground plane under differential lines CLK and CLK-. The CLK and CLK- signals are routed close to each other and pass through series resistors R<sub>1</sub> and R<sub>2</sub>, which are also placed close to each other, to provide proper termination. The closely spaced differential signals connect to

Figure 1 This circuit for an SOC-differential-clock source drives two DDR chips.

Figure 2 The bare PCB shows the differential-signal traces from the SOC to IC, and ICo.

IC, with the  $120\Omega$  termination resistor, R<sub>3</sub>. The bottom-layer traces are necessary to connect the differential signals to IC<sub>3</sub>. The total length of the differential pair is approximately 2.5 in. from the SOC chip to the DDR chips.

The SOC provides DDR differential clocking. With various values for  $R_1$ ,  $R_2$ , and R<sub>3</sub>, the best results occur when R<sub>1</sub> and  $R_2$  are  $\Omega$  and  $R_3$  is unconnected. Figures 3 through 7, which are available with the Web version of this Design Idea at www.edn.com/090205dia, show various waveforms for the signals.EDN

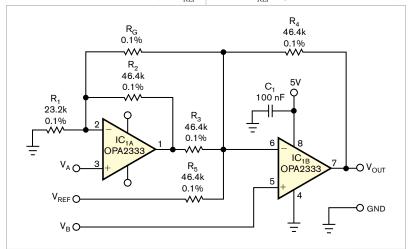

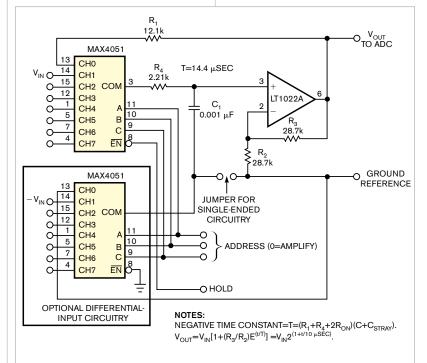

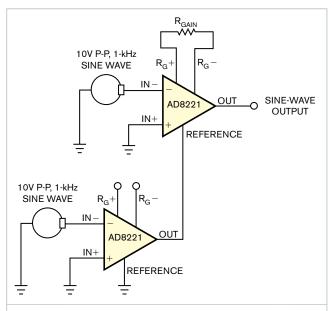

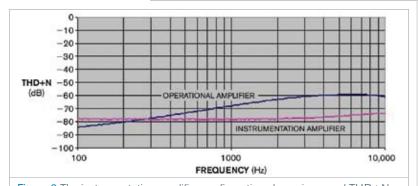

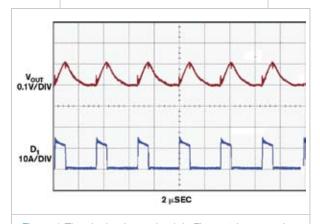

### Flying capacitor and negative time constant make digitally programmablegain instrumentation amplifier

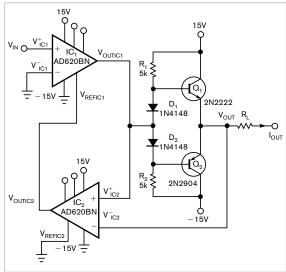

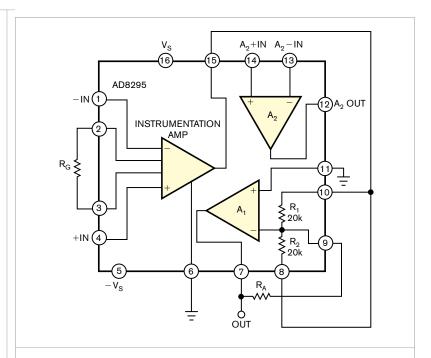

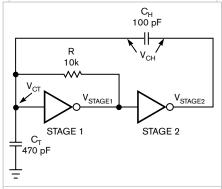

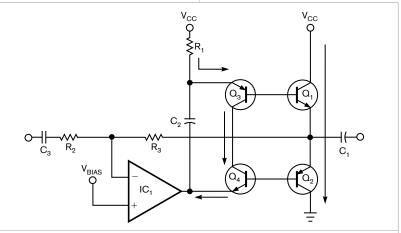

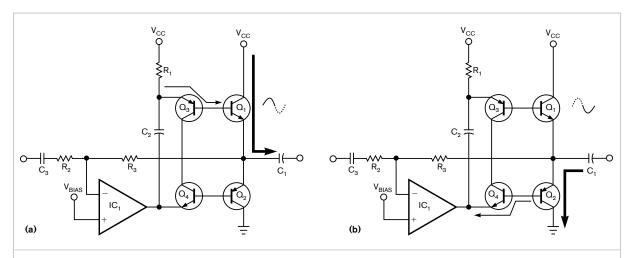

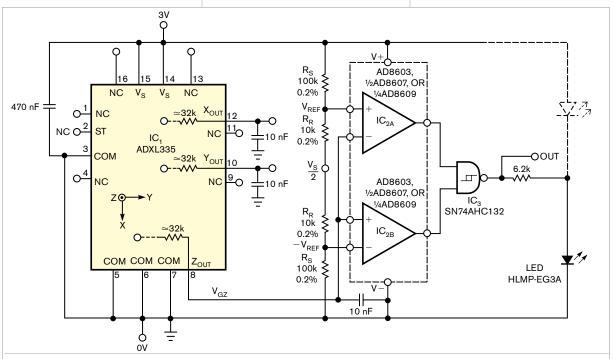

W Stephen Woodward, Chapel Hill, NC

Numerous and evil are the forces of darkness that conspire to frustrate accurate analog-to-digital conversion of wide-dynamic-range analog signals. Among these gremlins lurk common-mode-voltage noise and signal amplitudes too variable to fully use ADC-input span and conversion resolution. Proven charms against common-mode noise are differential inputs, and you can exorcise variable signal amplitudes by implementing digitally programmable gain. DPGIAs (digitally programmable-gain instrumentation amplifiers) combine both useful features (Figure 1).

Microcircuit—even monolithic— DPGIAs, such as the Linear Technology (www.linear.com) LTC6915, are available. But this Design Idea describes a DDENT (differential-divergent-exponential-negative-time-constant) DPGIA employing the concepts of the "flying"-capacitor differential input and the DDENT curve, which provide an interesting alternative.

You control DDENT operation with the amplify/track-bit mode. Track mode connects flying-capacitor C to the positive and negative differential-input terminals, which acquire the input voltage,  $\boldsymbol{V}_{\text{IN}}.$  The transition to the amplify mode isolates C from the input and initiates regenerative negative-time-constant exponential amplification of the input voltage. From that point (Reference 1) until the moment when a connected ADC ultimately samples and converts the

Figure 1 The behavior of the RC topology is still simple when you replace the resistors with an active circuit that synthesizes a negative resistance.

output voltage,  $V_{OUT}/V_{IN}$  is a divergent exponential function of time: gain= $2^{(t/10 \, \mu sec+1)}$ .

Building on the assets of that earlier design, this new circuit features CMR (common-mode rejection) that neither resistor-network matching nor the CMR of the op amp limits. Straycapacitance issues impose the only limits, but you can minimize these issues with careful circuit layout. The circuit has rail-to-rail inputs, virtually unlimited programmable gain, and gain-set resolution that only the resolution of the amplify-interval timing limits. The circuit also has settling time 10 to 100 times faster than that of the

THIS NEW CIRCUIT

FEATURES CMR

THAT NEITHER

RESISTOR-NETWORK

MATCHING NOR

THE CMR OF THE

OP AMP LIMITS.

exemplary LTC6915 and ±10V output-amplitude capability—two to four times greater than that of monolithic DPGIAs. Besides the inherent dc ac-

curacy of the op amp you choose, the accuracy and repeatability of the timing of exponential generation, ADC sampling, and RC-time-constant stability are the only limits on the amplifier's signal-processing performance and precision. In the sample circuit, in which  $T=14.4~\mu$ sec, 1 nsec of amplifytiming error or jitter equates to 0.007% of gain-programming error.EDN

#### REFERENCE

■ Woodward, W Stephen, "Digitally programmable-gain amplifier uses divergent-exponential curve," *EDN*, Jan 8, 2009, pg 49, www.edn.com/article/CA6625454.

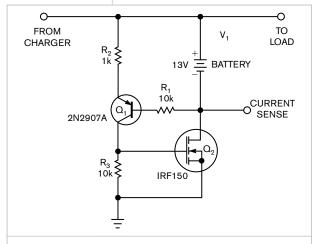

### MOSFET prevents battery damage

Santosh Bhandarkar, Wep Peripherals, Mysore, India

Sealed-lead-acid batteries, which find wide use in powerelectronics products, such as UPS (uninterruptible-power supplies), inverters, and emergency lamps, supply power to the load whenever utility power is unavailable. When you restore utility power, a charger supplies the power to the load and charges the batteries (Figure 1).

You can add a diode to protect a load from current resulting from a reverse-

connected battery. The diode, however, won't protect a reverse-connected battery from the charger circuit. If the charger is on, a potentially dangerous current can flow into a reverse-connected battery. The battery voltage, which normally opposes the charging voltage, now aids it, which lets a higher current flow into the battery.

If you add an N-channel MOSFET to the circuit, you can protect the battery from this damaging condition

(Figure 2). The MOSFET conducts only when the battery is correctly connected, which lets the battery charge or discharge. In this condition, the transistor gets forward-biased, which switches on the MOSFET. If the battery is reverse-connected, the transistor and MOSFET turn off, thus preventing current flow. This simple circuit provides reverse-battery protection in both charger and battery paths, thereby protecting the battery, the charger, and the load. You can use a microcontroller to measure battery current and make a decision on appropriate action, as well.**EDN**

Figure 1 Batteries provide power to a load when utility power is off.

Figure 2 MOSFET  $\Omega_2$  protects the battery from excessive current.

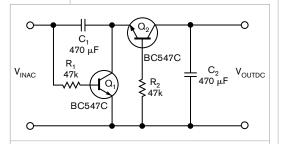

### Voltage doubler improves accuracy

S Chekcheyev, Tiraspol, Moldova

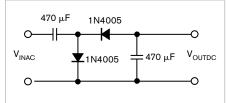

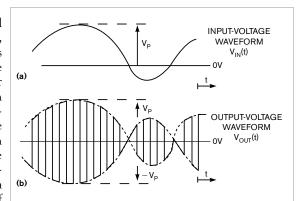

The voltage doubler in **Figure 1** provides more accurate voltage doubling than does the conventional voltage doubler in Figure 2 because it uses transistors instead of diodes. You can express the output voltage of the conventional doubler as  $V_{OUTDC} = 2V_{INAC} - 2V_{D}$ , where  $V_{OUTDC}$  is the output dc voltage,  $V_{INAC}$  is the amplitude of the

input ac voltage, and V<sub>D</sub> is the voltage across the forward-biased diodes. The error of the conventional voltage doubler is  $2V_D$ . Transistors  $Q_1$  and  $Q_2$  in Figure 1 are saturated during the positive and the negative half-cycles, respectively, of the input ac voltage. The operation of the saturated transistors is similar to the operation

of the forward-biased diodes in Figure 2. The collector-emitter voltage of the saturated bipolar transistors, however, is substantially smaller than the voltage across the forward-biased diodes. Thus, the error of doubling decreases.

Transistors  $Q_1$  and  $Q_2$  are reverse-biased during the negative and the positive half-cycles, respectively. The re-

Figure 1 An improved voltage doubler uses transistors for better accuracy.

verse beta of the bipolar transistors is small; consequently, the operation of the reversed transistors in Figure 1 is similar to the operation of the reversebiased diodes in Figure 2. Both circuits underwent tests with a resistive load of 10 k $\Omega$  and a 50-Hz, 2V-amplitude sinusoidal signal applied to the input. The measured output voltage of the conventional voltage doubler was 2.8V, and the error of doubling was  $2\times2V-2.8V=1.2V$ . The measured output voltage of the proposed voltage doubler was 3.8V, and the error of doubling was  $2\times2V-3.8V=0.2V$ .EDN

Figure 2 A conventional voltage doubler uses diodes.

### Digital controller compensates analog controller

David Caldwell, Flextek Electronics, Carlsbad, CA

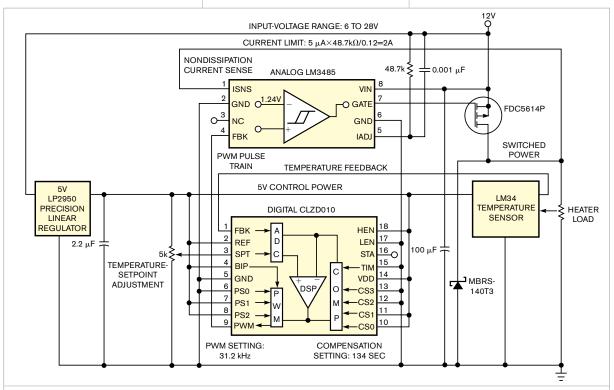

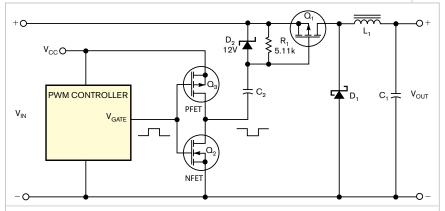

Emerging digital ICs for power control lack basic features, such as the built-in gate drive and current limiting, that you would normally find in analog ICs. Digital-power controllers generally have only PWM (pulsewidth-modulated)-logic output, and discrete gate drivers rarely include current limiting. In addition, most protected FETs work only in low-frequency, low-side applications.

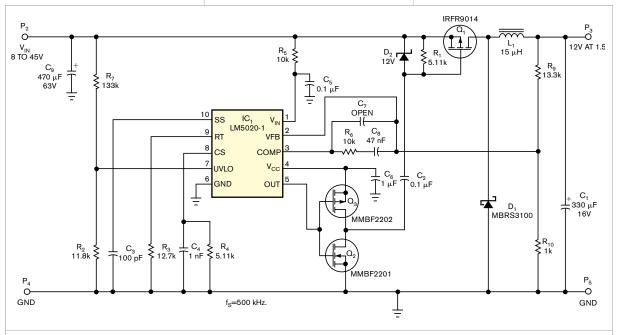

The LM3485 IC from National Semiconductor (www.national.com)

includes high-side gate drive with current limiting (Reference 1). However, the hysteretic-control scheme of this analog IC is likely to yield questionable performance in some applications due to variable switching frequency and overshoot, as well as an inability to regulate feedback below the 1.24V reference. A traditional PID (proportionalintegral-differential)-control scheme can get around these limitations but adds considerable complexity.

The CLZD010 CLOZD (Caldwell-

#### **DIs Inside**

- 51 Circuit provides constant-current load for testing batteries

- 52 MOSFET-based, analog circuit calculates square root

- 54 "Hippasian" nonlinear VFC stretches dynamic range

- 57 Decoder lights the way

- ►To see all of EDN's Design Ideas, visit www.edn.com/design ideas.

Figure 1 Combine the simple and robust closed-loop control of the digital CLZD010 with the current-limited high-side gate drive of the analog LM3485 for the best of both worlds.

loop-optimization-in-Z-domain) controller-chip IC from Flextek Electronics (www.flex-tek.com) both broadens and simplifies control applications though the embedded intelligence of a digital device (Reference 2). A single time-domain compensator replaces the three frequency-domain PID parameters, eliminating complex stability analysis. The circuit requires no PC interface because you inspect the openloop response and then use pin settings to configure the closed-loop compensation. However, the PWM output is only a logic-level driver.

Combine the simple and robust

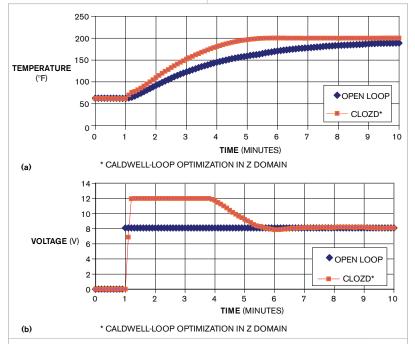

Figure 2 In the thermal-response example (a), the circuit takes about three minutes for the open-loop temperature to reach roughly two-thirds of its final value. The resultant closed-loop temperature quickly nears its final value due to maximum drive; voltage then decreases to allow the temperature to settle at the setpoint without overshoot (b).

closed-loop control of the digital CLZD010 with the current-limited high-side gate drive of the analog LM3485 for the best of both worlds (Figure 1). The PWM-logic level of the digital IC overrides the hysteretic comparator of the analog IC to switch the FET. A second comparator at ISNS, Pin 1 in the LM3485, turns off the FET if the voltage across it exceeds a predetermined value during conduction to limit current.

In the thermal-response example (Figure 2a), the circuit takes about three minutes for the open-loop temperature to reach roughly two-thirds of its final value, so closed-loop compensation, at 134 seconds, is slightly faster in Figure 1. The resultant closedloop temperature quickly nears its final value due to maximum drive; voltage then decreases to allow the temperature to settle at the setpoint without overshoot (Figure 2b). You can use this basic circuit combination to satisfy a broad range of applications in multiple industries.**EDN**

#### REFERENCES

- 1 "LM3485 Hysteretic PFET Buck Controller," National Semiconductor, September 2004, www.national.com/ ds/LM/LM3485.pdf.

- 2 "CLOZD Loop Controller Chip, Part CLZD010," Flextek Electronics, 2004, http://flex-tek.com/CLZD010. pdf.

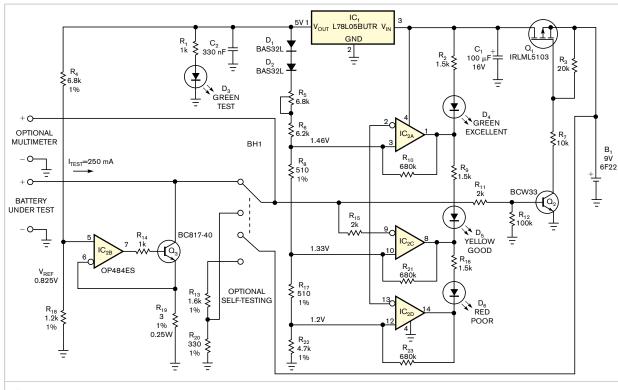

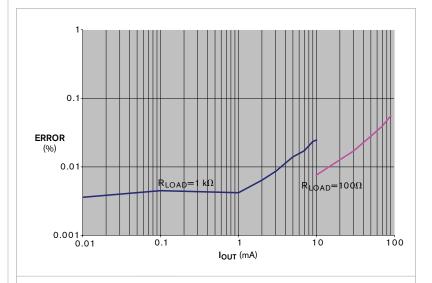

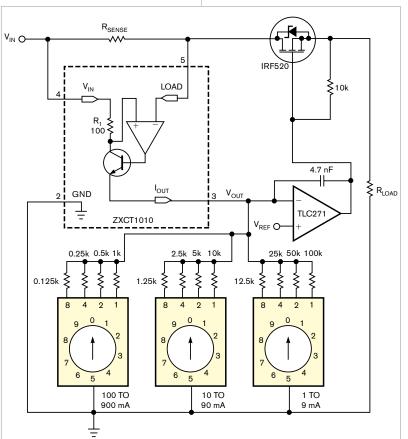

### Circuit provides constant-current load for testing batteries

Vladimir Rentyuk, Modul-98 Ltd, Zaporozhye, Ukraine

Suppose that you need to test a 1.5V, AA-size alkaline battery. You can apply a short circuit and measure current, or you can measure opencircuit voltage, but neither method properly tests the battery. A suitable test current of approximately 250 mA gives you a more reasonable test. You can use a  $6\Omega$  resistive load at 1.5V, which produces an output voltage of 1.46V at an ambient temperature of 25°C if the battery is in excellent con-

dition. A poor battery might produce less than 1.2V. Given the load, the output current at 1.2V will be 200 mA instead of 250 mA. The battery will have just 80% of a full load current. Instead, you can use the circuit in Figure 1 to produce a constant-current load.

The circuit uses a 9V battery and a voltage regulator to produce a steady power-supply voltage of 5V. From that voltage, the circuit produces a constant sink current, which is independent of the battery's output voltage, using IC<sub>1</sub>, IC,, and Q<sub>3</sub>. Your choice of current depends on battery size. You calculate the sink current of this circuit as  $I_{\text{TEST}}$  =  $1/R_{19} \times [V_{CC} \times R_{18}/(R_4 + R_{18})], \text{ where}$  $I_{ ext{TEST}}$  is the current you are testing and  $m V_{CC}$  is the voltage of resistive divider  $m R_4$ and R<sub>18</sub>. The voltage across R<sub>19</sub> should range from 0.3 to 0.85V for AAA and AA batteries. Transistor Q<sub>3</sub> should be in its active region. Resistor R<sub>14</sub> limits Q,'s base current to a safe level.

A suitable choice for the operational amplifier, IC2, is also important. You should use a single-supply op amp with a rail-to-rail input and a rail-to-rail output, such as Analog Devices' (www.

Figure 1 A tester of AA- or AAA-sized batteries uses constant-current load.

| TABLE 1 VOLTAGE RANGES FOR LEDs |                                     |                       |                |                       |                |                |  |  |  |  |

|---------------------------------|-------------------------------------|-----------------------|----------------|-----------------------|----------------|----------------|--|--|--|--|

| Condition                       | Battery<br>voltage <sup>1</sup> (V) | <b>D</b> <sub>2</sub> | D <sub>4</sub> | <b>D</b> <sub>5</sub> | D <sub>6</sub> | D <sub>3</sub> |  |  |  |  |

| Excellent                       | >1.46                               | Yes                   | Yes            | No                    | No             | Yes            |  |  |  |  |

| Good                            | >1.33                               | Yes                   | No             | Yes                   | No             | Yes            |  |  |  |  |

| Poor                            | >1.2                                | Yes                   | No             | No                    | Yes            | Yes            |  |  |  |  |

| Bad                             | >12                                 | Yes                   | No             | No                    | No             | Yes            |  |  |  |  |

| Unable to test                  | >12                                 | No                    | No             | No                    | No             | No             |  |  |  |  |

<sup>&</sup>lt;sup>1</sup>Ambient temperature is 25°C.

analog.com) OP484ES or OP496GS.

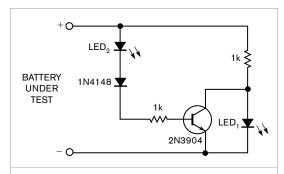

When you connect the battery under test, Q, turns on, which then turns on Q<sub>1</sub>, applying voltage from the 9V battery to the regulator. That action lights D, indicating that the battery under test has enough voltage to be tested. LEDs  $D_4$ ,  $D_5$ , and  $D_6$  indicate the battery's condition. Table 1 shows the voltage ranges necessary for these LEDs to light.

Op amps  $IC_{2A}$ ,  $IC_{2C}$ , and IC<sub>2D</sub> work as comparators with some hysteresis for operational stability. The resistive divider comprising R<sub>5</sub>,  $R_6, R_8, R_{17}, \text{ and } R_{22} \text{ sets}$

the voltage levels. Diodes D, and D, are optional but are useful when you need to operate the circuit outdoors, where temperatures vary widely. Resistor  $R_{15}$  protects the inputs of  $IC_{2A}$ ,  $IC_{2C}$ , and  $IC_{2D}$ .

When you connect a battery to test, you should test it for at least 5 seconds. LED D<sub>3</sub> shines if the battery is in relatively normal condition. In this case, switch Q<sub>1</sub> applies power to the battery tester. The sink-current generator comprising  $IC_{24}$  and  $Q_3$  loads the battery under test, and the resistor-divider network sets the comparator voltages.

You can add an optional self-testing button for checking the 9V battery to ensure that it has enough voltage to drive the circuit. You can also connect a digital multimeter to the multimeter terminals if you need a more accurate measurement. You can use a suitable rotary switch or a variable resistor and change the value of the test current by changing the value of R<sub>4</sub> to test another type or size of battery. EDN

### MOSFET-based, analog circuit calculates square root

Abhirup Lahiri, Netaji Subhas Institute of Technology, New Delhi, India

Square-root-calculating circuits find wide use in instrumentation and measurement systems for such tasks as calculating the rms (root-

mean-square) value of an arbitrary waveform, for example. Hence, designers need an effective analog squareroot calculator. Because manufacturers do much of the IC fabrication in MOS technology, a MOSFET-based, analog square-root calculator seems appropri-

<sup>&</sup>lt;sup>2</sup>This estimated value can be less.

ate. This Design Idea describes such a circuit, which uses only MOSFETs to provide the square-root function (Fig**ure 1**). The design is simple and versatile and can provide the output as the square root of the difference of two voltages.

The circuit uses the nested connection of MOSFETs  $Q_1$  and  $Q_2$ .  $Q_3$ works in the saturation region as it is diode-connected, forcing Q<sub>1</sub> to work in the triode region. All other MOS-FETs work in the triode region. The first part of the circuit, comprising  $Q_{,}$  $Q_4$ ,  $Q_5$ , and  $Q_6$ , creating the current  $I_{O1}$ , is basically a MOS-resistive circuit. The essential equation governing the circuit operation is:

$$V_{O} = \left(\sqrt{\frac{1}{K_{2}}} - \sqrt{\frac{1}{K_{1}}}\right) \sqrt{I_{O1}},$$

where K<sub>1</sub> and K<sub>2</sub> represent the aspect ratios of transistors  $Q_1$  and  $Q_2$ , respectively:  $K_I = (\mu C_{OX} W)/2L_I$ , where  $I=K_1=K_2$ . The MOSFETs creating the MOS-resistive circuit and hence responsible for the current creation are identical, having the same aspect ratio and threshold voltage. The current relates to inputs V, and V<sub>2</sub>, as the following equation shows:  $I_{O1} = G(V_1 - V_2)$ , where  $G = 2K(V_A - V_B)$  and represents the conductance of the MOS-resistive circuit— $k = (\mu C_{OX} W)/2L$ —of the identical transistors forming the MOS-resistive circuit, and  $V_A$  and  $V_B$ are control voltages applied to the gate of the MOSFETs that are working in the triode. This approach provides the advantage of voltage controllability of the output; hence, the square-rooting function is voltage-controllable.

The following equation gives the output voltage:

$$V_{O} = 2 \left( \sqrt{\frac{1}{K_{1}} + \frac{1}{K_{2}}} - \sqrt{\frac{1}{K_{2}}} \right) \times \sqrt{K(V_{A} - V_{B})(V_{1} - V_{2})}.$$

It is evident from this equation that the output voltage,  $V_{o}$ , is the square

Figure 1 This circuit uses only MOSFETs to provide the square-rooting function.

root of the difference of input voltages  $V_1$  and  $V_2$ . If you ground  $V_2$ , then the output voltage is proportional to the square root of input voltage  $V_1$ . As noted, control voltages  $V_{\Delta}$  and  $V_{R}$ can vary the proportionality constant. Hence, you have devised a new all-MOSFET-based, voltage-controllable analog square-root calculator.

You can test the circuit using a variety of commercially available MOS-FETs, such as the 2SK1228, which is available from many sources; the buffer can be a MOSFET-based op-amp buffer, such as the BUF04701 from Texas Instruments (www.ti.com). For the operation of the circuit to be in accordance with the output-voltage equation, the four MOSFETs you use

> to create the MOS-resistive circuit should be identical and should work in the triode region, for which inputs  $V_1$  and  $V_2$  should be less than  $V_A - V_{TH}$  and  $V_B - V_{TH}$ , respectively. The MOSFETs in the current mirror,  $Q_7$  and  $Q_8$ , should be identical, and the diode-connected MOSFETs,  $Q_1$  and  $Q_2$ , should be different and have different aspect ratios. You can test the circuit onboard using commercially available ICs, or you can simulate it on a computer using any standard version of Spice. The supply voltage must be in accordance with the selected components.EDN

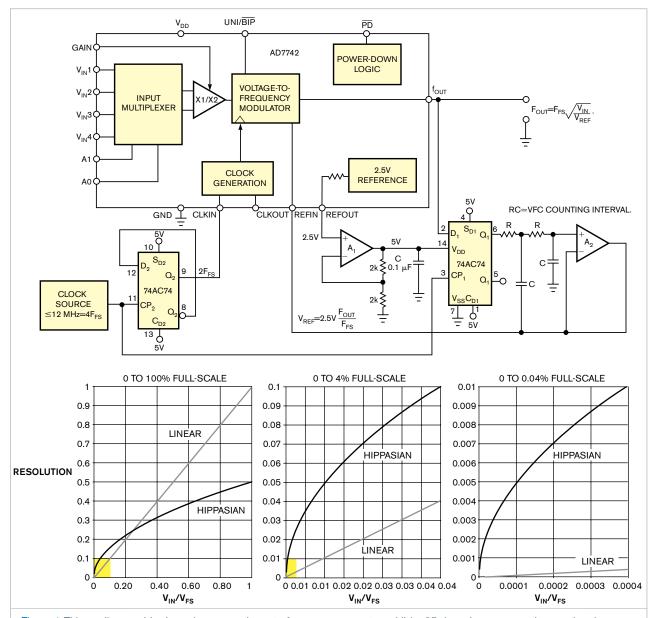

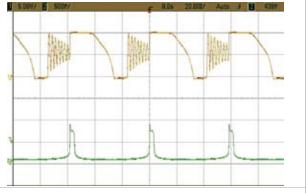

## "Hippasian" nonlinear VFC stretches dynamic range

W Stephen Woodward, Chapel Hill, NC

Hippasus of Metapontum was a Greek philosopher who lived approximately 500 BC. A disciple of Pythagoras, Hippasus discovered some interesting properties of square roots. This Design Idea describes a VFC (voltage-to-frequency converter) that also uses an interesting property of square roots: their ability to

extend VFC dynamic range by orders of magnitude (Figure 1).

Linear VFCs are one of the oldest types of ADCs, and their simplicity and noise rejection preserve their popularity. However, their Achilles' heel is the direct proportionality between dynamic range and conversion time. Because the voltage resolution of linear VFC conversion is equal to the full-scale voltage reference,  $V_{\text{REP}}$ divided by full-scale frequency,  $f_{FS}$ , multiplied by the counting interval, large dynamic range is inevitably associated with long counting intervals and slow conversion, even when clever VFC design provides for fast full-scale frequency.

For example: If you use a 3-MHz VFC-based ADC, such as Analog Devices' (www.analog.com) AD7742 with a 2.5V reference voltage in a design that requires 1-mV resolution, then

Figure 1 This nonlinear, wide-dynamic-range voltage-to-frequency converter exhibits 25-times improvement in counting time over other approaches.

you would need a minimum counting interval of 2.5/1 mV/3 MHz=2500/3 MHz=833 µsec. That counting interval yields only 1200 conversions per second, which for many applications is inconveniently slow.

The "Hippasian" VFC avoids this problem with a semiparabolic-transfer function instead of a linear one. It works by substituting  $V_{\text{REF2}}$ , which, instead of the constant  $V_{\text{REF}}$  of a linear VFC, is proportional to the output frequency. Then,  $V_{REF2} = V_{REF} \times f_{OUT}/f_{ES}$ ,

$$\begin{array}{l} f_{OUT} \! = \! V_{IN} \! \times \! f_{FS} \! / \! V_{REF2} \! = \! V_{IN} \! \times \! f_{FS} \! / \! (V_{REF} \! \times \! f_{OUT} \! / \! f_{FS}), \; (f_{OUT} \! / \! f_{FS})^2 \! = \! V_{IN} \! / \! V_{REP} \; \text{and} \\ f_{OUT} \! = \! f_{FS} \! \times \! (V_{IN} \! / \! V_{REF})^{1/2}. \end{array}$$

Generating the dynamic, output-frequency-proportional reference voltage is the job of op amps A<sub>1</sub>, which boosts the VFC's internal 2.5V reference to power flip-flop  $Q_1$ , and  $Q_1$  and  $A_2$ , which compose a high-performance frequency-to-voltage converter. The accuracy of the reference voltage depends on precise 50-to-50 symmetry of the VFC's input-clock reference. Flipflop Q, guarantees this symmetry.

The effect on conversion resolution of low-level signals is dramatic. To return to the example of a 2.5V full-scale, 1-mV-conversion resolution, which requires a 2500-count, 833-usec conversion interval with a linear 3-MHz VFC, the Hippasian version needs only 100 counts and 33 μsec—a 25-fold improvement. Software linearization of the Hippasian VFC conversion is easy, requiring only one multiplication.**EDN**

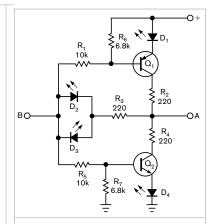

### Decoder lights the way

Jean-Bernard Guiot, Mulhouse, France

To display the status of two digital outputs, you can simply connect an LED and its resistor on each output. You must, however, interpret, or "decode," the displayed binary code. In addition, when no LED lights, users have no way of knowing whether it means that both outputs are off, that the power is off, or that a malfunction has occurred. In some applications, including industrial and medical settings, an indicator sending an ambiguous signal would be unacceptable. This Design Idea describes a simple circuit that resolves this problem by displaying four states on four LEDs (Figure 1). The operator need not understand binary coding, and, if no or more than one LED lights, it can mean only "no power" or "default."

The circuit works in the following way: If both inputs A and B are low, Q, allows current to pass through D, and resistor R, to A; only D, will light. Symmetrically, if both inputs A and B are high, Q, passes, and the current can pass from A through R<sub>4</sub>, Q<sub>2</sub>, and D<sub>4</sub>; only D<sub>4</sub> will light. If both inputs

> are on different levels, only D, or D, will light. Table 1 shows the possibilities; all other displays point to a default, such as a bad connection, a no-power condition, or a malfunction.

A totem-pole output that can sink and source

Figure 1 This simple circuit displays four states on four LEDs.

the current for one LED must drive the A and B inputs. Resistors  $R_2$ ,  $R_3$ , and R<sub>4</sub> are for applying a 12-mA LED current if the power supply is 5V. No component is critical. For example, you can use generic transistors, such as the NPN 2N3904 and the PNP 2N3906. You can even use transistors with integrated base resistors, further reducing the component count.EDN

| TABLE 1 LED-LIGHTING POSSIBILITIES |   |     |   |   |   |  |  |  |  |

|------------------------------------|---|-----|---|---|---|--|--|--|--|

| IN                                 |   | LED |   |   |   |  |  |  |  |

| Α                                  | В | 1   | 2 | 3 | 4 |  |  |  |  |

| 0                                  | 0 | 1   | 0 | 0 | 0 |  |  |  |  |

| 0                                  | 1 | 0   | 1 | 0 | 0 |  |  |  |  |

| 1                                  | 0 | 0   | 0 | 1 | 0 |  |  |  |  |

| 1                                  | 1 | 0   | 0 | 0 | 1 |  |  |  |  |

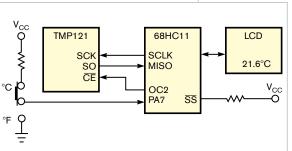

### Microcontroller converts digitaltemperature-sensor readings without floating-point arithmetic

Jordan Dimitrov, Toronto, ON, Canada

Digital temperature sensors combine a sensor, an ADC, and a serial interface in a single chip. They feature wide enough measurement range, good accuracy and resolution, no need of external parts, easy interface to microcontrollers, small size, and low price. In a review of 10 digital sensors from seven companies, all parts deliver signed-number data in two'scomplement format. They feature temperature ranges of -25 to +85 or -40to +125°C, accuracy of 0.5 to 2 or 2 to 4°C, and output data of 9 to 13 bits with 0.5 to 0.0312°C resolution. The devices' conversion time is 26 to 750 msec, and they use an SPI (serial-peripheral interface), an I<sup>2</sup>C (inter-integrated-circuit), or a 1-Wire interface. Power supplies are 1.5 to 3.6 or 3 to 5.5V, and prices range from 80 cents to \$2.10 (1000).

These sensors connect to microcontrollers; hence, size, speed, and time to develop firmware are also important. The standard approach is to use a high-level language and a compiler. Development time is short, and performing even complex calculations is not a problem. However, compilers produce machine code that occupies more memory and runs at lower speed than code from an assembler. Also, compiler IDEs (integrated development environments) cost hundreds of dollars, whereas many companies offer free assembly-language IDEs. If you work on a tight budget or memory-space allotment, assembly language is the better option. The problem is to find a simple way to avoid the necessary floating-point calculations to convert sensor data into human-understandable format, both in Celsius and Fahrenheit. This Design Idea presents an effective approach.

Consider the TMP121 sensor from Texas Instruments (www.ti.com). It provides 13-bit data in a 16-bit frame with resolution of 0.0625°C/ bit. Hence, the transfer function is  $t_c = 0.0625 \times N_s$ , where  $t_c$  is the tem-

> perature in degrees Celsius and N<sub>s</sub> is the sensor data after you remove the three meaningless least-significant bits. You can easily rearrange the above equation to:

$$t_{C} = \frac{5}{80} \times N_{S} = \frac{5}{80} \times N_{S} = \frac{1}{10}$$

Figure 1 A small system uses a 68HC11 microcontroller to read a switch and a sensor, to convert data. and to display temperature.

#### **DIs Inside**

- 44 Discrete-component buck converter drives HB LEDs

- 47 Drive a single-coil latching relay without an H-bridge circuit

- 48 Limit switches control dc-motor H bridge

- 50 Implement a clip-detection circuit for BTL Class D amplifiers

- ►To see all of EDN's Design Ideas, visit www.edn.com/design ideas.

To get readings in degrees Fahrenheit, use the following equation, which converts degrees Celsius into degrees Fahrenheit:  $t_F = [(9/5) \times t_C + 32]$ . Replacing t<sub>C</sub> from the above equations vields:

$$t_{F} = \frac{9}{5} \times \frac{5}{80} \times N_{S} + 32 =$$

$$\left(N_{S} + \frac{N_{S}}{8} + 320\right) \times \frac{1}{10}.$$

(2)

The benefit of equations 1 and 2 is that you can perform the calculations with integer arithmetic only. They require divisions by powers of two, which you can replace with shifts, and division by 10, which you perform by introducing a decimal point in the display.

The circuit underwent testing with the popular 68HC11 microcontroller from Motorola (www.motorola.com, Figure 1). Besides a sensor and a controller, it includes a unit-selection switch and a dot-matrix LCD. The display resolution is 0.1°. The core of the supporting firmware is an endless loop in which the 68HC11 uses an output-compare function to generate a square-wave signal with a