#### JANUARY

Test continuity with an LED Reliable 555 timer doesn't falsely trigger Flash an LED from ac-mains power Transistors drive LEDs to light the path Use an optocoupler to make a simple low-dropout regulator Generate noisy sine waves with a sound card Oscillator has voltage-controlled duty cycle Decode a quadrature encoder in software Power an LED driver using off-the-shelf components

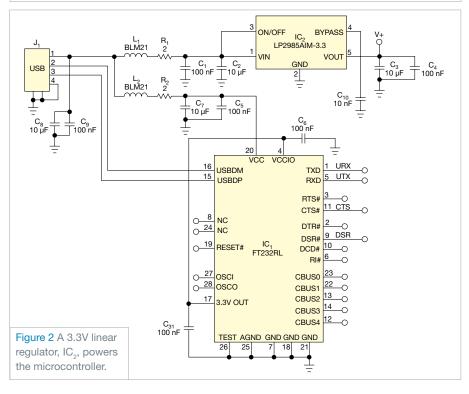

#### FEBRUARY

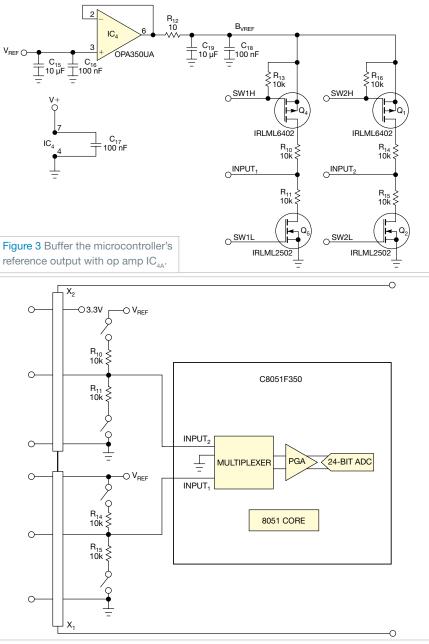

Compute a histogram in an FPGA with one clock Protect MOSFETs in heavy-duty inductive switched-mode circuits Control an LM317T with a PWM signal High-speed buffer comprises discrete transistors Limit inrush current in high-power applications Power supply accepts wide input-voltage range Reduce acoustic noise from capacitors Function generator has variable frequency Circuit lets you test capacitors

#### MARCH

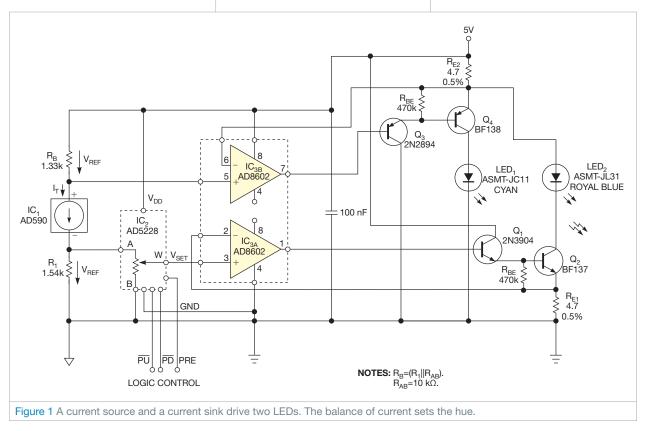

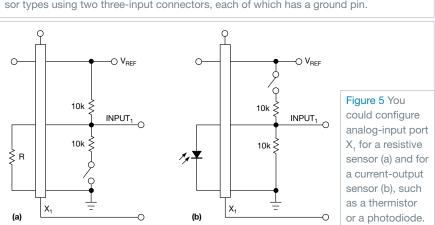

Design provides single-port-to-dual-port SDRAM converter Bicolor LED indicates 10 states Zener diode protects FPGA inputs Relay driver switches two relays with one pin Anticipator circuit speeds signal settling to a final value Schmitt trigger provides toggle function Active multiplexing saves inputs Transistor tester identifies terminals Finely tune the hue of blue-light sources

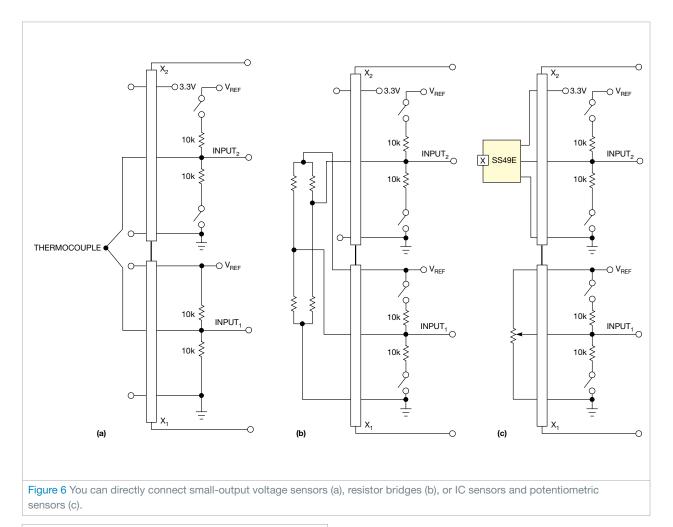

#### APRIL

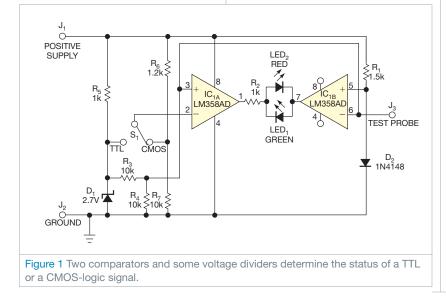

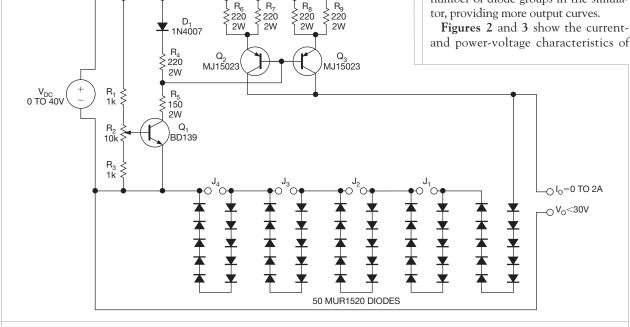

Low-component-count logic probe works with TTL and CMOS logic Circuit implements photovoltaic-module simulator Switch circuit controls lights Isolated PWM suits low frequencies Light an LED without wasting energy Increase efficiency in embedded digital-I/O lines Modulating a reference allows maximum-value search for phase detection Offline supply drives LEDs

#### MAY

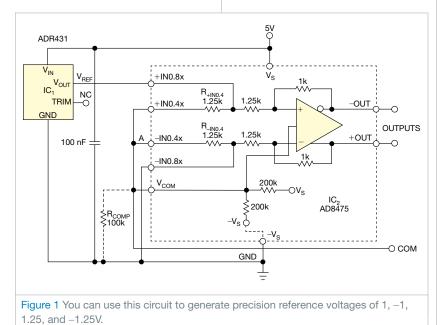

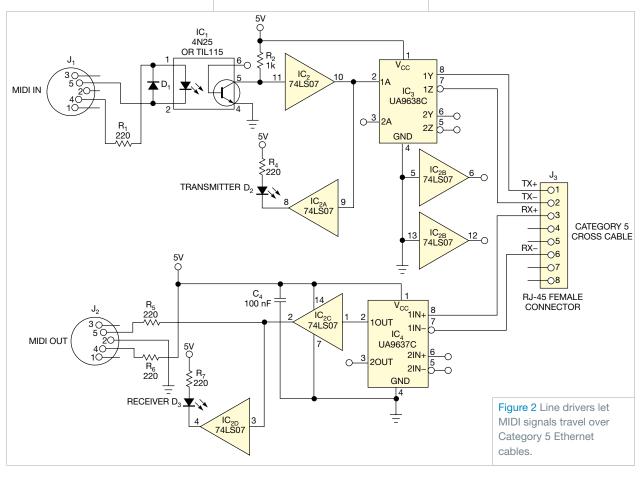

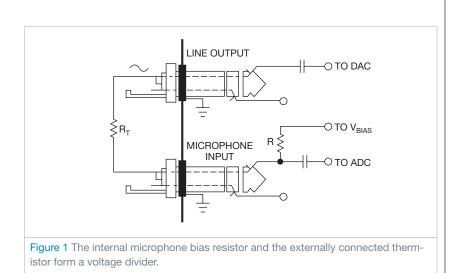

MOSFET provides high power at low loss Circuit secures bootstrap operation under light load Build an accurate bipolar voltage reference Send MIDI signals over long distances Arrange LEDs as seven-segment displays Logic gates form high-impedance voltmeter Waveform generator minimizes amplitude dependency Produce current from positive or negative high-voltage supplies Measure resistance and temperature with a sound card

#### JUNE

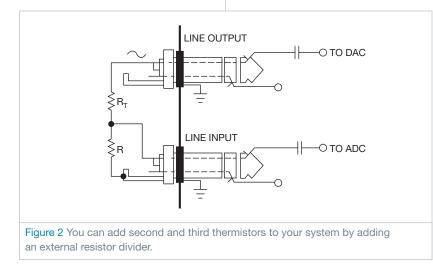

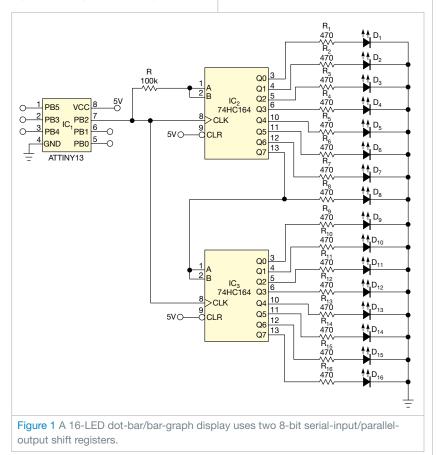

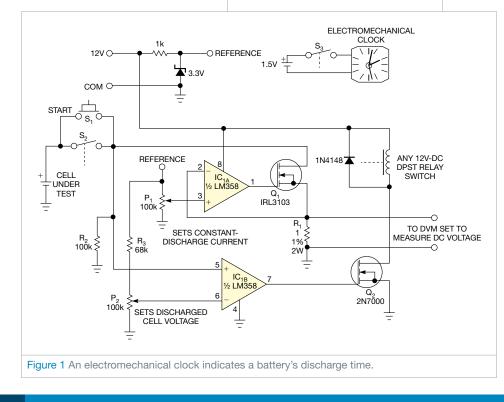

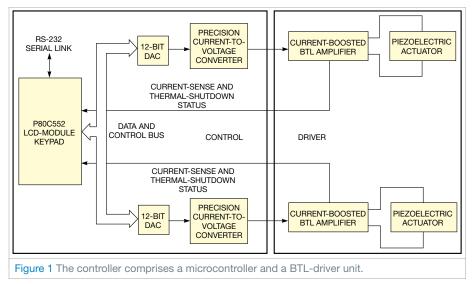

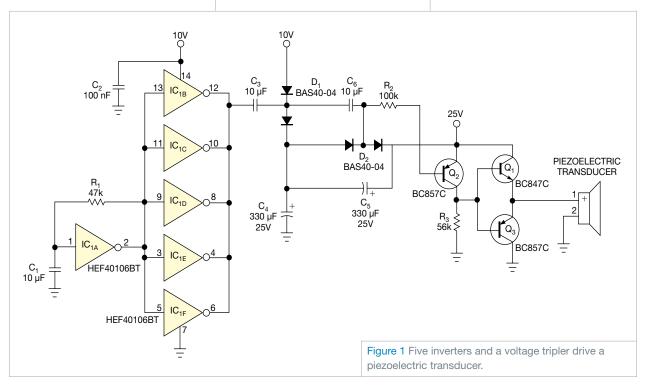

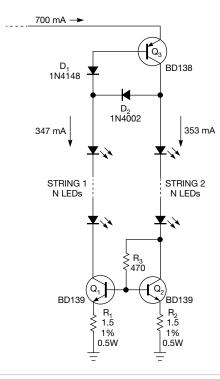

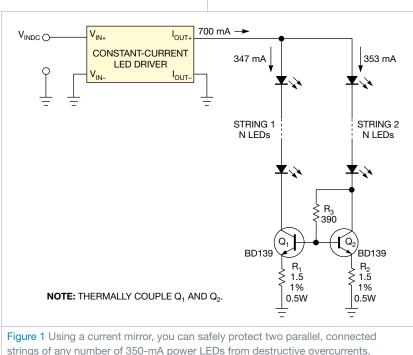

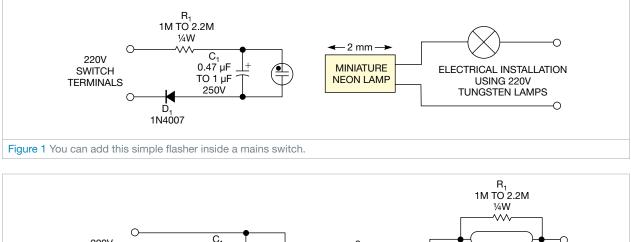

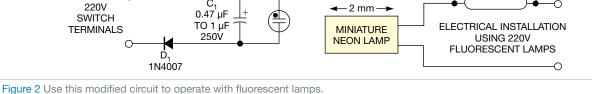

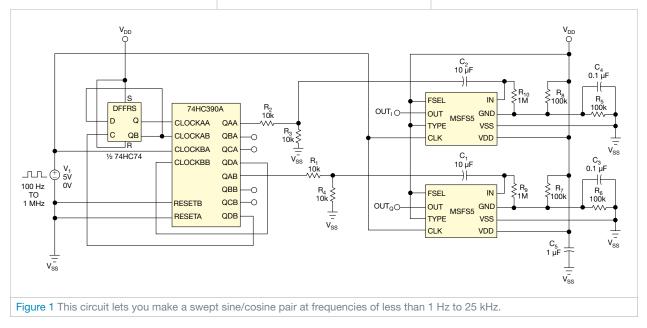

Drive 16 LEDs with one I/O line Potentiometer calibrates photodiode amplifier Circuit measures battery capacity Programmable driver targets piezoelectric actuators Circuit boosts voltage to piezoelectric transducers Use resistor noise to characterize a low-noise amplifier Protect power-LED strings from overcurrent Simple flasher operates off ac mains Build a UWB pulse generator on an FPGA Generate swept sine/cosine waveforms with two filters

#### JULY

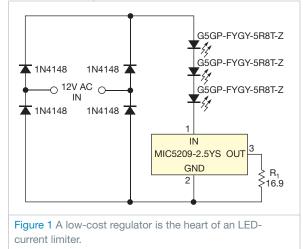

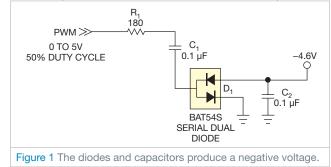

Compensate for four-wire sensor errors LED-current limiter accepts ac or dc Voltage inverter employs PWM Form positive pulses from negative pulses Positive edges trigger parabolic timebase generator Measure small currents without adding resistive insertion loss Power resistor varies in value Minimize noise in power-supply measurements

#### AUGUST

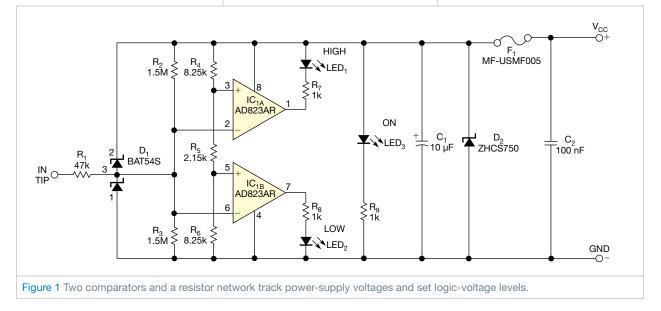

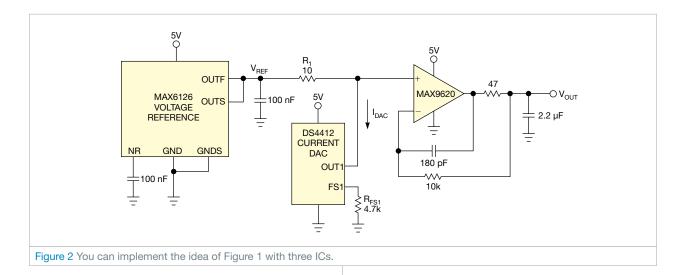

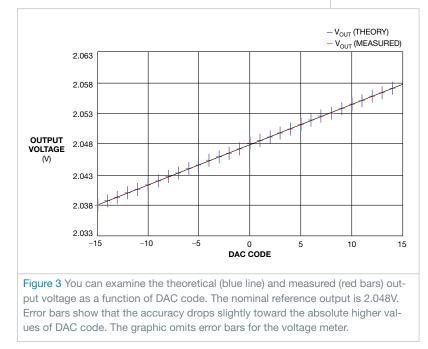

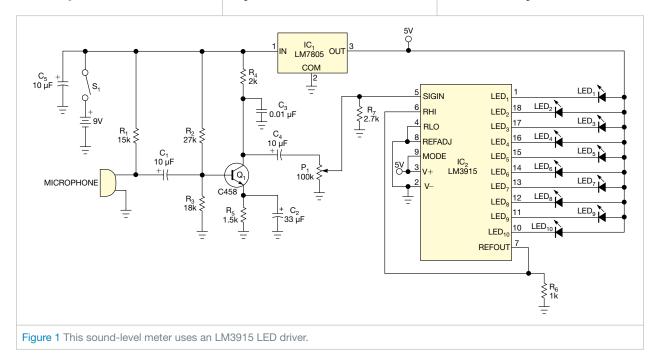

Driver circuit lights architectural and interior LEDs Use op amps to make automatic-ORing power selector Charging time indicates capacitor value Circuit provides universal ac-input-voltage adapter Logic probe uses two comparators DAC fine-tunes reference output LEDs indicate sound level

#### SEPTEMBER

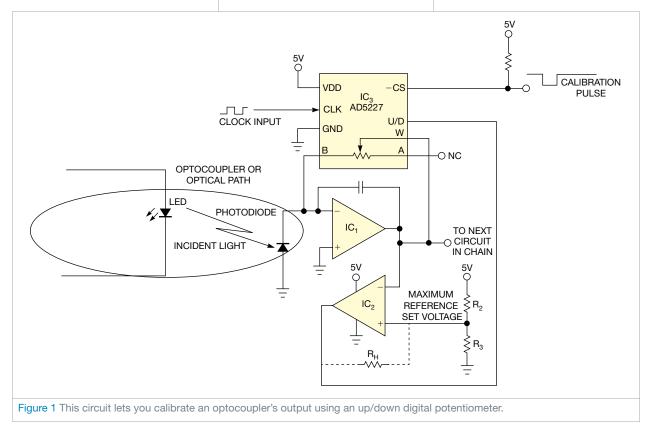

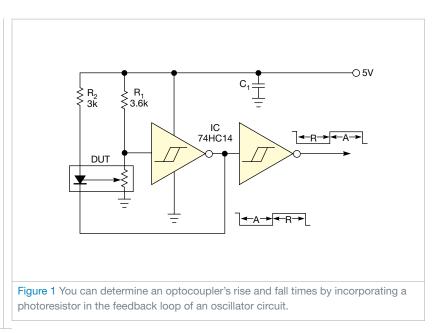

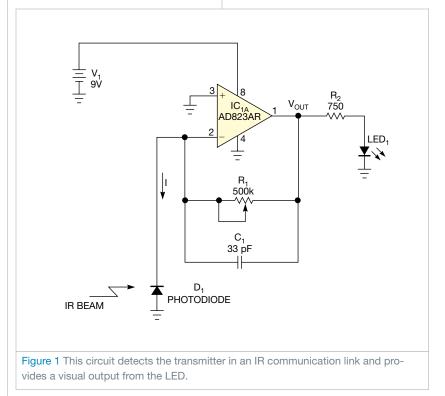

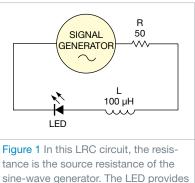

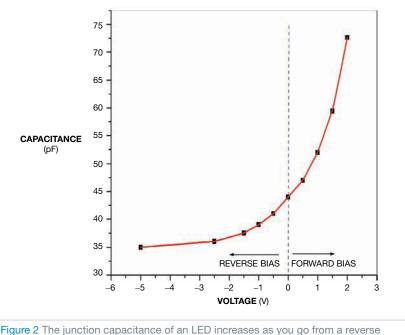

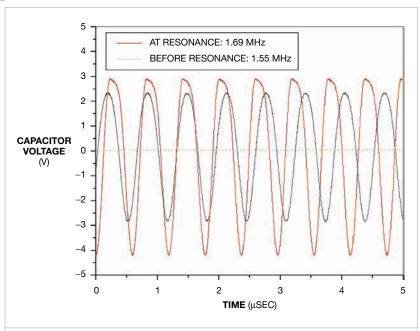

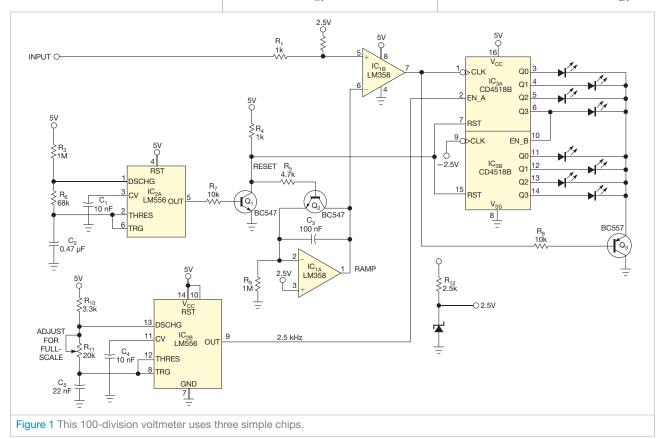

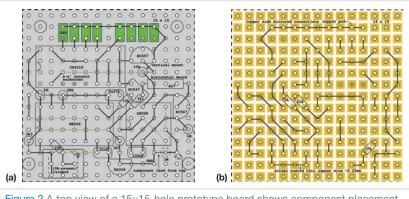

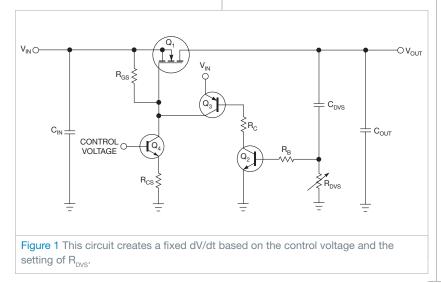

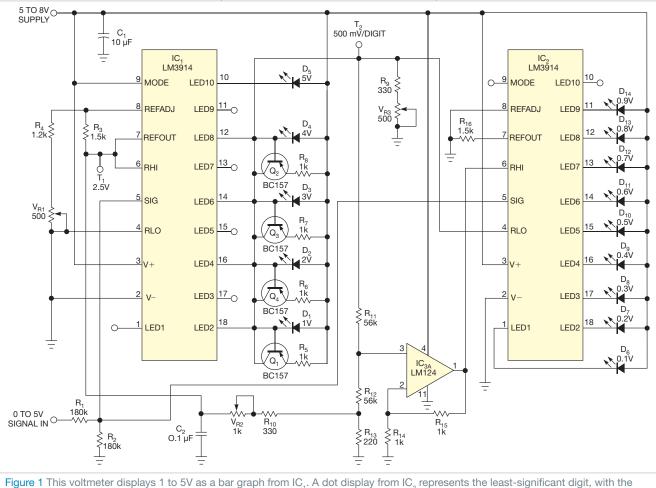

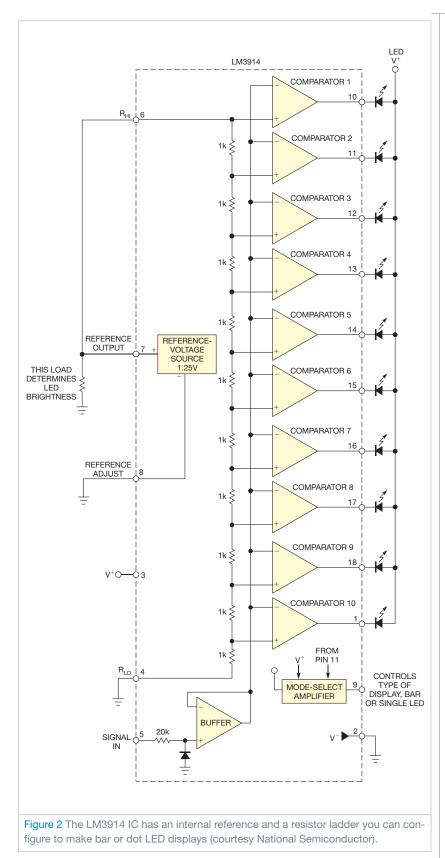

Polynomial rotation accelerates CRC calculations Simple circuit measures optocoupler's response time Circuit provides visual verification of IR pulses An LED's intrinsic capacitance works in a 650-mV LRC circuit Eight LEDs make a 100-division voltmeter Simple circuit controls the rate of voltage change across a capacitor or another load LED bar-graph display represents two digits

#### OCTOBER

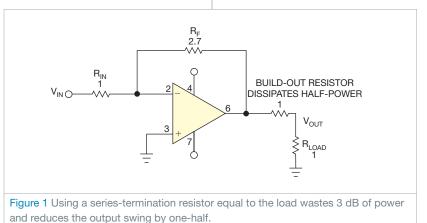

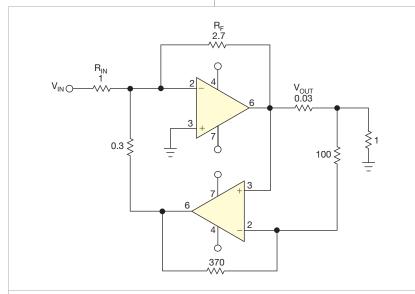

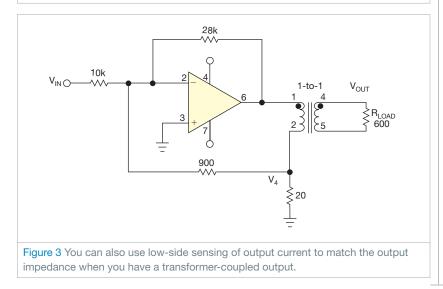

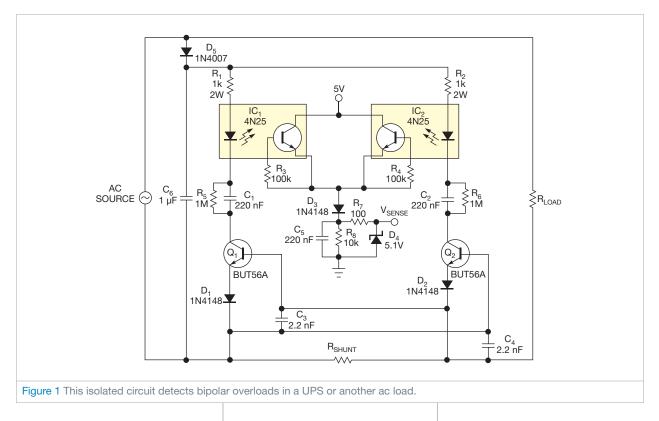

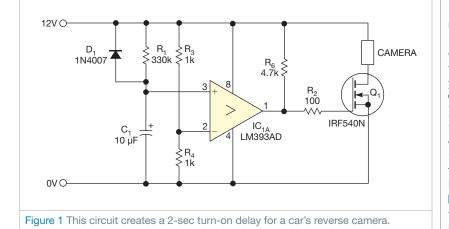

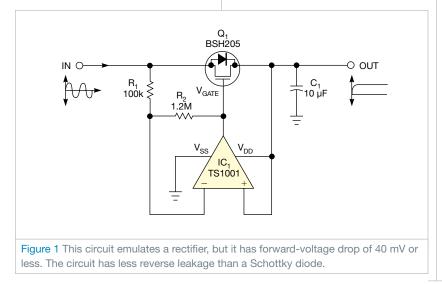

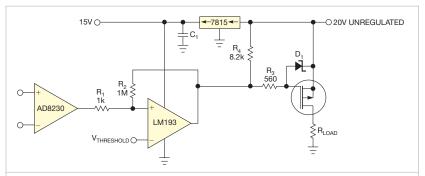

Circuit controls inrush current in ac-operated power supplies Save 3 dB of output power using feedback to set the output impedance Optically isolated overcurrent detector works from ac mains Simple circuit helps to protect a vehicle-reverse camera Use a self-powered op amp to create a low-leakage rectifier Simple reverse-polarity-protection circuit has no voltage drop Series-LC-tank VCO breaks tuning-range records

#### NOVEMBER

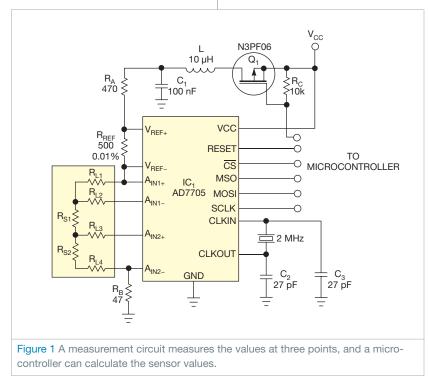

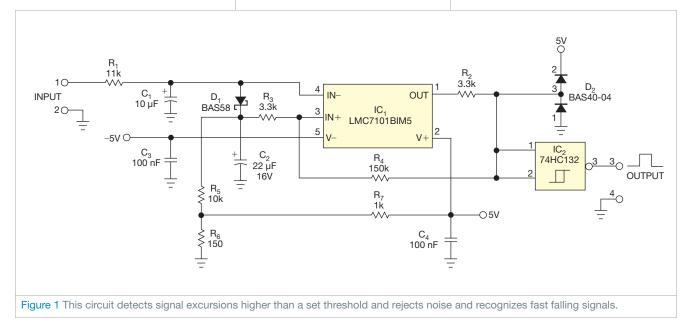

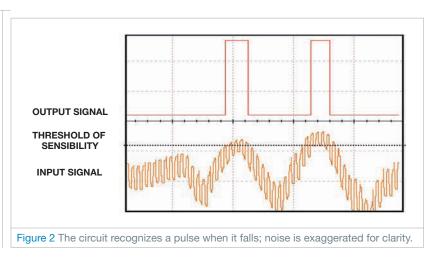

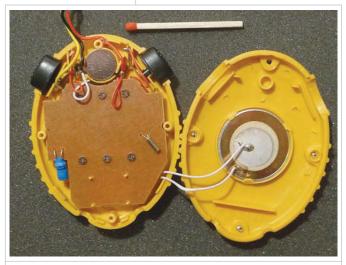

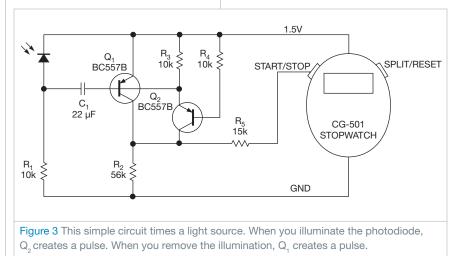

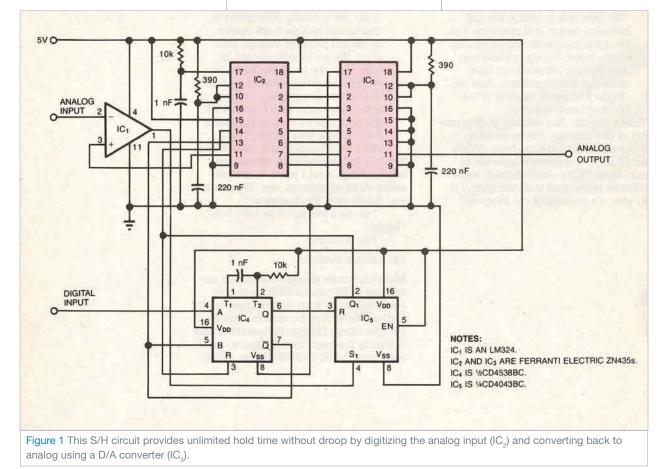

Circuit detects rapidly falling signals and rejects noise Hack into a stopwatch to make a phototimer Comparator directly controls power-MOSFET gate AGC circuit uses an analog multiplier Add extra output to a boost converter Fabricate a high-resolution sensor-to-USB interface Converters yield droop-free S/H circuit

#### DECEMBER

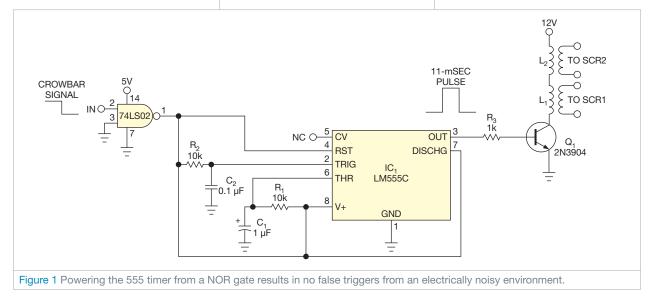

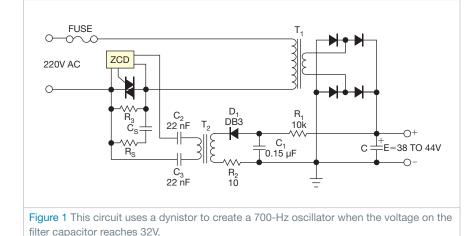

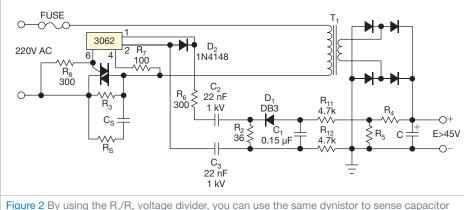

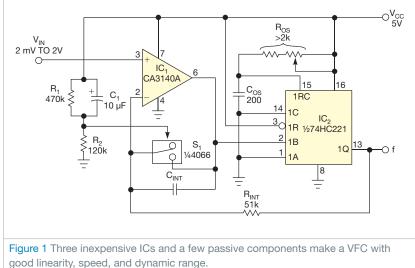

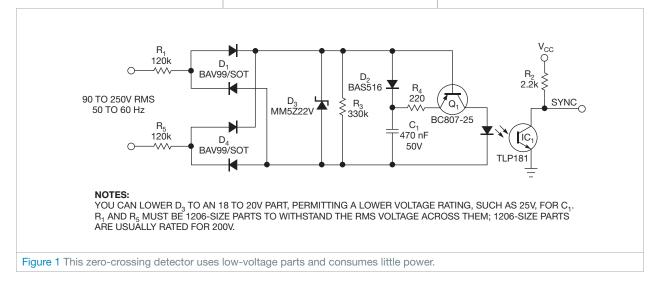

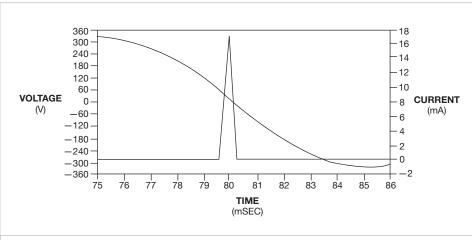

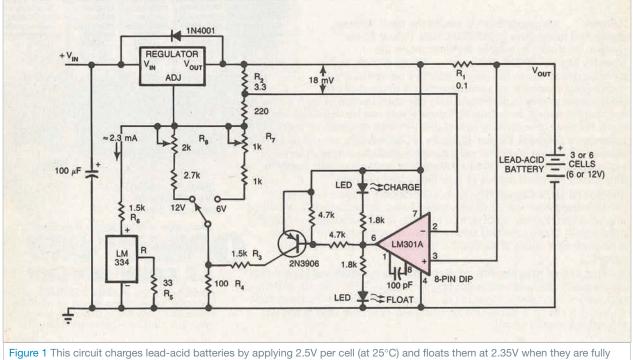

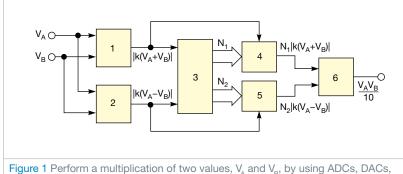

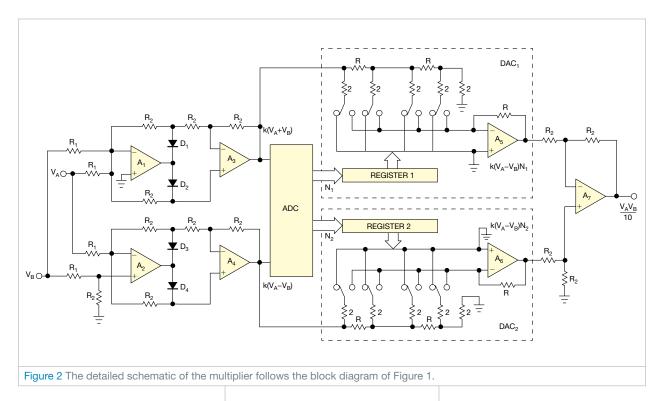

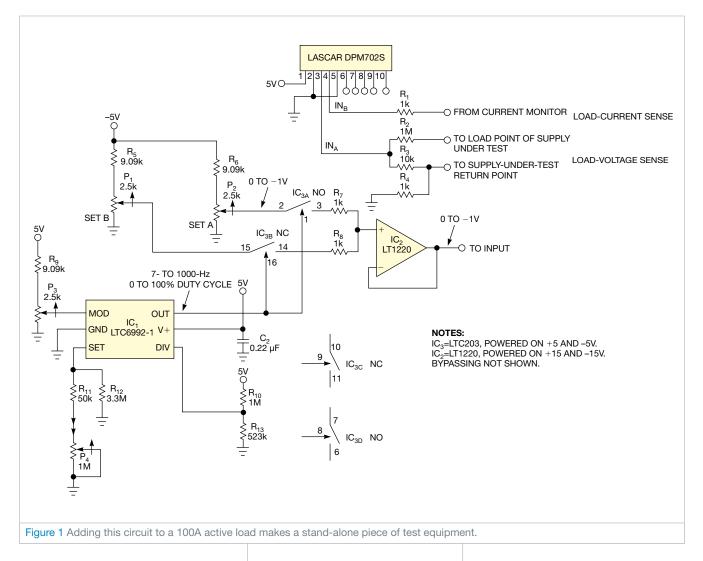

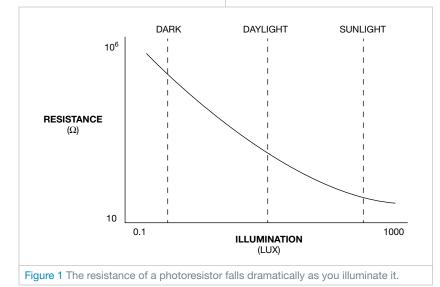

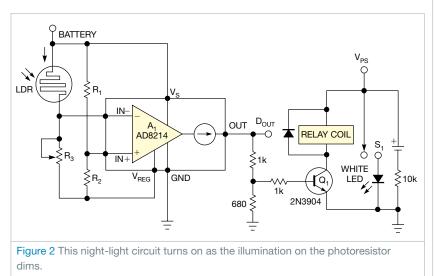

A diode ladder multiplies voltage under software control Inexpensive VFC features good linearity and dynamic range Mains-driven zero-crossing detector uses only a few high-voltage parts Build an op amp with three discrete transistors Charger extends lead-acid-battery life Circuit provides more accurate multiplication A few added components make a self-contained controller for 100A load Simple night-light uses a photoresistor to detect dusk Simple tester checks Christmas-tree lights

# CESTO CONTRANSPONDENCE CONTRANSPONDENCE

### Test continuity with an LED

Raju R Baddi, Raman Research Institute, Bangalore, India

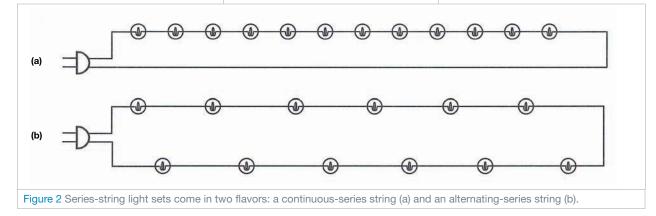

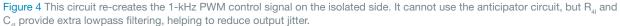

You sometimes need to know whether a resistance exceeds a preset limit. The continuity tester in **Figure 1** lets you determine that fact for resistances of  $0.5\Omega$  to  $10 \text{ k}\Omega$ . The heart of the circuit is the transistor pair comprising  $Q_1$  and  $Q_2$ , whose emitters draw current from a single source,  $R_E$ . Insert the circuit under test,  $R_{CY}$ , between Point A and Point B. To set the limit, use a known resistance for  $R_{CY}$  and set the trimming potentiometer until the LED begins to light.

The current through  $R_E$  divides between  $Q_1$  and  $Q_2$  in proportions based on the resistances of the two loops. The circuit lets you set the low limits to values as low as  $0.5\Omega$  because the emitter current in  $Q_2$  can change rapidly with small changes in its  $V_{\text{BE}}$  (base-to-emitter voltage). The remaining current originating in  $R_{\text{E}}$  goes through the emitter of  $Q_1$ , whose collector then suffers voltage changes on the order of approximately 100 mV because most of a transistor's emitter current flows to its collector.

At extremely low limits, a large change in emitter current can easily accommodate the drop in voltage across  $R_{CY}$  in Loop 2. The extra current goes through Loop 1. At the critical value of  $R_{CY}$ , Loop 1 conducts a much higher current than Loop 2, which again means a much smaller  $V_{BE}$  change for  $Q_2$ .

#### **DIs Inside**

48 Flash an LED from ac-mains power

50 Reliable 555 timer doesn't falsely trigger

50 Transistors drive LEDs to light the path

51 Use an optocoupler to make a simple low-dropout regulator

► To see all of *EDN*'s Design Ideas, visit www.edn.com/design ideas.

The online version of this Design Idea, available at www.edn.com/110106dia, includes an appendix that provides

a detailed analysis of the circuit's dc performance.

When  $R_{CY}$  is an open circuit or has a resistance above the set limit, a larger portion of the current through  $R_E$  flows to the emitter of  $Q_1$ , which produces a voltage across  $R_3$ . That voltage is close to the voltage at the emitter of  $Q_3$ . Thus,  $Q_3$  doesn't have sufficient  $V_{BE}$  to turn on. In turn,  $Q_4$  is off, and the LED doesn't illuminate.

When the resistance of  $R_{CY}$  is under the set limit,  $Q_2$  begins to draw its share of current from  $R_{e}$ . This step reduces the current through the collector of  $Q_1$ , and the voltage drop across  $R_3$  also decreases. The difference in voltages between the collector of  $Q_1$  and the emitter of  $Q_3$  exceeds  $V_{BE}$ ,  $Q_3$  then conducts, turns on  $Q_4$ , and lights the LED.

The tester's quiescent current is 10 mA, making the tester suitable for a bench instrument. If you need battery power, such as a 3.6V nickel-cadmium or lithium-ion battery, however, you can reduce the LED's series resistance by less than  $47\Omega$  and change Q<sub>3</sub>'s emitter voltage. (See the appendix, which is available

online at www.edn.com/110106dia.)

Use two variable potentiometers in series whose values—1 k $\Omega$  and 100 $\Omega$ , for example—differ by an order of magnitude. This approach allows you to make precise limit adjustments at lower limits.

The values in parentheses in Figure 1 are substitute values. You can substitute five 1N4148 diodes for the 3.2V zener diode. Both arrangements perform well. The LED may go a bit dim toward the low limit, approximately  $0.5\Omega$ , so use one with a transparent lens.EDN

## Flash an LED from ac-mains power

TA Babu, Chennai, India

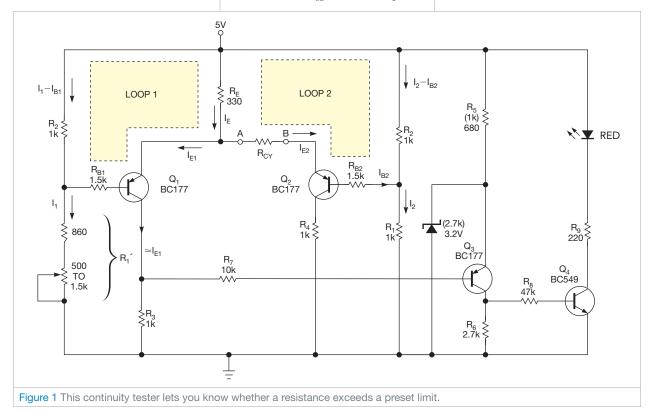

LED technology is opening the door to a variety of high-power-illumination applications. The circuit in **Figure 1** can let you know when ac power is available. To drive a power LED from the ac line requires a converter or a similar arrangement. In this circuit, a passive

cuit drives the LED with a constant current, you can use any LED color to suit the situation.

The circuit uses a simple DIAC (diode-alternating-current) relaxation oscillator, which activates a constant-current switching circuit comprising IC<sub>2</sub>

dropper greatly simplifies the total design. You can also simplify the circuit to run on dc power, which lets you use it from automotive batteries to supply light at night.

The design comprises an inrush-limiting resistor,  $R_i$ ; a half-wave rectifier with a filtering capacitor comprising  $D_2$ ,  $D_3$ ,  $D_4$ , and  $C_2$ ; a relaxation oscillator; and two high-power LEDs. Because the cirand  $Q_1$ . The DIAC turns on when capacitor  $C_3$  charges through diode  $D_1$  and resistor  $R_2$  from the mains voltage. After a number of half-cycles of the mains, the voltage on  $C_3$  exceeds the break-over voltage of the DIAC, the DIAC conducts, and  $C_3$  discharges through  $R_3$  and optocoupler IC<sub>1</sub>. The optocoupler activates the constant-current switching

circuit, resulting in a brief, intense flash of light from the LEDs.

High-voltage capacitor  $C_1$ , part of the passive dropper, limits the current drawn from the power line, as the following **equation** shows:

$$I_{RMS} = \frac{V_{AC}}{X_{ACCAPACITOR}} = \frac{V_{AC}}{\frac{1}{2\pi FC}} = 2\pi FCV_{AC}.$$

A 47 $\Omega$  metal-oxide resistor, R<sub>1</sub>, acts as an inrush-current limiter. Because the LEDs require a lot of energy, it's not feasible to directly drive them using a small-value capacitive dropper. Instead, this circuit uses a 2200-µF capacitor, C<sub>2</sub>, to collect and store energy from the power line between flashes. Zener diode D<sub>4</sub> limits the capacitor voltage to 12V.

The easiest constant-current approach is to use an adjustable linear regulator, such as Linear Technology's (www.linear. com) LM317. The regulator maintains a voltage of 1.25V across series resistor  $R_5$ . The 1.25V is the reference voltage of the regulator. Consequently, you can determine the load current with the following equation:  $I_{LED}=1.25/R_5$ . The active current limiting is 320 mA, which is sufficient to produce an intense light flash.

As a note of caution, this circuit has no galvanic isolation from the ac mains. Most nodes are, therefore, at mains potential and hence dangerous. You should not construct this circuit unless you have experience in handling high-voltage circuits.EDN

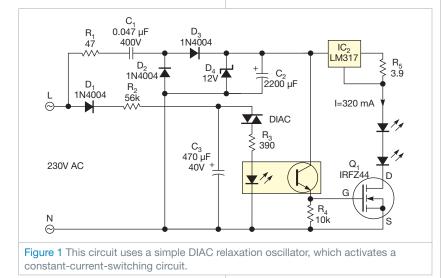

## Reliable 555 timer doesn't falsely trigger

John Dawson, Opelika, AL

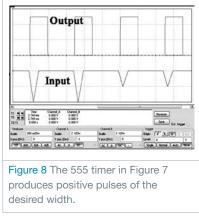

Circuits employing the popular 555 timer circuits are often reliable under many conditions. When you use them in electrically noisy environments, however, the timer can produce a false trigger, no matter how well you filter its power-supply lines. The circuit in **Figure 1** sends a pulse to an SCR (silicon-

controlled-rectifier) crowbar circuit when the 555's input pulls low due to a fault-detection circuit. The 555 timer chip is unpowered until a crowbar fault signal occurs. The logic-low signal forces the 74LS02 NOR gate's output high, which provides enough power to operate to the 555 timer circuit. The timer triggers on power-up. Capacitor C<sub>2</sub> holds the trigger signal low until it charges to 5V. The 555 timer's output should drive a low-current device—in this case, a transistor switch. This circuit solves the problem of false triggers. The pulse transformers connect to two SCRs in series that pulse 1600 to 2000V dc to fire a crowbar for a 22-kV dc power supply. The SCR-controlled high-voltage power supplies are electrically noisy, causing many false triggers from the 555 timer circuit.EDN

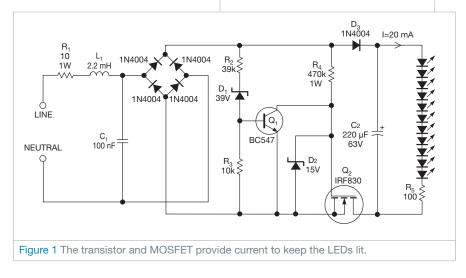

## Transistors drive LEDs to light the path

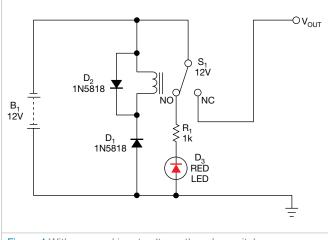

Eliot Johnston, Comnet International, Richardson, TX

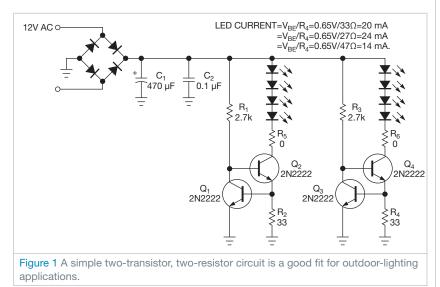

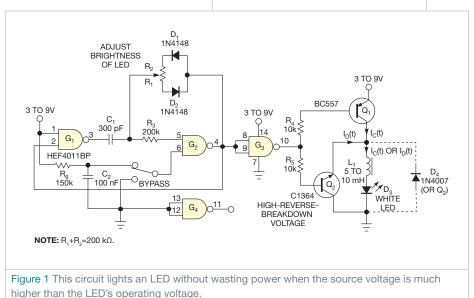

Keeping low-voltage outdoor lights illuminated takes some effort. Bulbs burn out, and connections corrode. HB LEDs (high-brightness light-emitting diodes) seem like acceptable replacements, but most are available only in surface-mount packages, which aren't conducive to a backyard project. In addition, you must create a reflector for tiered lighting. Low-power LEDs, which come in finished packages, are more appealing, but you must have a way to drive them. Numerous driver ICs are available, but they, too, usually are available in surface-mount packages. Furthermore, the cost of the parts can add up to an expensive project. The simple two-transistor, two-resistor circuit in Figure 1 provides a better fit for this application.

The two transistors and two resistors act as a simple current source.  $Q_1$ 's baseemitter voltage,  $V_{BE}$ , combines with re-

Figure 2 Two identical circuits on a round PCB can drive eight LEDs, producing a relatively consistent light output.

sistor  $R_2$  to set the LED current at approximately 20 mA. In this application, even a tolerance of ±10% doesn't significantly affect LED performance. Thus, only the value of  $R_2$  is somewhat critical.

The 7 and 11W incandescent outdoor lights in this setup receive their power from a 12V-ac photoelectric timer. The bridge rectifier and filter capacitor produce approximately 15V dc—enough to drive four white LEDs, each with an approximately 3.2V forward-voltage drop. A small-value resistor,  $R_5$ , may be necessary to offload some of the power dissipation of the main pass transistor. In this setup, however,  $Q_2$  dissipates only around 50 mW, so it can use just a jumper wire for  $R_5$  hence, the schematic shows it with a value of  $0\Omega$ . Two identical circuits on a round PCB (printed-circuit board) can drive eight LEDs, producing a relatively consistent light output using Cree (www.cree.com) C535A-WJN series 110°-viewing-angle LEDs (**Figure 2**).

The lighting network uses two 144W transformers, which probably consume

more energy than the new LED lamps. Once you replace all the bulbs with LEDs, power consumption should drop from approximately 200W to approximately 20W. You then connect the two strings together and remove one of the transformers. You could also build an ef-

#### SOLDER THE WIRES DIRECTLY TO THE PCB, LEAVING THE POTEN-TIAL FOR CORROSION AT THE CONNECTION TO THE MAIN WIRE.

ficient 120V-ac to 15V-dc power supply into the transformer housing and send dc down the wire rather than 12V ac.

You should use an automotive clearcoat spray to seal everything from moisture. This circuit should provide more than 10 years of service life. Contact corrosion causes reliability problems. Corrosion tends to set into the stab connection to the main wire and at the bulb itself. Instead of plugging in the replacement, you can solder the wires directly to the PCB, leaving the potential for corrosion at the connection to the main wire. Removing some insulation and soldering the wires makes for a more reliable connection. Remember to coat each splice with some silicon RTV (room-temperature-vulcanizing) sealant.EDN

# Use an optocoupler to make a simple low-dropout regulator

Marc Ysebaert, De Pinte, Belgium

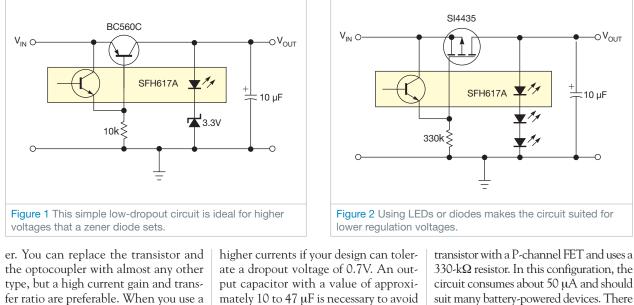

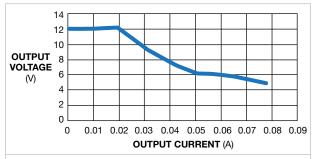

Although a monolithic low-dropout regulator has superior dynamic characteristics, the discrete regulator in this Design Idea is so simple that you can adapt it to many purposes. Using a common transistor, it has a dropout voltage of 0.1V. This dropout voltage can be even less if you use a FET. In the circuit in **Figure 1**, the optocoupler's LED determines the approximately 1V output voltage, which the circuit adds to the voltage of the zener diode. A low-current zener diode gives the best results because regulation occurs at less than 1 mA, depending on the current gain of the transistor. To regulate the voltage of one battery cell, you can omit the zener diode to a given output voltage of approximately 1V. You can also replace the zener diode with a potentiometer to obtain a variable output voltage. Another alternative is to use a combination of one or more LEDs or regular or Schottky diodes to obtain a fixed output voltage. You can insert a low-current LED as part of the voltage-reference branch to give an indication of the proper operation of the regulator.

The circuit in **Figure 1** consumes approximately 1 mA and starts to limit the current at currents higher than approximately 50 mA. With a lower value for the resistor, the LED glows brighter, the output voltage is slightly higher, and the current consumption and the current limit are proportionally high-

high-voltage transistor, the input voltage can be much higher than is possible with common monolithic regulators. You can use a Darlington transistor for mately 10 to 47  $\mu$ F is necessary to avoid oscillation. Higher values are necessary for higher output currents. The circuit requires no input capacitor.

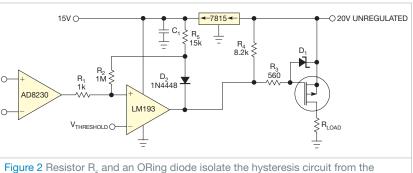

The circuit in Figure 2 replaces the

330-k $\Omega$  resistor. In this configuration, the suit many battery-powered devices. There is no inherent current limiting. You can reduce R<sub>1</sub> to  $10 \text{ k}\Omega$  or lower to have a faster response to load change and to obtain a visual indication with the LEDs.EDN

# CESTO CONTRACTOR OF CONTRACTOR

# Oscillator has voltage-controlled duty cycle

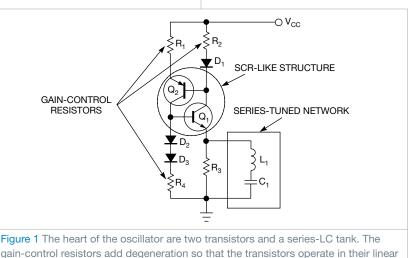

Luca Bruno, ITIS Hensemberger Monza, Lissone, Italy

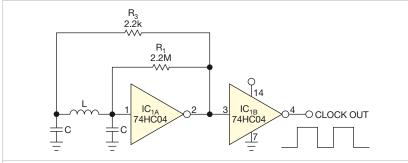

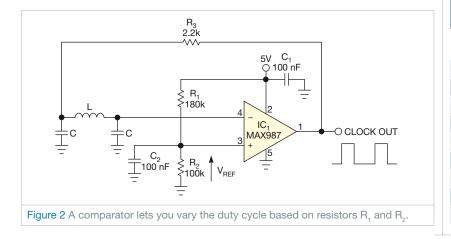

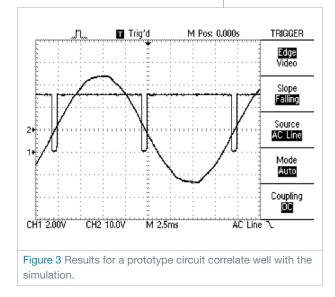

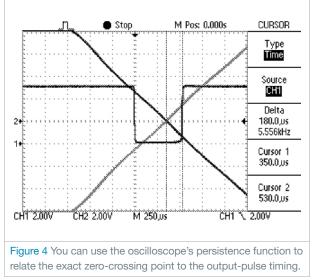

The classic Colpitts oscillator circuit in **Figure 1** generates a clock signal with a fixed duty cycle. By replacing CMOS inverter gate IC<sub>1A</sub> with a voltage comparator (**Figure 2**), you can obtain a more versatile and more useful clock generator. You can set not only the oscillation frequency but also the duty cycle. You must use the comparator in an inverting configuration, which introduces a 180° phase shift. That shift, along with an additional phase shift of 180° from the capacitor-input network, lets the circuit oscillate. The circuit com-

pares the sine wave at the output of the capacitor-filter network with the reference voltage, which drives the output of the threshold comparator high and low.

The network sets the oscillation frequency as follows:

$$f_{O} = \frac{1}{2\pi\sqrt{LC/2}},$$

where  $f_0$  is the oscillation frequency. With a suitable choice of the values of inductors and capacitors, the circuit can oscillate at frequencies as high as 10 MHz.

#### DIs Inside

48 Generate noisy sine waves with a sound card

48 Decode a quadrature encoder in software

51 Power an LED driver using off-the-shelf components

► To see all of *EDN*'s Design Ideas, visit www.edn.com/ designideas.

The output clock's duty cycle depends on the reference voltage, which you can easily set through the voltage divider comprising  $R_1$  and  $R_2$ . Unfortunately, the mathematical relationship between the reference voltage and the duty cycle is nonlinear because the sine wave at the output of the capacitor-input-filter network is not a linear function. Also, its amplitude is not constant but depends on the duty cycle of the output clock. You can easily obtain this mathematical relationship by testing the circuit with an inductance of 10  $\mu$ H and a capacitance of 10 nF.

You can use any high-speed compara-

## TABLE 1OSCILLATORDUTY CYCLE BASED ONREFERENCE VOLTAGE

| Reference<br>voltage (V) | Duty cycle (%) |

|--------------------------|----------------|

| 0.5                      | 15.2           |

| 1                        | 28.3           |

| 1.5                      | 37             |

| 2                        | 43.5           |

| 2.5                      | 50             |

| 3                        | 56             |

| 3.5                      | 62.6           |

| 4                        | 71.5           |

| 4.5                      | 85.4           |

tor with rail-to-rail inputs and outputs, such as the MAX987 from Maxim (www. maxim-ic.com), to achieve a wider input range for the reference voltage. That wider range gives you wider control of the duty cycle, although you can't reach the minimum duty cycle of 0% or the maximum duty cycle of 100%.

The propagation delay,  $T_{PD}$ , of the comparator introduces a further phase shift of value  $\Delta \phi = 2\pi f_{O} T_{PD}$ , where  $\Delta \phi$  is the phase shift. The capacitor-input network compensates for the phase shift, slightly reducing the oscillation

frequency. For safe operation of the circuit, you should vary the reference voltage by 0.5 to 4.5V. The duty cycle varies from approximately 15 to 85% (**Table 1**). You can produce a bipolar output signal if you use a dual power supply.EDN

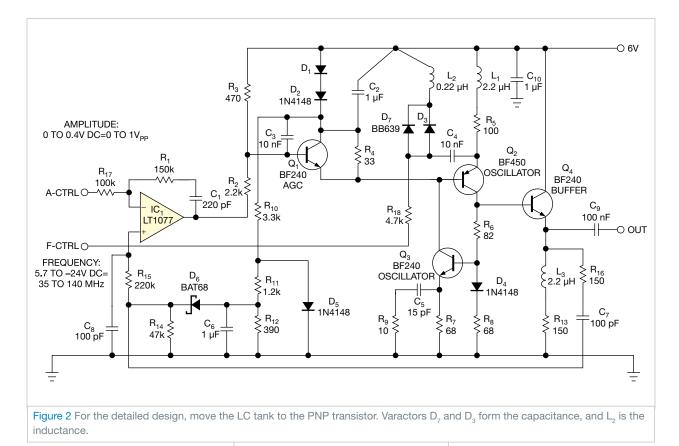

## Generate noisy sine waves with a sound card

José M Miguel, RF-Electronics Ltd, Barcelona, Spain

Testing audio-noise-reduction circuits, PLLs (phase-locked loops), and audio-frequency filters may require a noisy sine wave, one that is summed with white noise. Using a typical computer sound card, free software, and an external amplifier circuit, you can create a noisy sine wave.

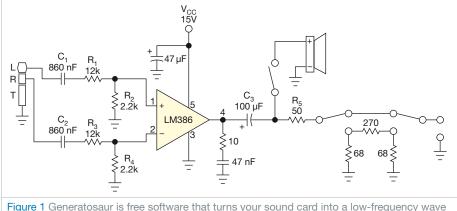

Free Generatosaur software from Wavosaur (www.wavosaur.com) turns your sound card into a low-frequency wave generator. It lets you independently choose amplitude, frequency, and waveform for the left and the right channels. The Generatosaur's user interface is a dialogue-box-style control panel (see **figure** at www.edn.com/110120dia). If you select a sine wave for the left channel and a white noise for the right channel, you then need only to use an amplifier to add the signals. **Figure 1** shows the complete circuit.

Figure 1 Generatosaur is free software that turns your sound card into a low-frequency wave generator.

The differential amplifier employs a National Semiconductor (www.national. com) LM386 audio power amplifier with a supply voltage of 15V. The output of the LM386 has a self-centered quiescent voltage that is half the power-supply voltage and that requires a blocking capacitor,  $C_3$ . Resistor  $R_5$  sets the output impedance to  $50\Omega$ . You need the voltage dividers  $R_1/R_2$  and  $R_3/R_4$  because the output-voltage range for a standard sound card is 0 to 2V. Taking into account that the voltage gain of the LM386 amplifier is internally set to 20 and that its output voltage range is 7V, you need an attenuation factor, K, of 7/(2×20) in each ampli-

> fier input. The circuit also includes a selectable 20-dB attenuator that you can invoke with the two DPDT (double-pole/ double-throw) switches.

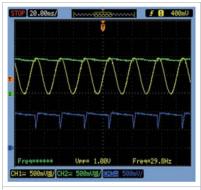

> Another **figure**, also available at www.edn.com/110120dia, shows a 450-Hz sine wave with a 10-dB SNR (signal-to-noise ratio). The root-mean-square noise voltage of this signal is 0.5V measured on an oscilloscope and following the tangential method. If you need to hear the generated noisy signal, connect a loudspeaker to the output of IC LM386.EDN

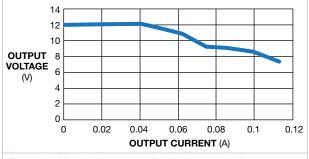

## Decode a quadrature encoder in software

Sid Levingston, Gentec-EO, Lake Oswego, OR

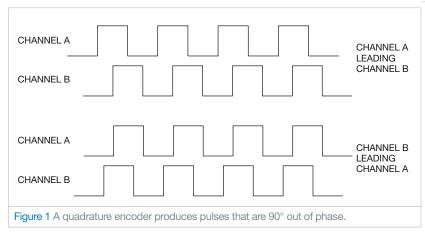

Quadrature encoders work in many applications to determine displacement and direction of mechanical travel. They vary in design, but they all do the same thing: supply a set of square waves 90° out of phase. Fig-

**ure 1** shows the typical output signals.

The encoder rotates clockwise when Channel A leads Channel B. If Channel B leads Channel A, the encoder is rotating counter clockwise. By counting the pulses and the direction of rotation, you can find the position of the encoder. Although ICs can decode quadrature encoders, you can easily and less expensively have the processor decode the signal. The signals from Channel A and Channel B go through a Schmitt trigger if necessary, but many encoders and processors include this trigger internally. The signals are then applied to two I/O pins on the processor that support edge-triggered inter-

rupts. The code in the interrupt handler implements a standard decoder algorithm, but all algorithms typically follow these steps:

1. Set up a state table like the one in **Table 1**. The table wraps around from State 3 to State 0.

2. Initialize a counter.

3. Measure the current state of Channel A and Channel B. Find that state in the table and set a pointer to it.

4. Enable the interrupts.

In the interrupt handler, use the following steps:

1. Read the state of Channel A and Channel B.

2. If the state is the one preceding the pointer, decrement the counter.

3. If the state is the one following the pointer, increment the counter.

#### LISTING 1 QUADRATURE-ENCODER CODE

```

#define CHA BIT0

#define CHB BIT1

```

```

initPort()

```

```

{

P1SEL = 0;

P1DIR = 0;

P1OUT = 0;

P1IES = 0; // rising edge.

P1IE = CHA + CHB; // interrupt on CH A or CH B rising edge

}

#pragma vector = PORT1_VECTOR

___interrupt void port1_ISR (void)

{

if(P1IFG & CHA ) // who interrupted? If A then A is high

{

(P1IN & CHB) ? gStepCount-- : gStepCount++ ; // test B

P1IFG &= ~CHA; // clear interrupt

}

if(P1IFG & CHB ) // who interrupted? If B then B is high

{

(P1IN & CHB ) ? gStepCount++ : gStepCount-- ; // test A

P1IFG &= ~CHB; // clear interrupt

}

}

```

#### TABLE 1 LOGIC STATES OF QUADRATURE ENCODER

|         | Channel A | Channel B |

|---------|-----------|-----------|

| State 0 | 0         | 0         |

| State 1 | 1         | 0         |

| State 2 | 1         | 1         |

| State 3 | 0         | 1         |

Set the pointer to the new state.

Clear the interrupt.

This method requires that a state table exists, that the previous state remain, and that the handler determine on each interrupt which of four states exists and then make a decision based on two possible conditions. The handler accomplishes this task with a fourcase switch, in which each case has two if conditions.

Now, consider what happens in the real world. If the I/O pin generates an interrupt on a rising edge, then when the interrupt happens, that channel goes from low to high. Therefore, there's no reason to read the state of the pin that interrupted. The other channel did not interrupt because the signals are 90° out of phase. So, to determine the current state, you need only to read the state of the pin that didn't initiate the interrupt. The state of the unchanged low or high signal tells which way the encoder rotated. If it is low, then the interrupting pin is leading. If it is high, then the interrupting pin is trailing. You can use these facts to implement an efficient interrupt handler with no state table and no memory of a previous state.

The code in **Listing 1** was tested on an MSP430F processor connected to an Encoder Products (www.encoder.com) model 15T. The encoder monitored the position of a linear stage. The stage traveled 85 mm and could be tracked with resolution of 5 microns.

The define statements (highlighted in red) make the code more readable. The initPort() function (highlighted in blue) sets up the rising-edge interrupt on channels A and B. The final piece is the interrupt handler (highlighted in green). Note that it contains only six lines of code compared with the 20 or 30 lines it would take to implement the traditional method of decoding the channels.EDN

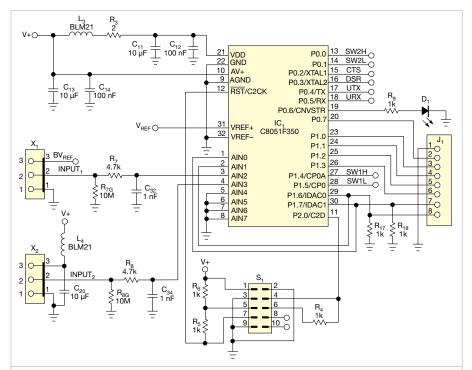

# Power an LED driver using off-the-shelf components

TA Babu, Chennai, India

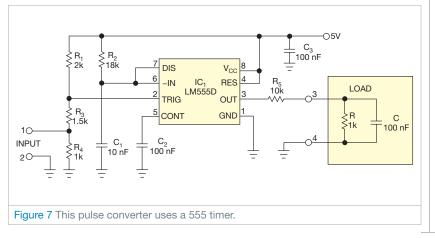

High-power LEDs challenge electronics engineers to design accurate and efficient, yet simple, driver circuits. Conventionally, driving highpower strings with accurate current requires dedicated switching regulators. Choosing a discrete driver circuit requires an understanding of LED lighting to make the best trade-off. This Design Idea describes a simpler and equally good way to employ the ubiquitous 555 IC.

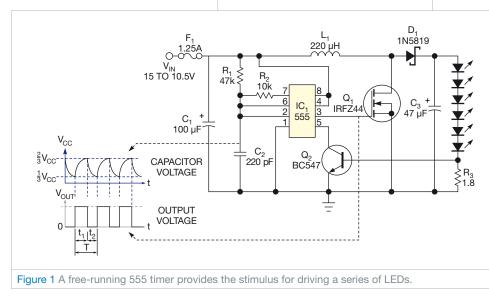

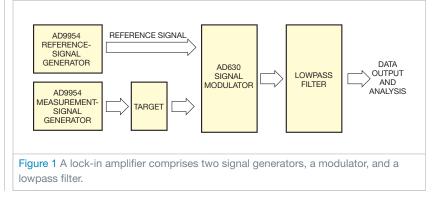

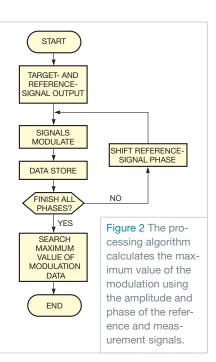

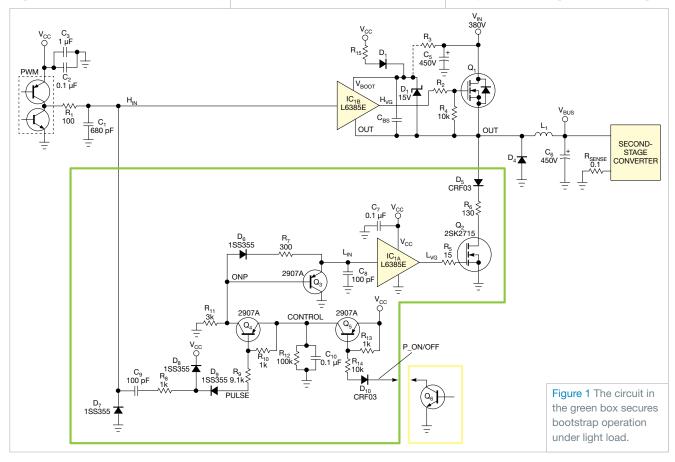

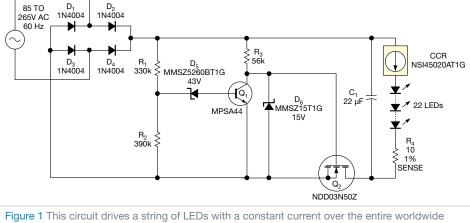

In the converter circuit in **Figure 1**, IC<sub>1</sub>'s pins 2 and 6 connect together, which lets the device retrigger itself on each cycle. Thus, it operates as a free-

#### ONCE THE VOLTAGE DROP REACHES THE BASE-EMITTER THRESHOLD OF TRAN-SISTOR Q<sub>2</sub>, IT STARTS CONDUCTING.

running oscillator. During each cycle, capacitor  $C_2$  charges up through timing resistor  $R_1$  and discharges through resistor  $R_2$ . The capacitor charges up to two-thirds of the power-supply

voltage, the upper comparator limit, which  $0.693(R_1C_2)$  determines, and discharges itself down to one-third the power-supply voltage, the lower comparator limit, which  $0.693(R_2C_2)$  determines. The total time period, T, is  $0.693(R_1+R_2)C_2$ .

During the on time, transistor  $Q_1$  conducts and stores the energy in inductor  $L_1$ . When it stops conduction, the stored energy transfers to capacitor  $C_3$  through Schottky diode  $D_1$ .

You can use the following **equations** to calculate the inductor value. The selection of an inductor depends on input voltage, output voltage, maximum current, switching frequency, and availability of standard inductor values. Once you know the inductance, you can choose the diode and the capacitor.

MOSFET  $Q_1$  determines the duty cycle, according to the following equation:

$$D=1-\frac{V_{INMIN}\times\eta}{V_{OUT}},$$

where  $V_{\text{INMIN}}$  is the minimum input voltage,  $V_{\text{OUT}}$  is the desired output voltage, and  $\eta$  is the efficiency of the converter, estimated at 80%.

The average inductor current is

$I_{LAVG} = \frac{I_O}{1-D}$

where  $I_{\rm LAVG}$  is the average inductor current and  $I_{\rm O}$  is the output current.

The peak inductor current is

$$I_{LPEAK} = I_{LAVG} + \frac{\Delta I_L}{2}$$

where  $I_{\text{LPEAK}}$  is the peak inductor current and  $\Delta I_{\text{L}}$  is the change in inductor current.

Assume that the change in inductor current is 25% over the average current. You can compute inductor  $L_1$  as

$$L=(V_{IN} \times D)/(F_{OSC} \times \Delta I_L),$$

where  $F_{OSC}$  is the oscillator frequency. The inductor's saturation-current rating should be greater than the peak current.

To ensure constant illumination, you must monitor the current through the LED. Resistor  $R_3$  senses the output current. Once the voltage drop across this resistor reaches the base-emitter threshold of transistor  $Q_2$ , it starts conducting, and this conduction reduces the on time of the 555 timer.

The following **equation** thus sets the LED current:

$$I_{LED} = \frac{0.6V}{R_{SENSE}}$$

where  $I_{\rm LED}$  is the LED's current and  $R_{\rm SENSE}$  is the sense resistance.

The minimum and maximum input and output voltages for this circuit are

10.5 and 15V, respectively. The LED string's voltage and current are 21V and 350 mA, respectively. The 6W LED driver can find numerous applications, including battery-operated portable lighting, solar-operated garden lighting, automotive lighting, bike headlights, and underwater lights. Driving highpower LED strings with standard off-theshelf components simplifies your design without sacrificing performance.EDN

# CESTO CONTRACTOR OF CONTRACTOR

## Compute a histogram in an FPGA with one clock

Mohit Kumar, Texas Instruments, Bangalore, India

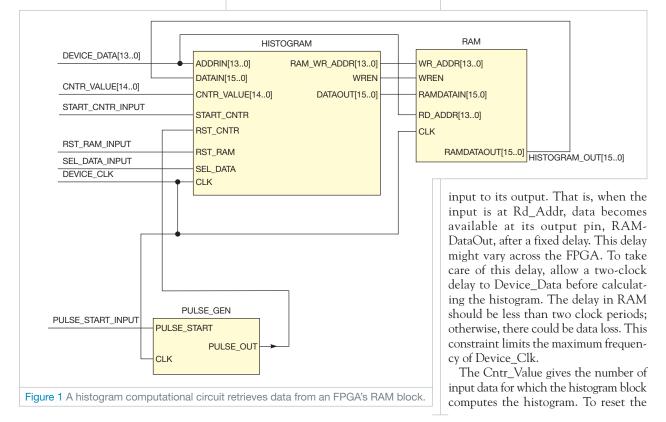

Histograms are often useful tools for analyzing digital data. To get reliable results from a histogram, though, you must collect large amounts of data, often with 100,000 to 1 million points. If you need to collect an ADC's digital outputs for analysis, you can use an FPGA (**Figure 1**).

The **figure** shows the histogram, RAM, and pulse-generator blocks, which let you capture and display the histogram computation based on 14bit data. The RAM block is the FPGA's built-in RAM, and the histogram block is the VHDL (very-high-level-designlanguage) code to compute the histogram. You can also download the VHDL code for this application from the online version of this Design Idea at www.edn. com/110203dia.

The 14-bit parallel data, Device\_ Data[13..0], from an ADC goes to the histogram block and to the RAM Rd\_Addr input. The RAM provides the data at its address location, RAM-DataOut[15..0]. This data loops back to the histogram block, which increments it by one and sends it to output pin DataOut[15..0], a 16-bit data output. When the WREN (write-enable) pin is

#### **DIs Inside**

44 Protect MOSFETs in heavy-duty inductive switched-mode circuits

46 Control an LM317T with a PWM signal

47 High-speed buffer comprises discrete transistors

48 Limit inrush current in high-power applications

► To see all of *EDN*'s Design Ideas, visit www.edn.com/designideas.

at logic level one, the data is written at the address at pin Wr\_Addr[13..0]. That approach is the same as if the data were coming from Device\_Data[13..0].

The RAM has a fixed delay from its

counter, the Pulse\_Gen block generates a pulse, which enters at input Rst\_Cntr. At this point, the histogram again computes the histogram for the next set of input data from Cntr\_Value. The Cntr\_Value is 15 bits, but you can increase it to collect more histogram data.

The signals Sel\_Data and Rst\_RAM reset the data stored in the FPGA's RAM. Whenever the high signal is at the Rst\_RAM pin, the DataOut pin of

the histogram block gives all bits as 0. When the high signal is at the Sel\_Data input pin of the histogram block, the output from RAM\_Wr\_Addr is not the Device\_Data but an internally generated ramp that ramps up from 0 to 16,384. The histogram block does no computation because doing so would reset the address of the RAM.

When the FPGA completes the histogram computation, the RAM can read the histogram data by selecting Sel\_ Data as logic high and keeping Rst\_ RAM as logic low. The data in the RAM address sequentially exits the output pin, and you can transfer the data to a PC. Because all the blocks run on a single clock, Device\_Clk, the design is simple and helps you meet timing constraints. You can easily modify the design to accommodate 16- or 12-bit data histograms.EDN

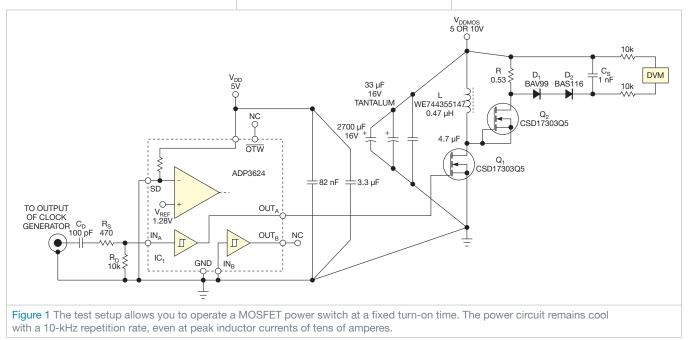

# Protect MOSFETs in heavy-duty inductive switched-mode circuits

Marián Štofka, Slovak University of Technology, Bratislava, Slovakia

The MOSFET power switch is commonly the most vulnerable part of a new switched-mode highpower circuit. One threat for this device is exceeding the value of the maximum allowed pulse current. You cannot exceed this limit, even for pulse durations as short as 10 nsec. You could still thermally damage the MOS-FET with a high duty cycle even when the drain-to-source current has a value between the peak and the dc ratings. The FET might eventually enter selfoscillations at a frequency, which might be an order of magnitude higher than your planned operating repetition rate. To protect the FET, you can limit the duty cycle by ac coupling the FET-driver circuit. If you further limit the repetition rate to tens of kilohertz, you needn't worry about thermal considerations.

To limit the duty cycle of the pulses, use the Schmitt-trigger input of  $IC_1$  (**Figure 1**). You pass the input-voltage waveform through a derivative circuit comprising  $C_D$ ,  $R_D$ , and  $R_S$ . The low-to-high transition of the clock causes an abrupt rise of voltage at resistor  $R_D$ . The output of the noninverting driver

therefore goes high. Immediately after this transition, the voltage on  $\rm R_{\rm D}$  starts to decrease exponentially. When it falls below  $\rm V_{TL}$ , the lower threshold of input IN<sub>A</sub>, output OUT<sub>A</sub> abruptly falls to 0V. The time constant (R<sub>D</sub>+R<sub>S</sub>+R<sub>GEN</sub>)×C<sub>D</sub> yields the rate of exponential decrease. R<sub>GEN</sub> is the output resistance of the generator of the input clock. You can calculate the value of capacitor C<sub>D</sub> using the desired pulse width, T<sub>p</sub>:

$$C_{D} = \frac{T_{P}}{R_{D} + R_{S} + R_{GEN}} \times \frac{1}{\ln \left[ \frac{V_{DD}}{V_{TL}} \times \frac{R_{D}}{R_{D} + R_{S} + R_{GEN}} \right]}$$

The equation employs an estimate of

the value of  $V_{TI}$ :

$$V_{TL} \simeq \sqrt{V_{INL} \times V_{INH}} - 0.1V = 1.165V.$$

The IC's data sheet gives the values of 0.8 and 2V as the limits of the low and high input voltages, respectively. The high-to-low transition of the clock has no effect. This transition causes a sharp negative exponential pulse, which an internal Schottky diode at input IN<sub>A</sub> suppresses. The anode of this internal diode connects to ground, and its cathode connects to input IN<sub>A</sub>. Resistor R<sub>S</sub> limits the peak current flowing through the protective diode to about 10 mA.

The IC has an output current of  $\pm 4A$ . The typical on-resistance of  $Q_1$  is 2 m $\Omega$ . You interconnect  $Q_2$ 's gate and source pins to create a freewheeling diode. This diode has a typical reverse-recovery time of 33 nsec at a 25A forward current. When  $Q_1$  turns off, the peak inductor current flows through  $Q_2$ . Voltage  $V_R$  occurs on power resistor R and is superimposed onto the supply voltage,  $V_{DDMOS}$ . The sum of these voltages must be lower than or equal to the manufacturer's specified value of the drain-to-source voltage of transistors  $Q_1$  and  $Q_2$ .

When testing the circuit, you should monitor the dc-supply current. You can calculate the ideal-case supply current as a function of supply voltage on the power section and the pulse period as follows:

$$I_{SID} = \frac{1}{2} \times \frac{V_{DDMOS} T_{PON}^2}{L}$$

$$\times f_{REP} = \frac{1}{2} I_{LPEAK} T_{PON} f_{REP}.$$

You calculate the pulse width of a single interval when the channel of  $Q_1$  is conductive as an approximation relating the rise, fall, on, and off times of the FET:

$$T_{PON} \simeq T_{P} + t_{DOFF} - t_{DON} + t_{DMOSOFF}$$

$$-t_{DMOSON} + (t_{R} + t_{F}) \times \left(\frac{1}{2} - \frac{V_{T}}{V_{DD}}\right).$$

The sum of differences in the propagation delays of IC<sub>1</sub> and Q<sub>1</sub> is positive and totals 32.1 nsec. V<sub>T</sub> is the gate-to-source threshold voltage of Q<sub>1</sub>. The data sheet gives a typical V<sub>T</sub> of 1.1V, and the supply voltage, V<sub>DD</sub>, has a value of 5V. These values yield 9.8 nsec for the last term of the preceding **equation**. T<sub>PON</sub> is thus larger by 41.9 nsec. For a good design, an ammeter will indicates a supply current one to 1.5 times the ideal value of the current.

You can check the peak voltage at load resistor R.  $D_1$  and  $D_2$  and storage capacitor  $C_S$  function as a peak detector. The peak-voltage pulses at resistor R cause a dc voltage at  $C_S$  of roughly the same value as the peak voltage. You

can determine the peak current flowing through the inductor from the voltage at the peak detector using the following **equation**:

$$I_{LPEAK} \simeq \frac{V_{RPEAK}}{R}$$

Set the auxiliary supply voltage at 5.078V, the supply voltage at 10V, and the clock-pulse repetition frequency to 11,387 Hz. This approach causes the supply's current to be 0.327A and the peak voltage to be 16.4V. The peak current of the inductor reaches 30.94A. The experimentally determined turn-on time is approximately 1.502 µsec.

The IC driver contributes to the protection of the MOSFETs with an undervoltage lockout. If the supply voltage is on, but the auxiliary supply voltage is off, a voltage could get from the  $IN_A$ pin through internal protective diodes to the  $V_{DD}$  pin. The undervoltage lockout disables the control outputs until the auxiliary supply's voltage reaches a typical value of at least 4.2V.

The 0.65-m $\Omega$  dc resistance of ferritecore inductor L might seem to be overrated for the circuit. However, the slope of current pulses in the inductor represents a megahertz-range equivalent frequency. The effective resistance at these slopes increases due to the skin effect and the proximity effect. This effective resistance can be many times the dc value.EDN

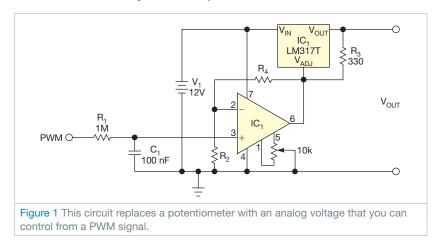

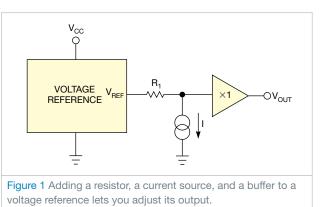

### Control an LM317T with a PWM signal

Aruna Prabath Rubasinghe, University of Moratuwa, Moratuwa, Sri Lanka

The LM317T from National Semiconductor (www.national. com) is a popular adjustable-voltage regulator that provides output voltages of 1.25 to 37V with maximum 1.5A current. You can adjust the output voltage with a potentiometer. The circuit in Figure 1 replaces the potentiometer with an analog voltage that you can control from a PWM (pulse-widthmodulation) signal. You control this signal with a microcontroller or any other digital circuit. You can use the same microcontroller to dynamically monitor the output and adjust the LM317T.

Using an RC lowpass filter and an op amp, you can convert the PWM signal to a dc level that can adjust the LM317T's voltage output. Varying the pulse width of the input signal lets you generate an analog voltage of 0 to 5V at the output of the lowpass filter. The op amp multiplies the voltage to achieve the desired voltage range.

For scenarios in which you must multiply the input voltage by two, the LM317T's adjustment pin receives 0 to 10V. Its output-voltage range is 1.25 to 11.25V. The equation  $V_{OUT}=V_{ADJ}+1.25V$  governs the LM3175T's output volt-

#### YOU CAN IMPROVE THE CIRCUIT BY REPLACING THE RC LOWPASS FILTER WITH AN ACTIVE FILTER.

age. You can change the op amp's gain by choosing proper values for  $R_4$  and  $R_2$ . You must be able to remove offset

voltages from the op amp. Use an op amp, such as a National Semiconductor LM741, with null adjustment. The selection of values for the capacitor and resistor for the RC lowpass filter depends on the PWM signal's frequency. This circuit uses values for a 1-kHz PWM signal.

You can improve the circuit by replacing the RC lowpass filter with an active filter and then feeding a feedback signal from the circuit's output into the microcontroller for dynamic adjustments.EDN

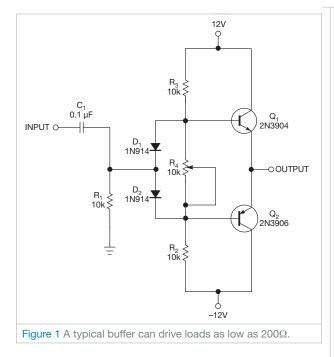

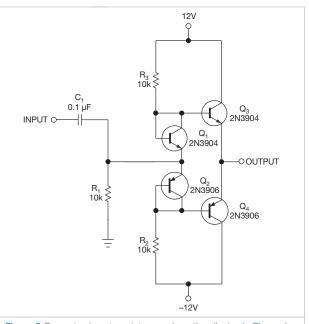

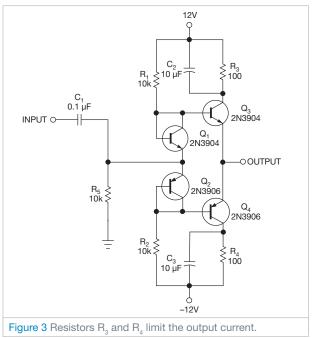

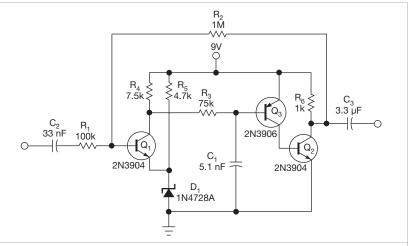

# High-speed buffer comprises discrete transistors

Lyle Russell Williams, St Charles, MO

Circuits sometimes need a gainof-one buffer to lower output impedance and prevent the load from interfering with the previous stage. For an application involving a 1.5-MHz, lowpower transmitter and antenna, a Burr Brown (www.ti.com) BUF634 buffer IC would work, but a discrete transistor buffer may be more convenient and less expensive than the IC. **Figure 1** shows the classic design of such a buffer. This circuit can drive a load as low as  $200\Omega$  with a peak output voltage of 2V. The maximum collector current of the transistors limits the output. You can use larger output transistors if your application requires more output current. Trimmer resistor R<sub>4</sub> across the diodes is, however, a relatively expensive part, and you must adjust it to produce the correct bias current for Class

AB operation. The adjustment is likely to drift over time.

A simpler circuit, such as the one in Figure 2, uses currentmirror transistors  $Q_1$  and  $Q_2$  instead of diodes. Resistors  $R_2$ and R<sub>4</sub> set the zero-signal bias current in the bias-transistor circuits. The current-mirror effect causes the current in the output transistors to be nearly equal to the current in the bias transistors—approximately 1.2 mA in this case.

Because the current-gain-bandwidth product of the 2N3904 and 2N3906 transistors is 300 MHz, this circuit should work at 100 MHz or higher frequencies. At these frequencies, however, the circuit layout may be critical, and the slew rate, which is unknown, may limit usefulness. The offset of the circuit is approximately 0.1V, which is not a problem for this application because the circuit uses capacitive coupling through  $C_1$ . If you use the buffer in the feedback loop of an op amp, the op amp can null the offset.

You may want to monitor the current in the output transistors, so the circuit in Figure 3 adds  $100\Omega$  resistors R, and  $R_4$  and 10-µF bypass capacitors  $C_2$  and  $C_3$  in the collectors of output transistors  $Q_3$  and  $Q_4$ . The voltage across these resistors reveals the collector currents, which are nearly equal in the two output transistors, and is close to the value that the values of  $R_1$  and  $R_2$  predicted.EDN

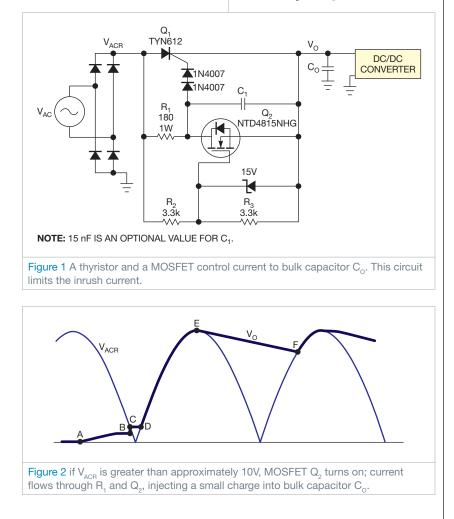

## Limit inrush current in high-power applications

JB Castro-Miguens, Cesinel, Madrid, Spain, and C Castro-Miguens, University of Vigo, Vigo, Spain

A high-power offline supply is | bridge dc/dc converter. Rectifying the ac nothing more than a half- or full-

line yields a dc voltage that feeds the

converter. At power-supply turn-on, the bulk capacitor of the uncontrolled rectifier is completely discharged. It results in a huge charging current for a high instantaneous line voltage because the discharged bulk capacitor temporarily short-circuits the diodes of the rectifier stage. The high inrush current can trigger a mains circuit breaker, burn a fuse, or even destroy a power supply's rectifier diodes unless you take precautions. The circuit in **Figure 1** limits the inrush current.

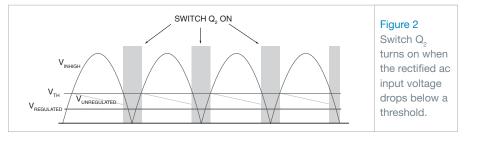

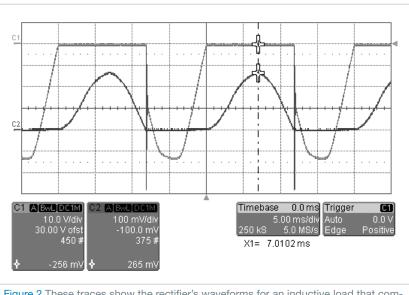

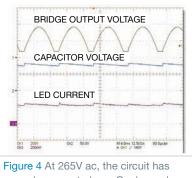

At turn-on, if the instantaneous rectified ac-line voltage,  $V_{ACR}$ , is greater than approximately 10V, Point A in **Figure 2**, MOSFET  $Q_2$  turns on, forcing thyristor  $Q_1$  off. In this situation, a little current flows through  $R_1$  and  $Q_2$ , injecting a small charge into bulk capacitor  $C_0$ , Path A to B in **Figure 2**.

When  $V_{ACR} - V_0 \le 8V$  or so, where  $V_0$  is the output voltage,  $Q_2$  is off, letting  $Q_1$  conduct. In this situation, the bulk capacitor receives the necessary charge through  $Q_1$ , Path B to C in **Figure 2**, to match  $V_0$  to  $V_{ACR}$ . After this point,  $V_{ACR}$  falls below  $V_0$ , and the bulk capacitor alone must support any power the dc/dc converter demands until  $V_{ACR} - V_0 \ge 5V$  or so, Path C to D in **Figure 2**. At Point D,  $V_{ACR} - V_0 \ge 5V$  and thyristor  $Q_1$  triggers, which conducts the capacitor's

charge current and the current the dc/dc converter demands until  $V_{\rm ACR}$  matches the sinusoidal peak at Point E.

When  $V_{ACR}$  falls, thyristor  $Q_1$  cuts off, and the bulk capacitor alone feeds the dc/dc converter. The thyristor conducts again when  $V_{ACR}$  matches  $V_0$  to the sinusoidal peak. This process then repeats. Use a nonsensitive gate thyristor with a breakdown voltage of at least 400V for an ac voltage of 220V rms (root mean square) and with twice the rms-current rating of the rectifier diodes.

This circuit uses a TYN610 thyristor. You can calculate the value of  $R_1$  using  $R_1$ =(6.8– $V_{GT}$ )/ $I_{GT-20^\circ}$ , where  $V_{GT}$  is the minimum gate-cathode voltage necessary to produce the gate-trigger current for  $Q_1$  and  $I_{GT}$  is the minimum gate current to trigger  $Q_1$  down to -20°C. The NTD4815NHG MOSFET is suitable for this circuit. A MOSFET with a different threshold voltage may require different values for  $R_2$  and  $R_3$ .EDN

# CESTO CONTRAR CARANTELE AND FRAN GRANVILLE READERS SOLVE DESIGN PROBLEMS

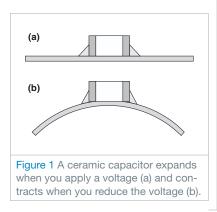

# Reduce acoustic noise from capacitors

Damian Bonicatto, Landis+Gyr, Pequot Lakes, MN

Some surface-mount capacitors exhibit acoustic noise when operated at frequencies in the audio range. A recent design uses 10-µF, 35V X5R 1206 ceramic capacitors that produce noticeable acoustic noise. To quiet such a board, you can use acoustically quiet capacitors from manufacturers such as Murata (www.murata.com) and Kemet (www.kemet.com). Unfortunately, they tend to cost more than standard parts. Another option is to use capacitors with a higher voltage rating, which could reduce the noise. Those parts may also be more expensive than standard capacitors. A third path is to make a physical change to the PCB (printedcircuit board).

A ceramic capacitor expands when you apply a voltage and contracts when you reduce the voltage. The PCB flexes as the capacitor changes size because the ends of the capacitor mechanically couple to the PCB through solder (**Reference 1**).

Figure 1a shows a capacitor with no applied voltage, and Figure 1b shows an exaggerated condition of PCB flexing when you apply voltage to a ca-

pacitor. Applying the voltage makes the PCB operate as a speaker. Keeping that fact in mind, consider two methods for improving the situation. The first technique is relatively simple: If your circuit uses one capacitor, replace it with two in parallel, each with half the capacitance of the noisy capacitor. This approach lets you place a capacitor on top of the board and the other on the bottom of the board; the capacitors lie directly above each other, and their orientations are the same. As the upper capacitor tries to flex the board down, the lower capacitor tries to flex the board up. These two stresses tend to cancel each other, and the PCB generates little sound.

Adding a second capacitor increases cost but not as much as replacing the noisy capacitor with one that might not create noise. A ceramic capacitor from Digi-Key (www.digikey.com) sells

#### **DIs Inside**

50 Function generator has variable frequency

52 Power supply accepts wide input-voltage range

55 Circuit lets you test capacitors

► To see all of *EDN*'s Design Ideas, visit www.edn.com/design ideas.

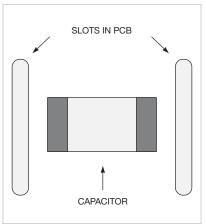

for approximately 27 cents (1000). A quieter KPS-series part from Kemet costs approximately \$1.50. The second method involves making a slot in the PCB near each end of the capacitor (**Figure 2**). When the capacitor expands and contracts, it flexes only a small portion of the PCB, which should reduce the noise.

A test with five 10-µF, 25V ceramic capacitors connected in parallel showed that putting three capacitors on top of the PCB and two on the bottom reduces the noise by 14 dBA (acoustic decibels). Routing a slot on both sides of the five capacitors reduces the noise by 15 dBA. Both are substantial noise reductions. A Murata JG8-series capacitor reduces the noise by 9.5 dBA. Combining these techniques should further reduce the noise.EDN

#### REFERENCE

Laps, Mark; Roy Grace, Bill Sloka, John Prymak, Xilin Xu, Pascal Pinceloup, Abhijit Gurav, Michael Randall, Philip Lessner, and Aziz Tajuddin, "Capacitors for reduced microphonics and sound emission," *Electronic Components, Assemblies, and Materials Association, Capacitor and Resistor Technology Symposium Proceedings*, 2007, http://bit.ly/eKyPKR.

# Function generator has variable frequency

Adolfo Mondragon, Electrolux Products, Juarez, Mexico

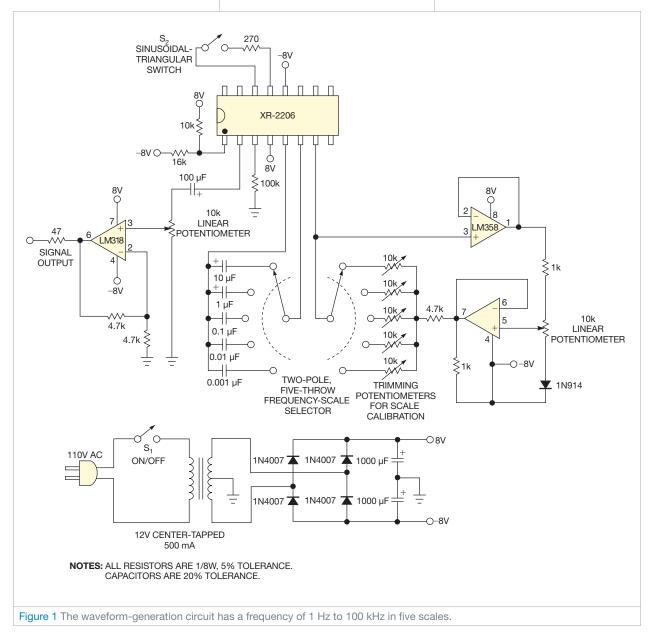

The Exar (www.exar.com) XR-2206 function-generator IC can generate square, triangular, and sinusoidal signals with low distortion. Its output frequency is inversely proportional to the components in an RC network, according to the formula F=1/RC.

Use a potentiometer as the resistor component to provide a frequency variation similar to a logarithmic scale. To change this behavior, the manufacturer's data sheet recommends connecting a resistor network to a variable external voltage source. The voltage should be stable and vary from 0 to almost 3V.

Instead of using an external voltage, the circuit described here uses an inter-

nal reference voltage of approximately 3V at Pin 7 of the XR-2206. With this internal reference, the circuit requires no voltage regulators—not even in the power supply. The circuit requires a power supply with only a 12V, 500-mA center-tapped transformer, a bridge rectifier, and two filter capacitors (Figure 1). You can define the frequency equations using Figure 2 as a reference.

When  $V_x$  is 0V, you determine the frequency using F=1/RC. The current trough,  $I_R$ , equals 3/R, where 3 is the voltage reference in Pin 7. From this **equation** and resolving the recipro-

cal of R, you define the frequency as  $I_R/3R=1/R$ , as a function of the current,  $F=I_R/3C$ .

When  $V_x$ >0V, you define the current as  $I_R = (3-V_x)/R$ . Replacing  $I_R$  from the previous **equation**, you can define the frequency as a direct function of the voltage: F=(1/3RC)(3-V\_x).

**Figure 1** shows the final circuit to generate the waveforms. The circuit's frequency ranges from 1 Hz to 100 kHz in five scales. The rotary switch lets you select the scale by switching in a set of capacitors.EDN

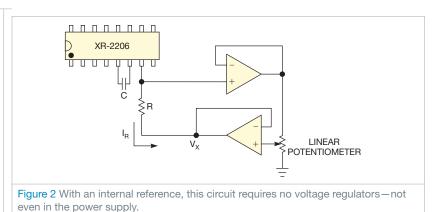

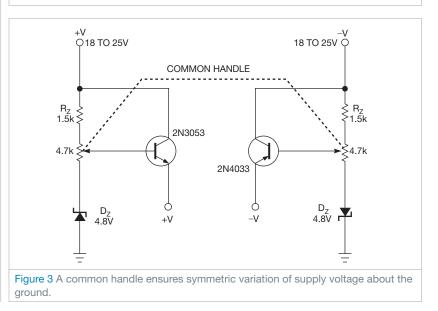

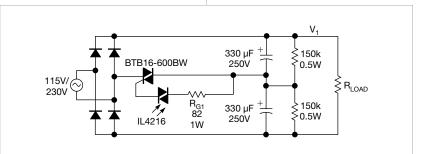

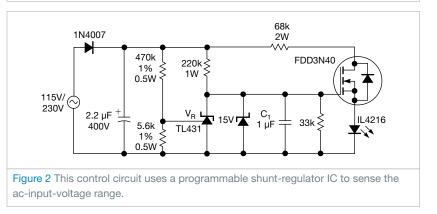

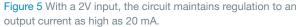

## Power supply accepts wide input-voltage range

Jim Windgassen, Northrop Grumman Undersea Systems, Annapolis, MD

**The switching power supply in Figure 1** produces 3.3V dc from an input voltage of 2.5 to 20V dc with high efficiency. The circuit operates at an input voltage as low as 1.5V once it starts from a minimum of 2.5V dc, allowing the switcher to fully discharge a pair of alkaline cell batteries nearing end of life. The power supply can also run efficiently off higher input voltages, such as 12V automotive power. The heart of the circuit is a SEPIC (single-ended-primary-inductance-converter)-based switching power supply, which provides an output voltage greater than or less than the input voltage (**Reference 1**).

This power supply includes bootstrap circuitry comprising IC<sub>1</sub>, an LT3008

voltage regulator; Schottky diode D<sub>1</sub>; and capacitor  $C_2$ . It needs a minimum of 2.5V to start. Voltage regulator IC, provides 2.5V to start SEPIC controller IC<sub>2</sub>. Once the output voltage of the SEPIC power supply reaches its normal output voltage of 3.3 V, D<sub>1</sub> lets the output power of the switcher flow back to power IC<sub>2</sub>. Once this action occurs, IC<sub>1</sub> drops out of the circuit because the voltage at its output is above its setpoint voltage. The converter's own output now powers IC<sub>2</sub>, and the regulator's internal circuitry prevents backflow of power through IC<sub>1</sub>. MOSFET  $Q_1$  has low threshold voltage, appropriate on-resistance to provide current feedback to IC2, and a maximum

drain-to-source voltage of 30V to allow for operation up to a 20V input.

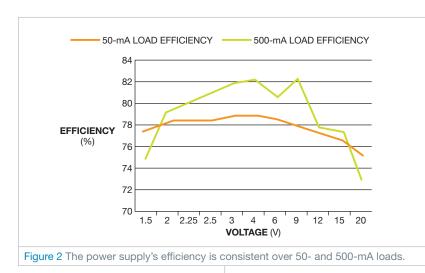

The bootstrap circuit allows the converter to run from very low input voltages by maintaining the input voltage to  $IC_2$ , and it increases efficiency at high input voltages by eliminating the use of  $IC_2$ 's internal linear voltage regulator. **Figure 2** shows the efficiency of the prototype power supply at both 50- and 500-mA loads. The power supply's efficiency is consistent over a range of operating voltages because of the bootstrapping circuit.

Because the circuit uses a low-threshold-voltage MOSFET, the switch, keeping the gate drive voltage low, reduces the total charge that must go into and out of the MOSFET gate, further improving efficiency. SEPIC controller  $IC_2$ normally uses its internal low-dropout capability to generate an operating voltage of 5V from the input. Running  $IC_2$ from the bootstrapped output reduces  $IC_2$ 's operating voltage to approximately 3V, which also limits the drive voltage to  $Q_i$ 's gate.

Table 1 lists the key components for the power supply, including an appropriate commercially available coupled inductor. The PCB (printed-circuitboard) design and the choice of coupled inductors for this power supply are critical for good performance. For the power supply to achieve high efficiency at low input voltages and high output current, the coupled inductor must have low-resistance windings, and the high current tracks should use wide copper pours to minimize resistance

Figure 3 The complete power supply fits onto a 23×15×3.5-mm PCB.

| TABLE 1 KEY PARTS FOR POWER SUPPLY |                                                                   |                         |                  |

|------------------------------------|-------------------------------------------------------------------|-------------------------|------------------|

| Component                          | Description                                                       | Manufacturer            | Part             |

| Input capacitor                    | 22-μF, 25V, 10%-tolerance,<br>1210-size X5R ceramic<br>capacitor  | AVX                     | 12063D106KAT2A   |

| Output capacitor                   | 100-μF, 6.3V, 1206-size X5R<br>ceramic capacitor                  | Kemet                   | C1206C107M9PACTU |

| Coupled inductor                   | 4.7-μH coupled-inductor<br>Cuk SEPIC                              | Würth                   | 744878004        |

| Bootstrap low-dropout regulator    | Regulated-low-dropout-<br>adjustment, 20-mA,<br>6-DFN-packaged IC | Linear Technology       | LT3008EDC#TRMPBF |

| SEPIC controller                   | 10-MSOP-packaged current-mode-IC controller                       | Linear Technology       | LTC1871EMS#PBF   |

| MOSFET                             | 30V, 5A, N-channel<br>microMOSFET                                 | Fairchild Semiconductor | FDMA430NZ        |

| Bootstrap diode                    | SOD-523-packaged, 40V<br>Schottky diode                           | Diodes Inc              | ZLLS350TA        |

| SEPIC diode                        | 2A, 30V Schottky<br>power diode                                   | Diodes Inc              | DFLS230L-7       |

losses and unwanted inductance.

A prototype of the power supply measures 23×15×3.5 mm (Figure 3). It uses a custom coupled inductor, but you can choose from many off-theshelf coupled inductors available from BH Electronics (www.bhelectronics. com), Coilcraft (www.coilcraft.com), and Wurth Elektronik (www.we-online. com). You can download the Linear Technology LTSpice code for this circuit from the online version of this Design Idea at www.edn.com/110217dia.EDN

#### REFERENCE

"Designing a SEPIC Converter," Application Note 1484, National Semiconductor, April 30, 2008, http://bit.ly/ich5pf.

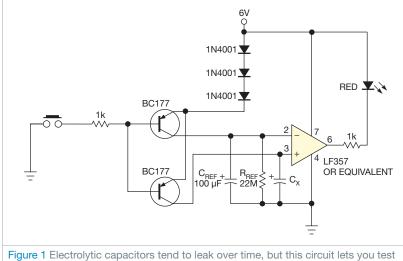

### Circuit lets you test capacitors

#### Raju R Baddi,

Tata Institute of Fundamental Research, Maharashtra, India

Electrolytic capacitors tend to leak with time. The circuit in Figure 1 lets you test capacitors and decide whether they're worth using. You can set the constraint on the leakiness through the values of  $C_{REF}/R_{REF}$ . The values in the figure are typical for general testing of all capacitors, from 1-nF ceramic versions to 1000- $\mu$ F electrolytic types. The value of  $C_{REF}$  in the circuit is near the value of the test capacitor,  $C_{X}$ . You can also choose  $R_{REF}$  by a rotaryswitching arrangement, to be greater than or less than 22 M $\Omega$ .

When the pushbutton switch closes, capacitors  $C_{REF}$  and  $C_X$  charge through their respective PNP transistors. When the switch opens, the capacitors begin to discharge.  $C_{REF}$ , assuming that it is in good condition, has an additional discharge external resistance,  $R_{REF}$ . The ca-

pacitor under test,  $C_{\chi}$ , discharges through its internal resistance. If the leakage in  $C_{\chi}$ is greater than that of  $C_{\text{REF}}$  through  $R_{\text{REF}}$ , then its voltage will fall faster. Thus, the voltage at the op amp's noninverting input will be lower than at its inverting input, forcing the op amp's output low and lighting the red LED. This LED indicates that the test capacitor leaks. Testing of the circuit reveals that even a 1-nF ceramic capacitor holds against the reference. Check the voltage rating on the test capacitor to make sure that it is higher than the voltage to which it will be charged—in this case,  $V_{\text{SUPPLY}}$  is –1.8V.

The LF357 has a minimum supply voltage of 10V, but the testing took place at only 6V to allow a low upperlimit voltage for the test capacitor. Make sure the capacitor has a FET or a MOS-FET input stage.EDN

them and decide whether they're worth using.

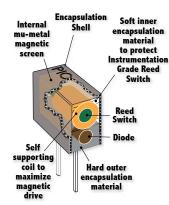

## Pickering Reed Relays

#### Need Instrumentation Grade Reed Relays? Look No Further

Pickering Electronics is a Manufacturer of high quality Reed Relays for:

Instrumentation

pickering

- Automatic Test Equipment (ATE)

- High voltage switching

- Low thermal EMF

- Direct drive from CMOS

- RF switching and other specialist applications.

#### Only Pickering has SoftCenter™ Technology

Pickering Reed Relays are encapsulated using a soft inner material to protect the reed switch capsule. The very hard compounds used by most other manufacturers can cause stresses that can potentially damage the reed switch and degrade contact resistance stability and life expectation. Go to www.pickeringrelay.com to find out more....

### pickeringrelay.com

# CESTOS CONTRACTOR SOLVE DESIGN PROBLEMS

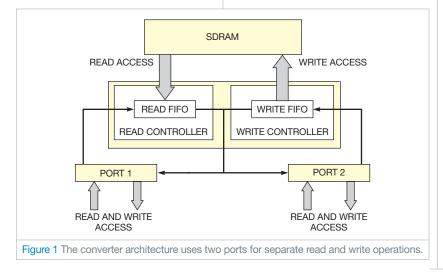

## Design provides single-portto-dual-port SDRAM converter

Yu-Chieh Chen, Instrument Technology Research Center, National Applied Research Laboratories, Hsinchu, Taiwan

In multimedia and video applications, DRAM buffers large frames in the image coding and decoding between an image-sensing device and an image-display device (references 1 and 2). It also plays a key role in imageframe-rate converters by matching the displaying format of the monitor (Reference 3). Accessing dual-port SDRAM is a complex task, especially when two data read or write operations are occurring simultaneously into a single-port SDRAM during high-speed operation.

SDRAM supports asynchronous control, performs reading and writing operations, and allows multiple CPUs to read or write in parallel. To reduce production costs and avoid complexity, engineers typically prefer conventional oneport SDRAM. You can, however, use an FPGA to convert a single-port SDRAM to function as a dual-port SDRAM.

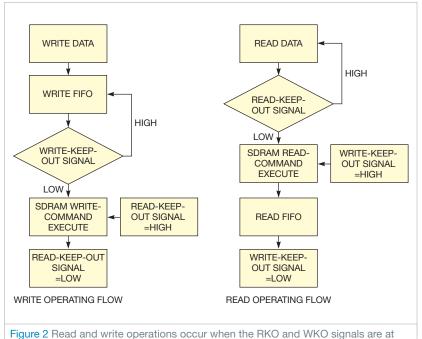

The single-port-to-dual-port SDRAM converter comprises two read-FIFO (firstin/first-out) and write-FIFO memory

blocks. A pair of read and write controllers each control a read-and-write data bus. Figure 1 shows the architecture of the proposed converter, and Figure 2 shows the operating flow of the read-andwrite controller. The write controller first stores the writing data in write-FIFO and executes the SDRAM write command when the WKO (write-keep-out) signal falls to a low level, which means that the read operation is complete. Meanwhile, the RKO (read-keep-out) signal goes high until the write operation is complete. The procedure prevents the read signal from occurring during the writing operation.

The read-data operation is similar to the write-data operation. The read controller first waits for the RKO signal to fall low if it is high when the read operation starts. The read controller then executes the read command and stores the data from SDRAM to read-FIFO memory. The read controller simultaneously pulls the WKO signal high until

#### **DIs Inside**

46 Zener diode protects FPGA inputs

48 Bicolor LED indicates 10 states

50 Relay driver switches two relays with one pin

► To see all of *EDN*'s Design Ideas, visit www.edn.com/ designideas.

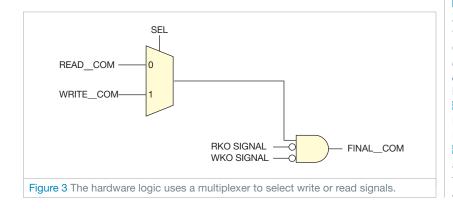

the read operation is complete. **Figure 3** shows the hardware logic of the smart controlling strategy, which the following **equation** also describes:

$$F_{COM} = $$[MUX_{READCOM,WRITECOM} \times \overline{RKO} \times \overline{WKO}],$$

where MUX is the multiplexer. For the read example, the SEL (select) signal switches to the read mode and then waits for the RKO signal to fall low if the RKO signal is at a high level when the read command executes (**Reference 1**).

This strategy doubles the high-level period of both the read operation, or RKO signal, and write operation, or WKO signal. These signals rise to logic high before executing each read or write operation. This step ensures that the read operation does not interrupt the write operation and that the write operation does not interrupt the read operation.

Figure 4, available with the Web version of this Design Idea at www.edn. com/110303dia, shows the simulation waveform of the converter, which is a part of the image-sensing and -displaying sequence. The iSDRAM\_Read signal is high, indicating that the SDRAM is performing a read operation. At the same time, the iSDRAM\_Write signal is high during the SDRAM-writing op-

logic-low states.

eration. The iSDRAM\_ReadKeepOut signal goes high before each iSDRAM\_ Write signal and lasts two times longer than each iSDRAM\_Write signal. This setup ensures that the writing command does not execute during the read operation. For the same reason, the read command doesn't execute during the writing operation.

The write-clock operation is initially ahead of the read-clock operation. After several time delays, however, the write-clock operation catches up with the read-clock operation. At this point, the controller holds the data and waits until the iSDRAM\_ReadKeepOut command falls to a low level before executing the read command. Using this read-and-write strategy, the controller resolves the conflict of executing read and write or read operations.EDN

#### REFERENCES

Zhu, Jiayi; Peilin Liu; and Dajiang Zhou, "An SDRAM controller optimized for high definition video coding application," *Proceedings of the IEEE 2008 International Symposium on Circuits and Systems*, May 2008, pg 3518, http://bit.ly/h6xaz0.

Jack, Keith, *Video Demystified*, Fifth Edition, Newnes Publishers, 2007, ISBN: 0750683953.

Yim, Myung-Sik, "Image decoding apparatus having frame rate transformation function," US Patent No. 5917950, June 29, 1999, http://bit.ly/i4GR98.

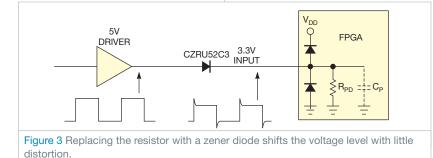

## Zener diode protects FPGA inputs

Rick Collins, Arius, Frederick, MD

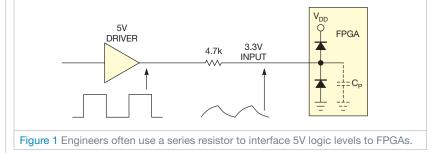

Although 5V-powered logic is still common in many applications, most FPGAs support interface levels of 3.3V and lower. When you connect an FPGA to higher voltage levels, the FPGA's application notes commonly suggest that you use the PCI (Peripheral Component Interconnect)bus clamp diodes in the FPGA's I/O blocks with an external series-limiting resistor to prevent damage to the FPGA (**Figure 1**). The PCI clamp diode limits the voltage to a level that doesn't harm the input, and the resistance value limits the current to a safe level that doesn't harm the PCI clamp diode. This approach works well in designs with low-speed signals.

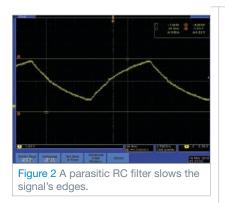

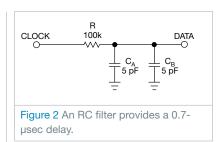

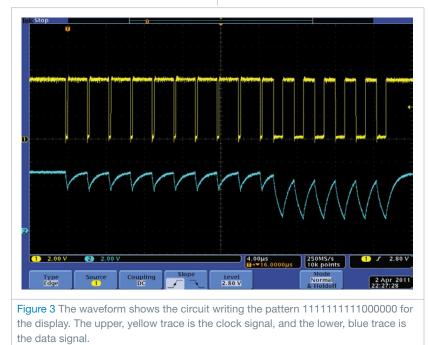

However, when you use this approach with a higher-rate signal, the effects of the parasitic RC filter distort the signal

(Figure 2). The circuit from the FPGA's application notes requires a change, which you can accomplish without redesigning the PCB (printed-circuit board). In this case, substituting a zener diode for the resistor shifts the signal level without causing excessive distortion (Figure 3). The zener diode works with the PCI clamp diode and the internal pulldown resistor to set the voltage level at the input pin.

To set the static level at the input pin, you must enable the FPGA's internal pulldown resistor to prevent the PCI clamp diodes from being driven too hard when the input is continuously high. The current from the pulldown resistor is smaller than the rating current of the zener diode. Low-voltage zener diodes also have round "knees" in the avalanche IV (current-to-voltage) curve. This curve results in a zener voltage that's lower than the rated value, so you need to use a higher-voltage zener diode. The diode should also have a low capacitance. The CZRU52C3, a 3V zener diode from Comchip (www.comchip. tw.com), works well, reducing the circuit's voltage by 2V (Figure 4).

Some parasitic effects in the zener diode will create other distortion to the waveform. The parasitic capacitance of the diode causes the diode to initially look like a short to the signal edges from the 5V driver. The FPGA pin will see a

Figure 4 An oscilloscope trace shows the signal with overshoot.

high-voltage overshoot for approximately 10 nsec, quickly decaying to the rated level of the input pin. The RC time constant of the pin capacitance and the pulldown resistance result in a slower drop to the final value, which the zener diode and the pulldown resistance determine. **Figure 5** shows a detailed view of the leading edge.EDN

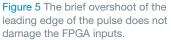

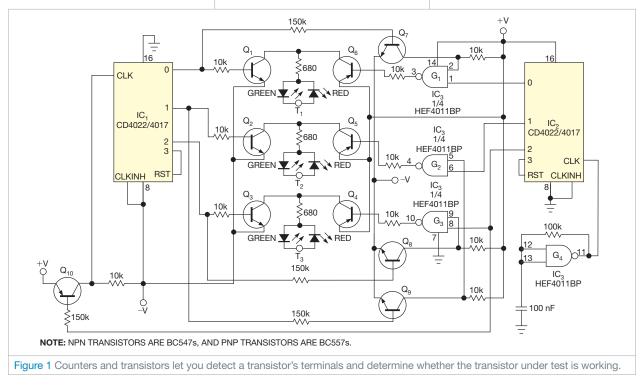

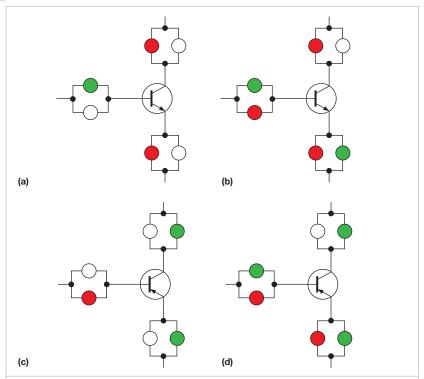

## **Bicolor LED indicates 10 states**

Abel Raynus, Armatron International, Malden, MA

Most microcontroller-based devices have several states of operation. Pushbutton switches often control these states. To minimize costs, many designs use only one switch; the number of presses sets the microcontroller's state. In the circuit in this Design Idea, lighting an LED indicates the chosen state.

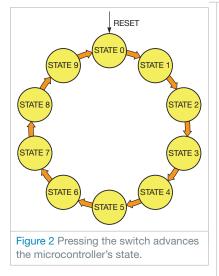

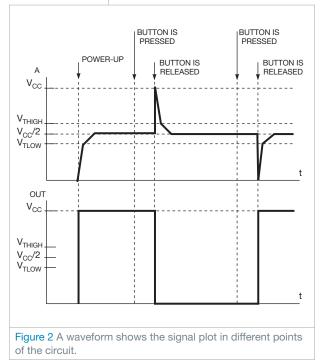

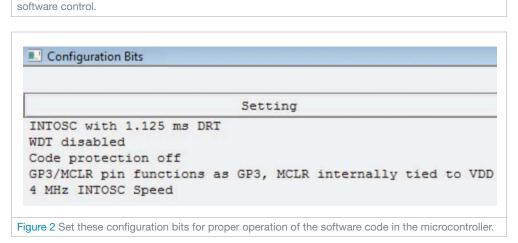

A large selection of bicolor LEDs is on the market in various shapes and colors from Kingbright (www.kingbrightusa.com), Optosupply (www. optosupply.com), and other suppliers. These LEDs provide new opportunities to use just one LED to indicate 10 states. You set the states by pressing a pushbutton switch that connects to a microcontroller's external interrupt pin (**Figure 1**). After each push, the interrupt subroutine sets the device to the next state (**Figure 2**).

State 0 is standby mode with the LED off. The device waits for you to press a switch. The LED's color indicates the next three states. For example, a Kingbright WP5A9EGW12.3SF LED yields red, green, and orange. Add

blinking to indicate the remaining states. You can independently control the red and the green LEDs, yielding six more combinations of indication (**Table 1**).

Using the microcontroller's internal oscillator as a clock source simplifies the circuit because the oscillator needs no external components and its 5% toler-

| TABLE 1 COLOR AND BLINKING PATTERNS FOR 10 STATES |         |           |                        |

|---------------------------------------------------|---------|-----------|------------------------|

| State                                             | Red LED | Green LED | Indication             |

| 0                                                 | Off     | Off       | No light (standby)     |

| 1                                                 | On      | Off       | Red                    |

| 2                                                 | Off     | On        | Green                  |

| 3                                                 | On      | On        | Orange                 |

| 4                                                 | Blinks  | Off       | Red blinks             |

| 5                                                 | Off     | Blinks    | Green blinks           |

| 6                                                 | Blinks  | Blinks    | Orange blinks          |

| 7                                                 | On      | Blinks    | Red and orange blink   |

| 8                                                 | Blinks  | On        | Green and orange blink |

| 9                                                 | Blinks  | Blinks    | Red and green<br>blink |

ance is sufficient for this application. Firmware sets the built-in pullup resistor for external interrupt input.

The clock speed and the values of the prescaler and time-counter-modulo registers determine the rate of LED blinking. The internal oscillator generates a 12.8-MHz clock, resulting in a 3.2-MHz bus frequency, with one cycle equal to  $0.3125 \mu$ sec. By choosing a prescaler value of 64, a time-counter-modulo register can calculate a cycle of 50 times the timer period in milliseconds. For example, for 1 second of blinking, you should set the time-counter modulo to 50,000, or \$C350 in hexadecimal.

Using tables rather than polling in programming allows you to significantly reduce the size of firmware (**Reference** 1).You can download firmware assembly code from the online version of this De-

sign Idea at www.edn.com/110303dib. This method is applicable to any microcontroller. You can even increase the number of indicated states by using different blinking rates.EDN

#### REFERENCE

Raynus, Abel, "Tables ease microcontroller programming," *EDN*, April 22, 2010, pg 76, http:// bit.ly/brXaq7.

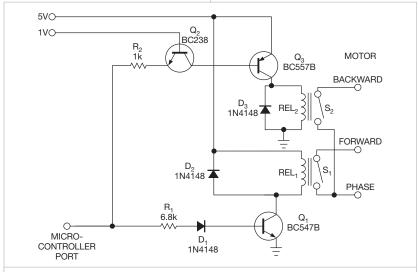

# Relay driver switches two relays with one pin

Gunther Kraut, PhD, Egmating, Germany

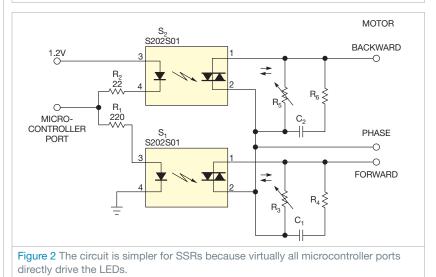

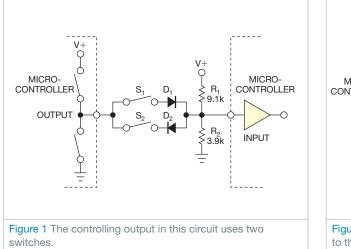

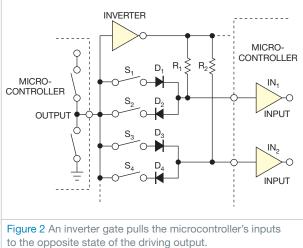

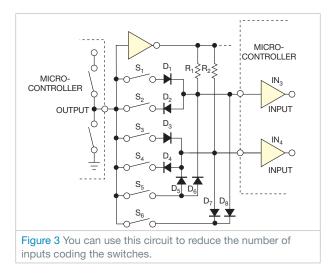

Independently switching two loads, such as relays, usually requires two microcontroller-I/O ports. Two ports let you control the loads so that you can switch them both off, switch them both on, or switch one on and the other off. If you don't need both relays on at once, you can control the remaining three states using only one port. You can also use a port's high-impedance state to control the relays.

You can, for example, use this application to control a motor. The motor's rotational direction depends on which of its two phase lines you select. This approach works with either classic electromechanical relays or SSRs (solid-state relays). If both relays are open, the motor is off. For electromechanical relays, you can use the driver circuit in Figure 1. Setting the microcontroller pin to logic one causes  $Q_1$  to turn on relay  $\text{REL}_1$ , and the motor runs forward. Setting the pin to a logic zero turns on  $Q_2$ , which turns on  $Q_3$ . This action closes the switch of REL<sub>2</sub> and causes the motor to run in the opposite direction. If the microcontroller port is in a high-impedance state,  $Q_1$ ,  $Q_2$ , and Q<sub>3</sub> cannot deliver current because the constant voltage of 1V at the base of  $Q_{2}$  is too low to reach the threshold of the base-emitter junctions of  $Q_1$  and  $Q_2$ plus the diode drop of D<sub>1</sub>. Both relays are off, and the motor is off. The supply voltage through a voltage divider or an emitter-follower circuit can provide the constant voltage of 1V. Free-wheeling diodes  $D_2$  and  $D_3$  prevent the collectors of  $Q_1$  and  $Q_2$  from overvoltage when the relay's coils are off. You can use almost any small-signal NPN and PNP transistors in this circuit. The selection of diode D<sub>1</sub> is also not critical.

The circuit is simpler for SSRs because

virtually all microcontroller ports directly drive the LEDs (**Figure 2**). A logic one supplies the LED in  $S_1$ , whereas a logic zero supplies the LED in  $S_2$ , making the corresponding TRIAC (triode-alternating-current) switches conductive. If the port is in the high-impedance state, no current can flow through the LEDs because the constant dc voltage of 1.2V is below the sum of the threshold voltages of the LEDs. Voltage-dependent resistors  $R_3$  and  $R_5$  and snubber circuits  $C_1$ ,  $R_4$ ,  $C_2$ , and  $R_6$  protect the SSRs. These protection circuits' values depend on the respective load.EDN

# CESTOR CONTRACTOR SOLVE DESIGN PROBLEMS

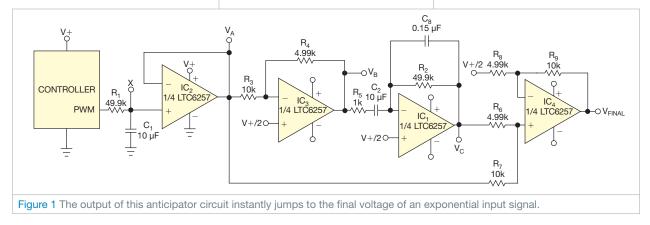

# Anticipator circuit speeds signal settling to a final value

Tim Regan, Linear Technology, San Jose, CA

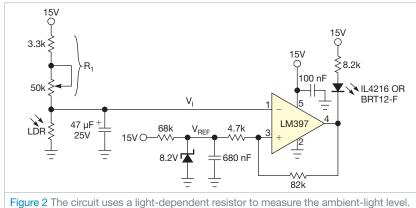

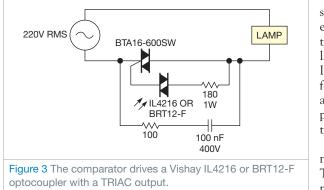

The circuit in this Design Idea anticipates, or jumps instantly to, the final voltage of an input-signal change. It relies on the fact that the intended input signal changes exponentially with a known time constant. This circuit was adapted from a 1970s-era instant-reading electronic thermometer, which displayed a patient's body temperature within seconds after a thermometer probe was placed under the patient's tongue. It exploits the fact that the temperature probe's exponential thermal response-time characteristic is known.

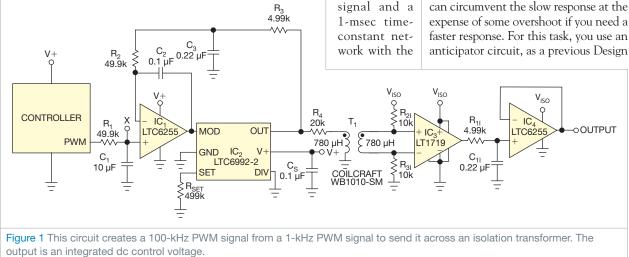

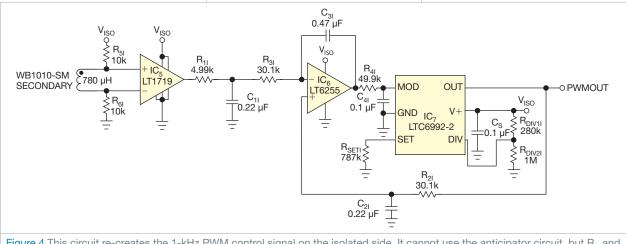

The circuit uses a quad rail-to-rail amplifier to perform a mathematical operation (**Figure 1**). The input to the circuit is at Node X. At that node, a filter with a 500-msec RC time constant averages a 1-kHz PWM (pulse-widthmodulated) signal. The desired output is a dc voltage proportional to the PWM duty cycle. A long time constant is required to reduce ripple. You obtain an instant output response by differentiating this input signal with the same time constant. The input signal is the voltage on capacitor  $C_1$  as it moves from initial voltage  $V_I$  to final voltage  $V_F$ .  $R_1$  and  $C_1$  set the time constant, as the following **equation** shows:

$$V_{IN} \! = \! V_F \! - \! (V_F \! - \! V_I) \! \times \! e^{-\frac{t}{R_1 C_1}} \! = \! V_A,$$

where e is an irrational constant approximately equal to 2.718281828. You then buffer this signal with an inverting gain of one-half to prevent clipping. Ignoring dc biasing for clarity, the ac output at Node  $V_B$  is a function of the RC time constant, as the following **equation** shows:

$$V_{B} = -0.5V_{F} + 0.5(V_{F} - V_{I}) \times e^{-\frac{t}{R_{I}C_{I}}}$$

You then differentiate the inverted signal with amplifier  $IC_1$ . You set the differentiator time constant with  $R_2$  and  $C_2$ . The gain of a differentiator circuit increases with frequency, making these circuits prone to instability. You use  $R_5$  and  $C_8$  to keep the circuit stable. At the low frequencies of interest,  $R_2$  and  $C_2$  dictate the function of the circuit, as the following **equation** shows:

#### **DIs Inside**

60 Schmitt trigger provides toggle function

60 Active multiplexing saves inputs

62 Transistor tester identifies terminals

64 Finely tune the hue of blue-light sources

What are your design problems and solutions? Publish them here and receive \$150! Send your Design Ideas to edndesignideas@ubm.com.

► To see all of *EDN*'s Design Ideas, visit www.edn.com/design ideas.

$$V_{\rm C} = -\tau \times \frac{dV_{\rm B}}{dt} =$$

$$-R_2C_2 \times 0.5(V_{\rm F} - V_{\rm I}) \times e^{-\frac{t}{R_1C_1}} \times \left(\frac{-1}{R_1C_1}\right).$$

$R_1$  and  $C_1$  set the time constant of the input, so you can match it by making the differentiator time constant,  $R_2 \times C_2$ , the same. This step cancels terms in the **equation** and simplifies the expression for output voltage, as the following **equation** shows:

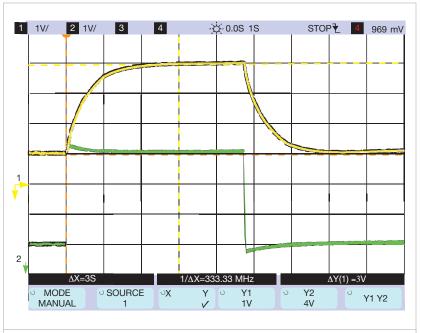

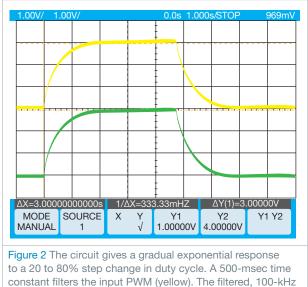

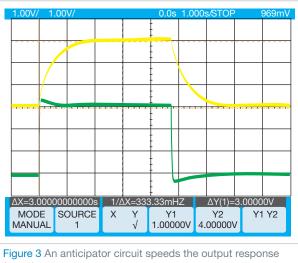

Figure 2 The anticipator circuit speeds the response of a slow exponential waveform (yellow) and results in nearly instant response to the final value, with only a small amount of overshoot (green).

$$V_{\rm C} = 0.5(V_{\rm F} - V_{\rm I}) \times e^{-\frac{t}{R_{\rm I}C_{\rm I}}}$$

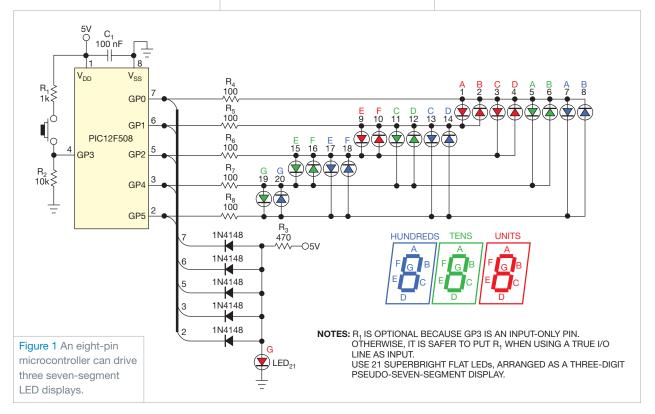

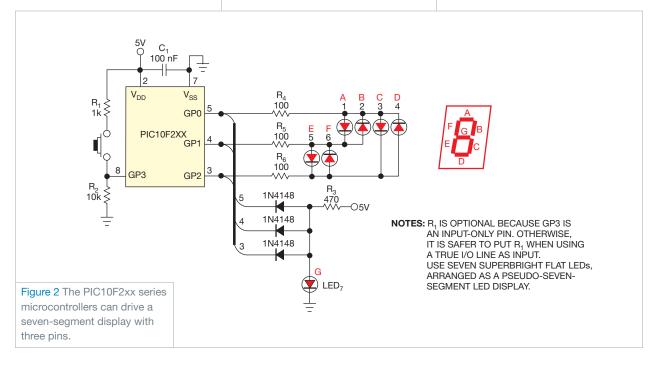

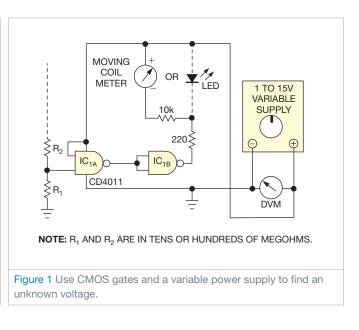

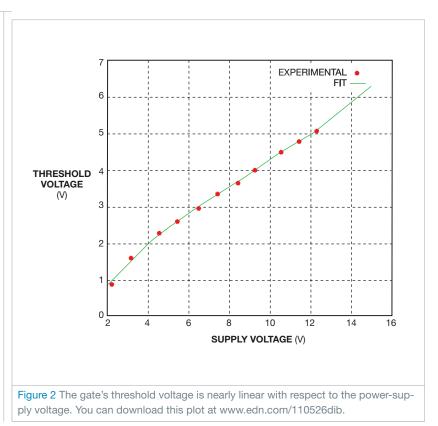

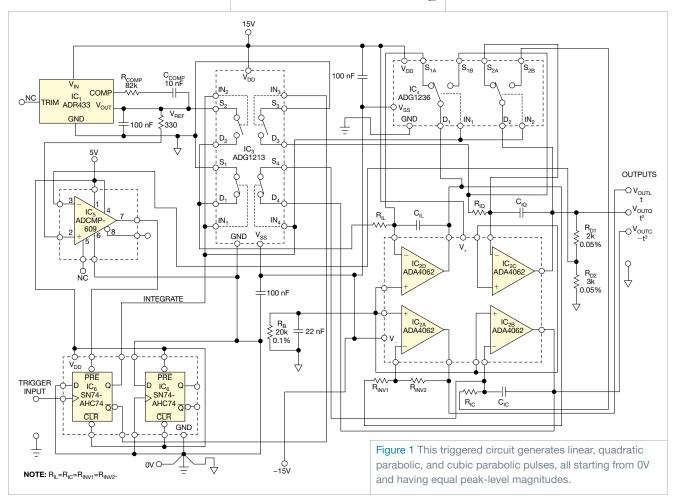

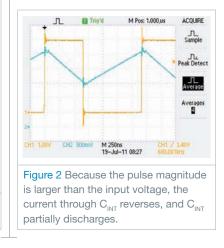

Due to scaling to prevent clipping, you sum this signal with the input signal in a weighted manner and present this voltage at the positive input of  $IC_4$ , as the following **equation** shows.