Design Ideas from EDN

January 1999 pag.6  $\mu$ C reprograms audio DAC via serial interface Calibrated trim tool tweaks multiturn pots Off-the-shelf watchdog serves in a pinch Novel circuit controls ac power Two AA cells power step-down regulator Temperature controller keeps IR detector at 8°K Flyback circuit provides isolated power conversion RISC  $\mu$ P implements fast FIR filter Simple algorithm transforms filter coefficients Door/window sensor resists tampering Use a trick to count scope events A primer on binary-arithmetic rounding Light powers isolation amplifier Low-cost feedback circuit boosts efficiency

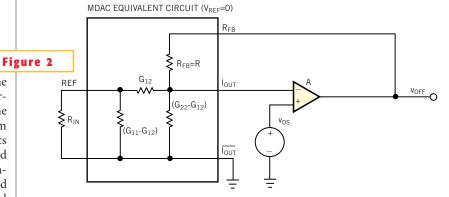

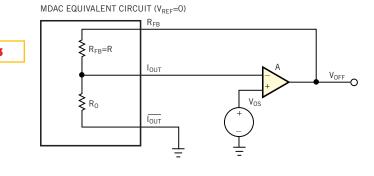

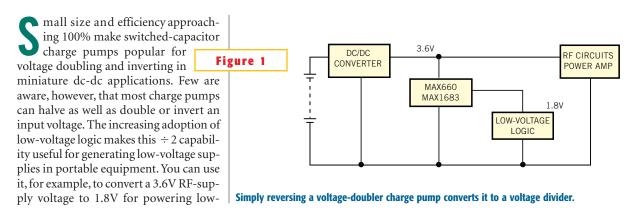

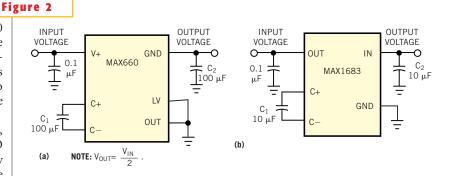

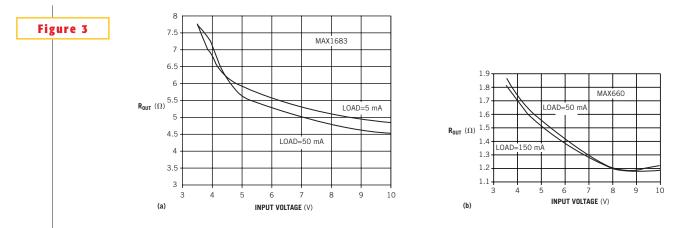

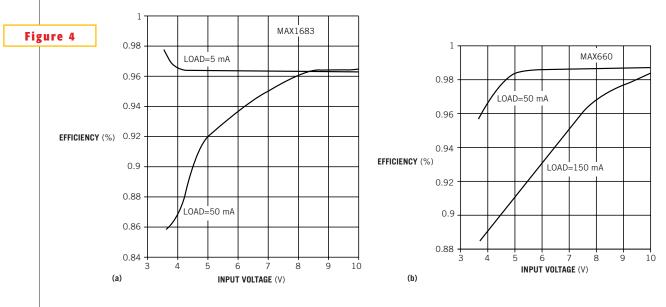

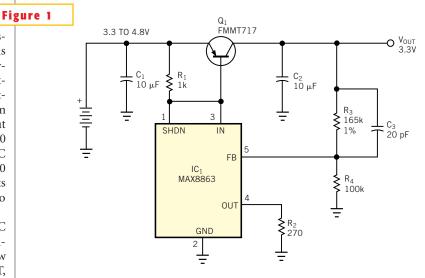

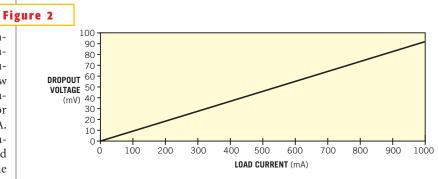

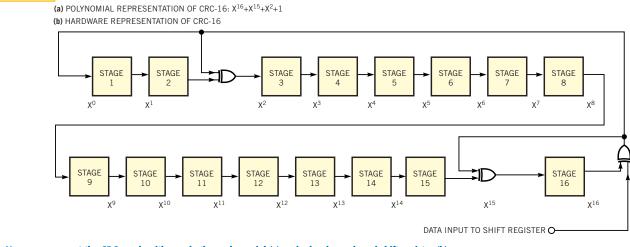

February 1999 ADC circuit optimizes key encoding RS-232C circuit has galvanic isolation Digital pot adjusts LCD's contrast Add speech encoding/decoding to your design Cheap PWM IC makes synchronous gate driver Circuit detects total on-time Simple circuit provides efficient PWM Visual Basic models MDAC offset Charge-pump circuit divides by two Pass transistor lowers dropout voltage PIC μC implements CRC-16 algorithm Monostable makes low-cost F/V converter

#### March 1999

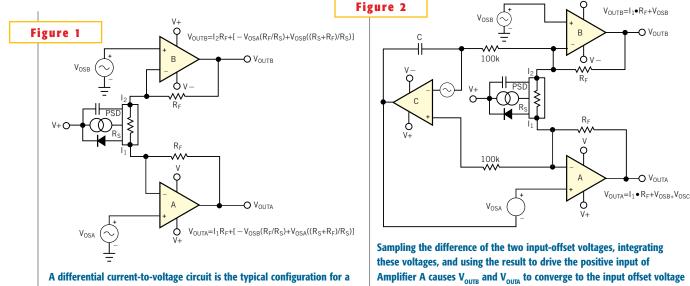

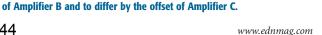

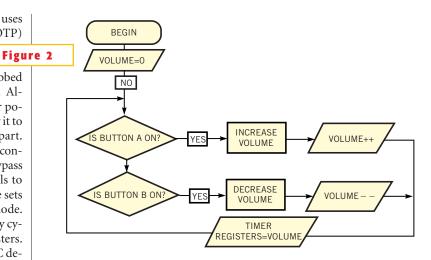

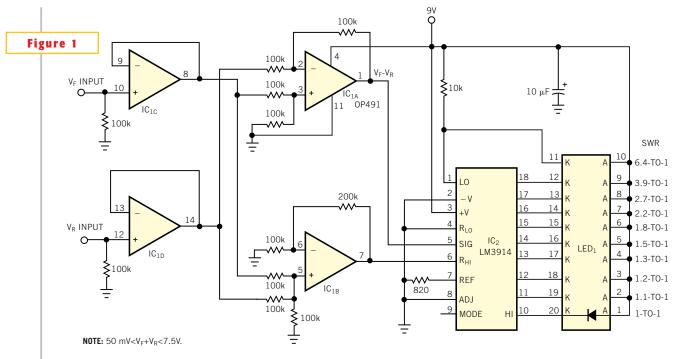

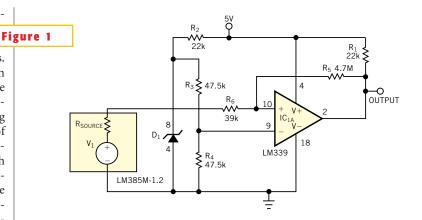

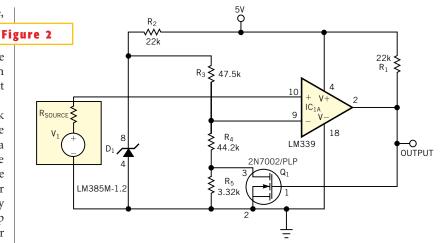

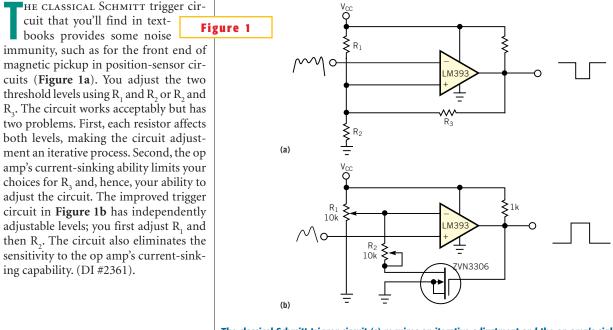

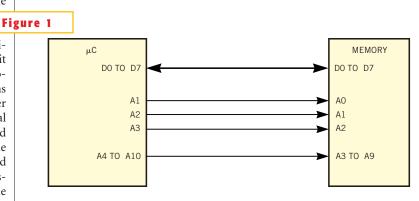

Simple circuit prevents processor latch-up Dual one-shot makes rising- and falling-edge detector Simple circuit measures diesel's rotations per minute Fast, compact routine interfaces EEPROM to  $\mu$ C Photodetector sorts objects Single-button lock provides high security Model fixed-point DSP arithmetic in C Two ADC channels double sensor precision Transistor pair lowers PWM IC's start-up current Autozero a position-sensing detector OTP  $\mu$ C controls Boomer amplifier LED driver displays standing-wave ratio Comparator provides stable hysteresis

#### April 1999

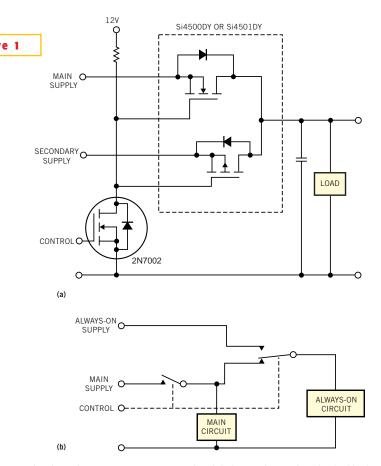

Shift register makes a fast counter RS-232C monitor operates without a power supply Simple circuits control RC servos One amplifier makes one-shot High-power latch provides 48V, 10A Tiny IC debounces pushbutton switch Back-to-back FETs thwart reverse current

#### May 1999

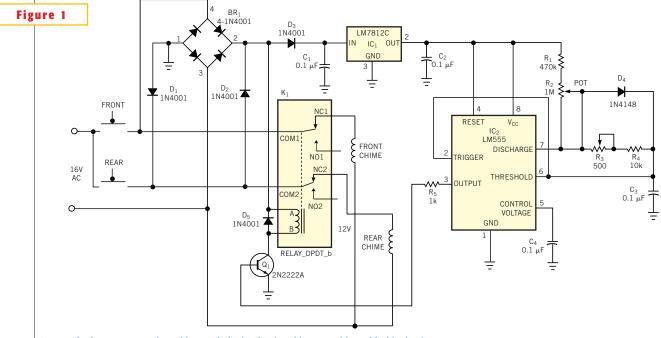

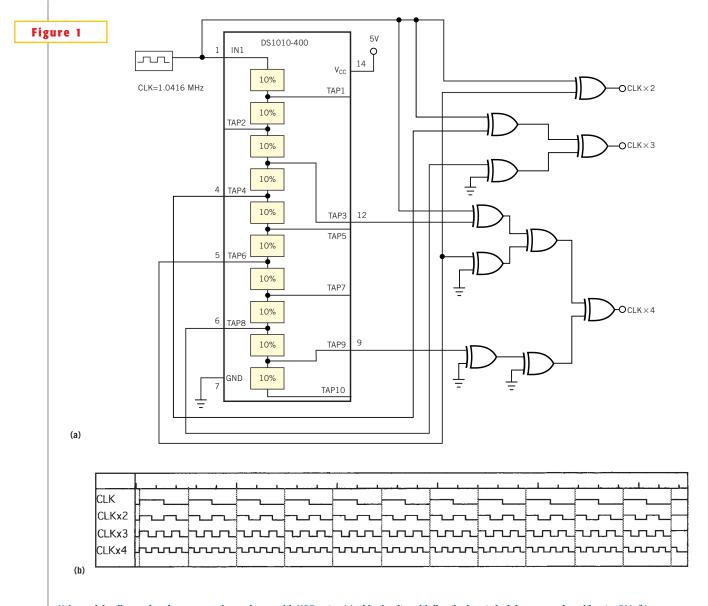

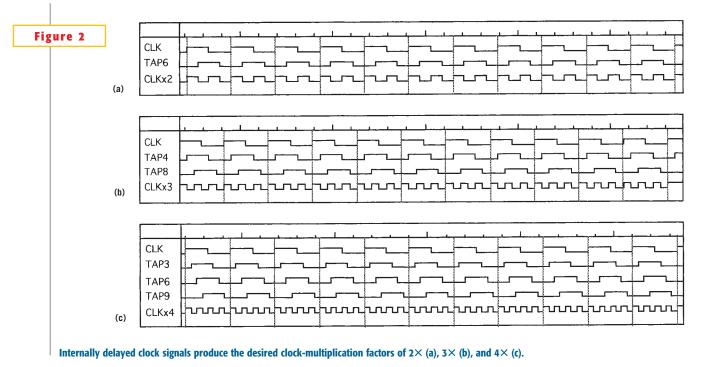

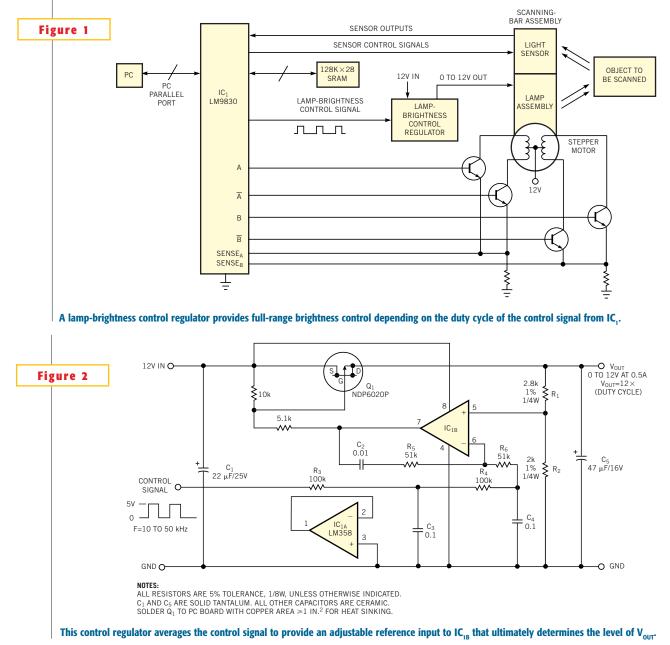

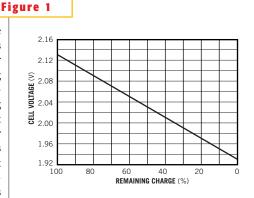

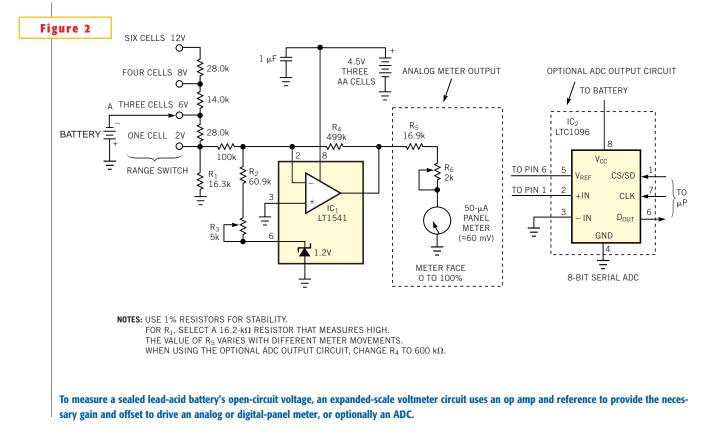

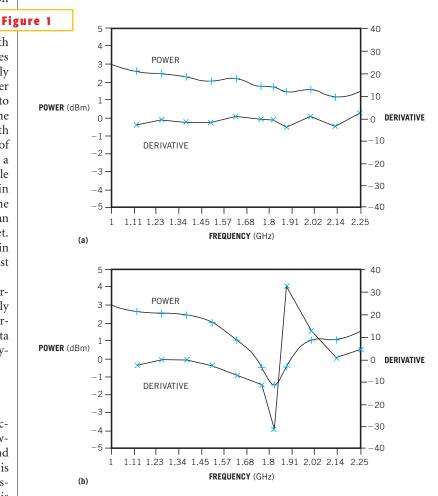

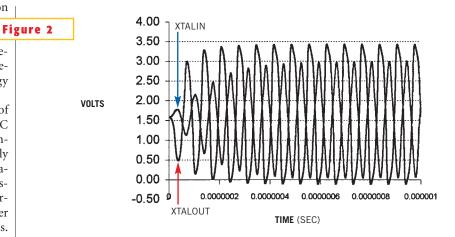

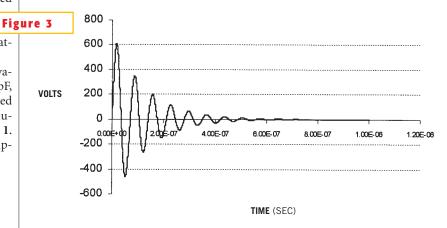

Switching regulator drives robot motor Simple fix adds door-chime repeater Clock multiplier circumvents PLL Synthesize optimal digital-frequency dividers Voltage regulator controls scanner-lamp brightness Simple changes improve Schmitt trigger Access odd memory locations without hardware Charge indicator gauges lead-acid batteries Use derivatives to catch RF calibration errors µC-based circuit performs frequency multiplication Kick start a crystal oscillator in Spice

#### June 1999

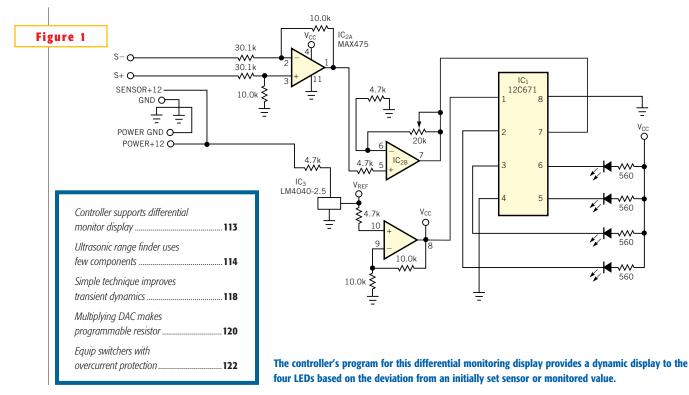

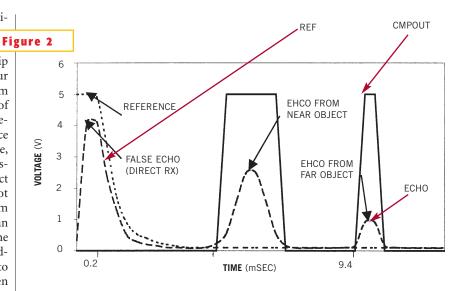

Missing-codes tester checks 16-bit ADC in 7 sec Switch-mode supply draws 43-mW standby power Circuit rejects ambient light V/I converter accommodates grounded load Digitally controlled potentiometer sets cutoff frequency Precision reference bans precision resistors Easy method calculates comparator trip points Controller supports differential monitor display Ultrasonic range finder uses few components Simple technique improves transient dynamics Multiplying DAC makes programmable resistor Equip switchers with overcurrent protection

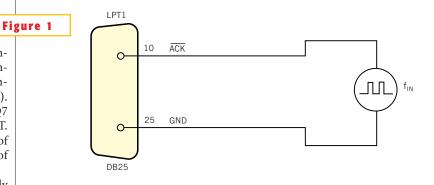

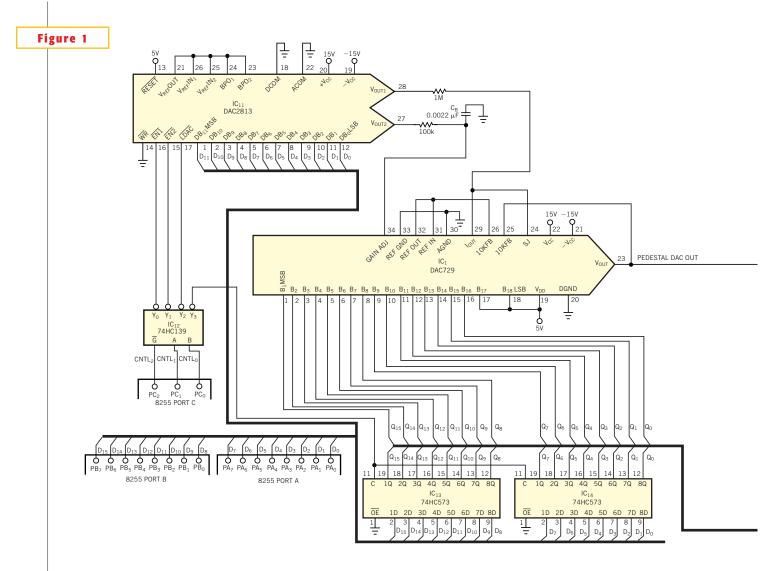

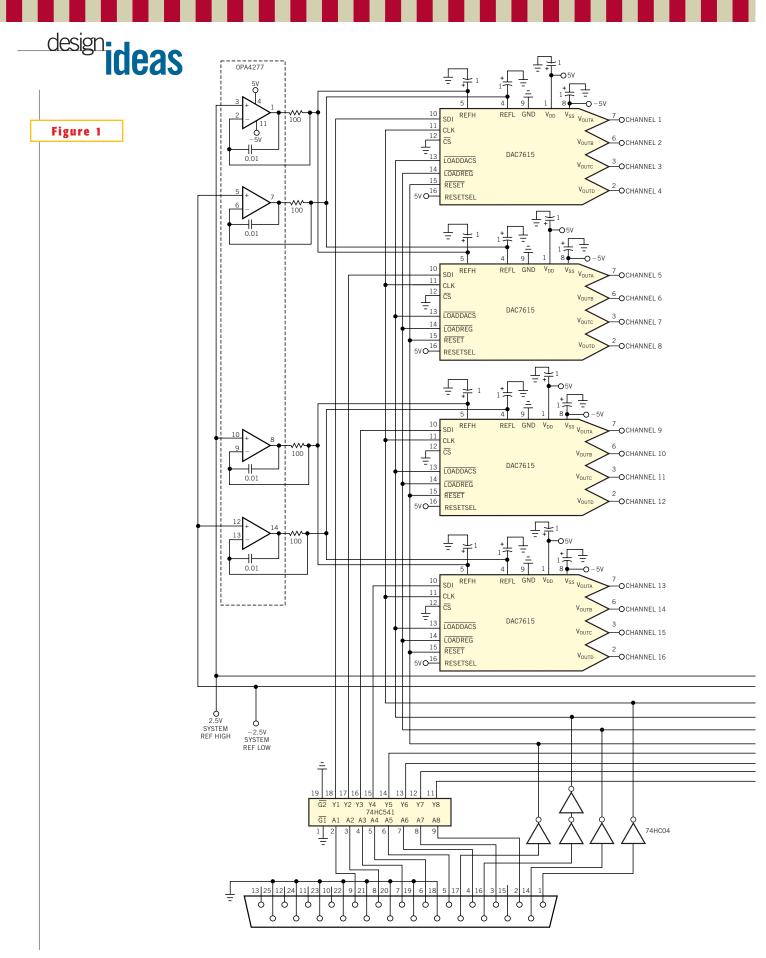

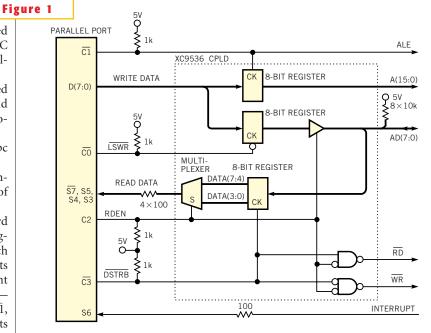

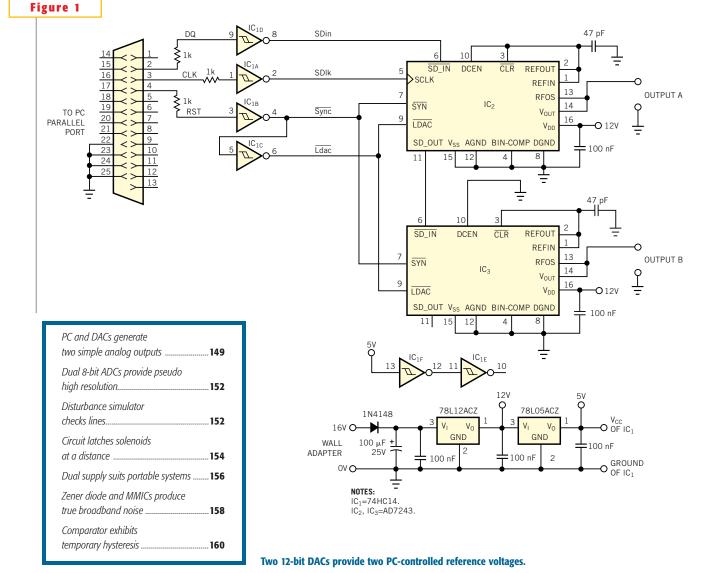

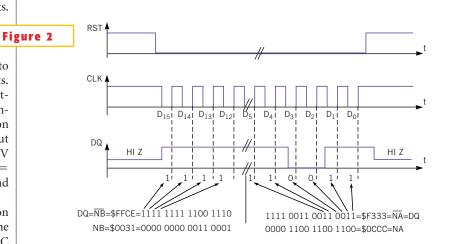

#### July 1999 Control 32 DAC channels via a parallel port

Comparator has programmable limits DAA circuit emulates central-office operation Speedy logic translator uses little power Parallel port replaces embedded  $\mu$ C Transimpedance amp covers dc to gigahertz range Simple scheme detects shorts High-isolation converters use off-the-shelf magnetics Autoranging circuit simplifies hardware and software Simple technique speeds Microstrip breadboarding Comparator has independent trip voltages Modem-access adapter reduces interference Synchronous oscillator converts audio, video to FM

#### August 1999

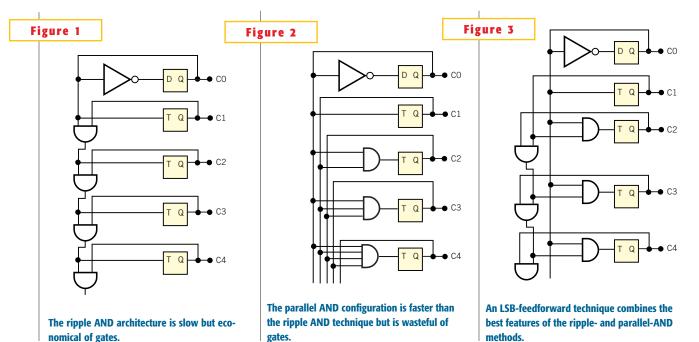

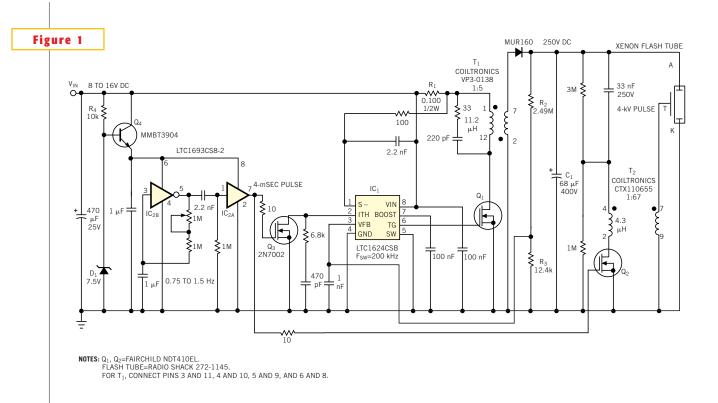

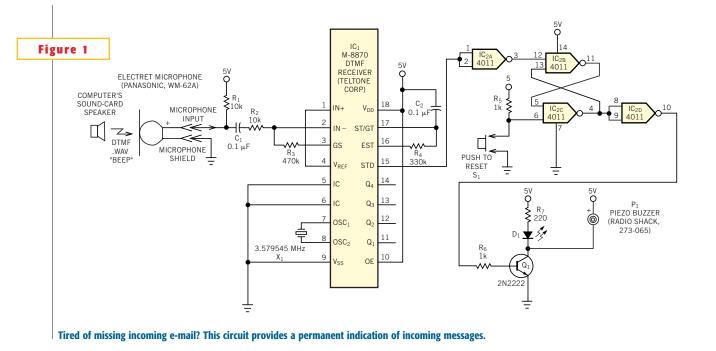

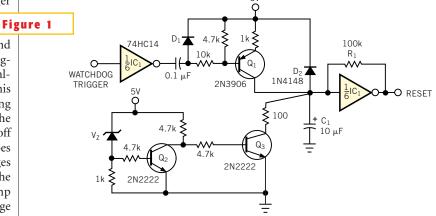

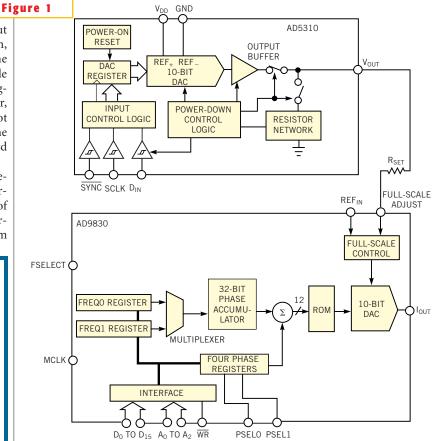

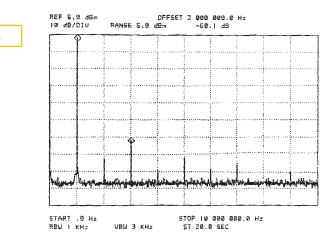

Scheme extends DDS phase-shift resolution Single  $\mu$ C pin makes half-duplex RS-232C Binary counter uses LSB feedforward Simple logic reduces EMI Emergency strobe flasher generates 250V 3.3V lithium-cell supply requires one inductor Circuit monitors quad supply for PCI systems Circuit controls multiple thermoelectric coolers Current-input ADC measures voltages You've got mail Circuit provides brownout control of 80C31 Circuit emulates mechanical metronome PC controls light dimmer

#### September 1999

DDS device provides amplitude modulation Charge pump converts V IN to $\pm$ V OUT Electronic SPDT controls two PCs GMR sensors manage batteries Driver thermally compensates LED Program turns PC sound card into a function generator Li-ion battery charger adapts to different chemistries Current-sense amplifier precisely measures low side Connect a modem to a Basic Stamp Bias supply provides short-circuit protection Analog multiplier works over large frequency range 5V logic pulser is battery-powered Square-root function improves thermostat  $\mu$ C detects transmission rate of RS-232 interface Current sensor measures 0 to 500A Safely swap SCSI disk drives SSB modulator covers HF band Switched-capacitor IC forms notch filter

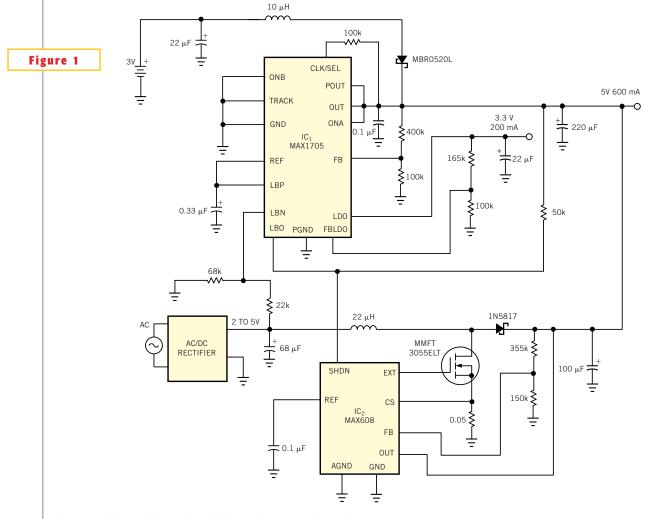

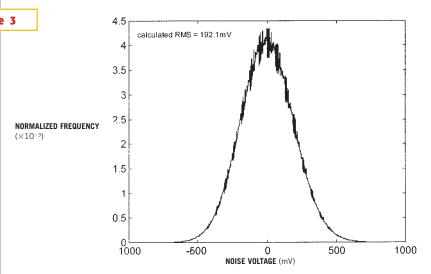

October 1999 PC and DACs generate two simple analog outputs Dual 8-bit ADCs provide pseudo high resolution Disturbance simulator checks lines Circuit latches solenoids at a distance Dual supply suits portable systems Zener diode and MMICs produce true broadband noise Comparator exhibits temporary hysteresis Fast algorithm computes histograms Loop powers current transmitter Spice creates time-variant resistor VCO supply touts low noise  $\mu$ C forms FM oscillator Circuit converts pulse width to voltage Restore dc to NRZ sigmals

November 1999 Controller IC halves switcher's standby power Load detector controls power sources Two-wire interface has galvanic isolation Measure power-on current transients on ac line Generator has independent pulse width, frequency Customized potentiometers aid amplifier design Ring your bell; light your light Voltage regulator goes digital Supply converts 5V to-48V C routine speeds decimal-to-binary conversion Resistor implements half-duplex RS-232 with echo Circuit monitors ac-power loss RF transmitter uses AMI encoding High-voltage regulator is 100%-surface-mountable

December 1999 Scheme cancels amplifier error Serial port provides interrupts for 8031µC ADC-to-PC interface transfers data in nibbles Matched offsets put signals into ADC's range Amplifier compensates piezoelectric-rate gyros Digital camera subs as a scope camera MOSFET pair makes simple SPDT switch Motor controller operates without tachometer feedback Cascade ABCD two-port networks Simple tester checks Christmas-tree lights Power meter uses low-cost multiplier Add music to your next project PWM circuit uses fuse to sense current Bias supply accepts high inputs Method provides simple error-rate generator Edited by Bill Travis and Anne Watson Swager

## $\mu\text{C}$ reprograms audio DAC via serial interface

<sup>3n</sup>ideas

Lukasz Sliwczynski, University of Mining and Metallurgy, Institute of Electronics, Cracow, Poland

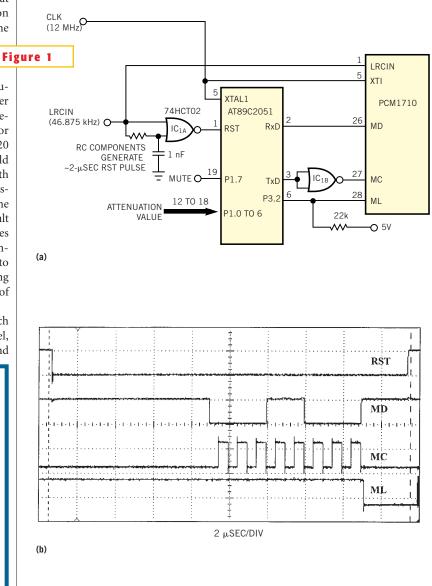

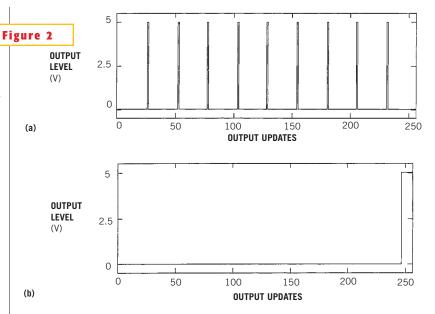

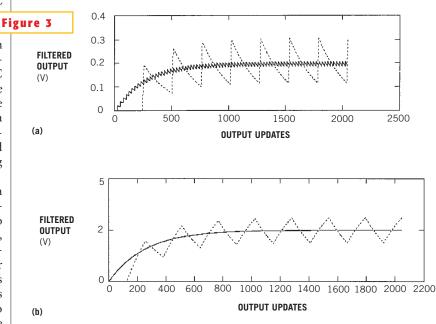

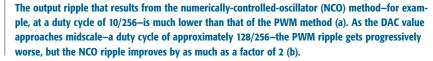

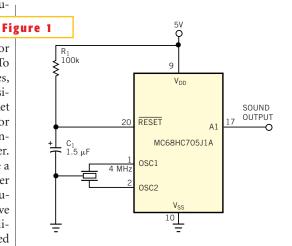

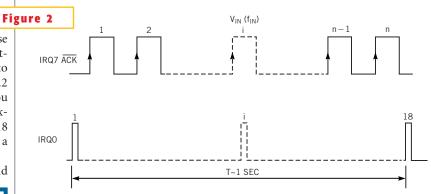

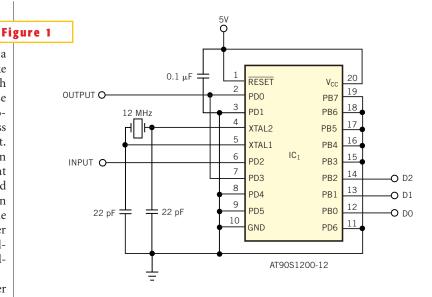

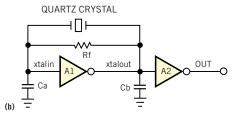

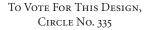

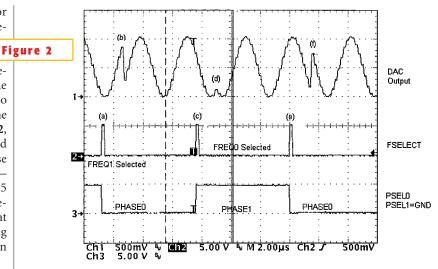

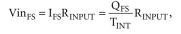

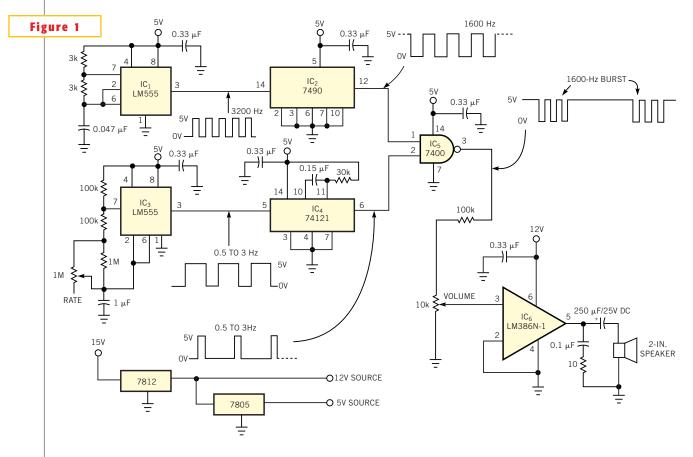

OU CAN USE A SIMPLE  $\mu$ C to continuously program an audio DAC so that it operates in a 20-bit resolution mode (**Figure 1**). After power-on, the

PCM1710  $\Delta\Sigma$  DAC (Burr-Brown Corp, www.burr-brown.com) operates in its default 16-bit resolution mode. Switching to its 20-bit resolution mode requires supplying the converter with a control word using its three-wire serial digital interface (SDI). A risk exists for using this converter at a resolution of 20 bits in a transmission system that should work 24 hours a day, seven days a week with no, or only occasional, supervision. A disturbance can cause reprogramming of the converter and cause it to revert to its default settings. The circuit in Figure 1 eliminates this possibility by repeatedly reprogramming the DAC. The circuit uses the SDI to continuously supply three programming words, which define the converter's state of operation, to the DAC.

The reprogramming circuitry, which uses a popular AT89C2051 µC (Atmel, www.atmel.com), has few components and

| $\mu$ C reprograms audio DAC via serial interface  | 107 |

|----------------------------------------------------|-----|

| Calibrated trim tool tweaks multiturn pots         | 108 |

| Off-the-shelf watchdog serves<br>in a pinch        | 110 |

| Novel circuit controls ac power                    | 112 |

| Two AA cells power<br>step-down regulator          | 114 |

| Temperature controller keeps<br>IR detector at 8°K | 114 |

| Flyback circuit provides isolated power conversion | 118 |

A simple  $\mu$ C-based circuit (a) continuously reprograms the PCM1710 audio DAC for a resolution of 20 bits. The  $\mu$ C sends 1 byte of code after each RST pulse (b).

www.ednmag.com

is power-efficient (**Figure 1a**). Because any  $\mu$ C system is also vulnerable to external disturbances, it's best to reset the  $\mu$ C repetitively. The circuit uses the LRCIN signal to reset the  $\mu$ C and invoke the programming procedure. The LRCIN signal also switches digital-audio words between the left and right channels of the converter. Thus, the  $\mu$ C takes less time to execute the program than the period of the LRCIN signal. The sampling rate is 46.875 kHz, so the period of the LRCIN signal is approximately 21  $\mu$ sec. The circuit must devote some of this time to properly resetting the  $\mu$ C.

The SDI of the PCM1710 comprises data (MD), clock (MC), and latch (ML) lines. To drive this SDI, the serial port of the  $\mu$ C operates in the default mode, Mode 0. Although this mode of operation is rare in many applications, it is convenient in this case because, apart from sending serial data via its RxD pin (P3.0), the serial clock is available on the TxD pin (P3.1). Thus, the RxD line directly serves as the MD signal, and the inverted TxD line serves as the MC signal. The program generates the third SDI line (ML). Sending 3 bytes of data to the DAC requires at least 36 µsec, assuming a 12-MHz clock from the DAC clock and omitting the time that the internal reset procedure of the  $\mu$ C consumes. Thus, you can transmit 1 byte for one program execution, which occupies about 17 µsec. Assuming that 2 µsec is enough time for the  $\mu$ C to properly reset, the entire program should easily fit into the allowable 21µsec frame. The low time of RST is approximately 19 µsec (Figure 1b).

This interface circuit relies on the fact that after you apply the RST signal to the  $\mu$ C, some internal registers do not change their values, and others reset to 00H. Listing 1 is the corresponding assembler code. (You can download this listing from *EDN*'s

#### LISTING 1–PCM1710 DAC ASSEMBLER CODE ; ATTENUATION SET ON PORT P1.0 (MSB) - P1.6 (LSB) .EQU PCON, 087H .EQU FLAG.7, 07H .EOU FLAG.6, 06H .EQU FLAG.5, 05H .ORG 00H JBC FLAG.7.B 03 JBC FLAG.6, B\_02 ;2 -> TOTAL MACHINE CYCLES: 4 B\_01: MOV SBUF, RO ;2 SEND ATTENUATION BYTE MOV R0,#25H ;1 SAVE MODE 2 BYTE BEFORE RESET SETB FLAG.6 MOV A,#02H :1 SET UP FOR THE NEXT RESET ;1 NOP NOP NOP NOP NOP CLR P3.2 ;1 GENERATE ML SIGNAL ORL PCON, A ;1 GO TO POWER DOWN -> TOTAL MACHINE CYCLES: 12 B 02: MOV SBUF, R0 SEND BYTE MODE 2 MOV A, P1 ANL A, #080H ;1 READ MUTE SIGNAL FROM P1.7 ORL A.#060H ;1 ;2 CALCULATE ADDRESS OF MODE 1 BYTE ;1 SAVE MODE 1 BYTE BEFORE RESET MOVC A, @A+DPTR MOV RO,A SETB FLAG.7 MOV A,#02H ;1 SET UP FOR THE NEXT RESET ;1 CLP P3 2 -1 GENERATE MJ. SIGNAL ORL PCON, A ;1 GO TO POWER DOWN B 03: MOV SBUF, RO ;2 SEND BYTE MODE 1 :1 READ ATTENUATION FROM PORT P1.0 - P1.6 MOV A, Pl RL A ANL A,#0FEH MOV R0,A SETB FLAG.5 1 SAVE ATTENUATION VALUE BEFORE RESET 1 SET UP FOR THE NEXT RESET MOV A,#02H NOP - 1 CLR P3.2 ;1 GENERATE ML SIGNAL ORL PCON, A ;1 GO TO POWER DOWN ;MODE 1 BYTE FOR MUTE-OFF -> P1.7 = L ORG 060H .DB 001H ;MODE 1 BYTE FOR MUTE-OFF -> P1.7 = H .ORG 0E0H .DB 041H

web site, www.ednmag.com. At the registered-user area, go into the Software Center to download the file from DI-SIG, #2312.) After each RST pulse, the  $\mu$ C sends 1 byte of code; the  $\mu$ C sends the same byte every third RST pulse. The circuit uses register R<sub>o</sub> to temporarily save the value of the next word to send because the  $\mu$ C reset does not affect this register. The circuit also uses one bit-addressable memory location, designated FLAG (20H), to switch between bytes to send. Port P1 supplies the program with the attenuation value on pins P1.0 to P1.6 (from MSB to LSB) and supplies the MUTE signal on pin P1.7. The circuit stores the proper value of the Mode 1 control word in the program-memory area of the  $\mu$ C at locations 60H (MUTE deasserted) and E0H (MUTE asserted). (DI #2312)

To Vote For This Design, Circle No. 427

### Calibrated trim tool tweaks multiturn pots

Sanjay Chendvankar, Tata Institute, Mumbai, India

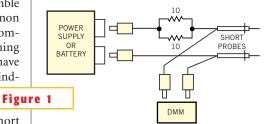

ANY ANALOG CIRCUITS contain multiturn trimming potentiometers whose settings you may need to change during maintenance or calibration. Also, some instruments have panelmounted potentiometers that may need periodic adjustments. After disturbing a setting by more than one or two turns, it becomes difficult or impossible to restore the original setting. The usual method is to measure the resistance between the wiper and one of the ends of the potentiometer before disturbing the setting and then to readjust to the same setting if and when necessary. However, this method is incon-

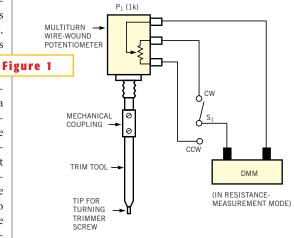

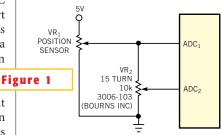

venient and sometimes impossible, such as when the trimmer is mounted on a panel, for example. The simple tool in **Figure 1** comes in handy in such situations.

You construct the tool by mechanically coupling the trimming tool's shaft to the shaft of a high-quality, multiturn, wirewound potentiometer ( $P_1$ ). The wiper and one of the end terminals of this potentiometer connect to a DMM operating in resistancemeasurement mode. The toggle switch,  $S_1$ , selects one of the two available end terminals. Before disturbing the setting of a multiturn potentiometer in a circuit, you rotate the trim tool to the endpoint of  $P_1$ 's rotation span in

the opposite direction to that in which you intend to adjust the trimming potentiometer. Set the selector switch such that the DMM reads zero (or near-zero) resistance. Then, you rotate the trim tool by

#### This "tool with a memory" allows you to accurately restore the original setting of a multiturn potentiometer.

firmly holding  $P_1$  with one hand and turn the trimming potentiometer to the desired setting. The corresponding  $P_1$  resistance value on the DMM, along with  $S_1$ 's position, tells you whether the tool rotates clockwise or counterclockwise. You record these data for future reference.

If you wish to restore the potentiometer's original position, you adjust P, to the recorded value with the same position of S<sub>1</sub> by turning the trim tool in the opposite direction until the DMM reads zero resistance. This position is the original setting of the potentiometer. The resistance value of P, is not critical. However, it's better to select low values to obtain higher resolution on the DMM. Also, a single range of the DMM should cover the value. This prototype uses 1 k $\Omega$ . You can improve the tool by replacing P<sub>1</sub> with a miniature bidirectional optical shaft en-

coder and connecting its output to an up/down counter. (DI #2308)

To Vote For This Design, Circle No. 428

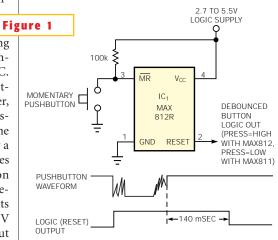

#### Off-the-shelf watchdog serves in a pinch

Giovanni Romeo, Istituto Nazionale di Geofisica, Roma, Italy

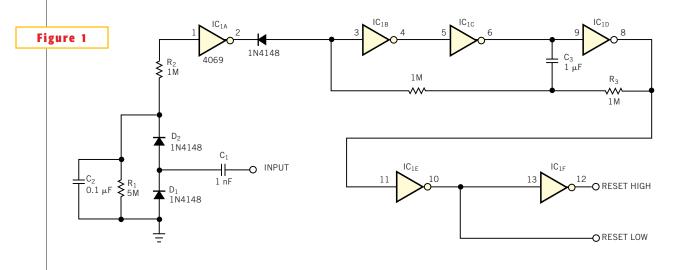

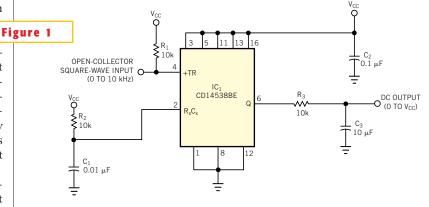

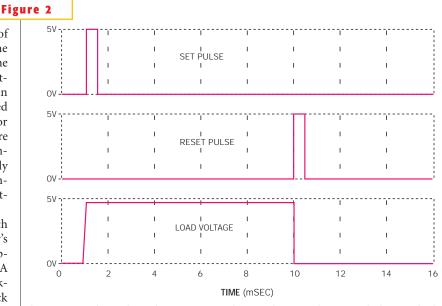

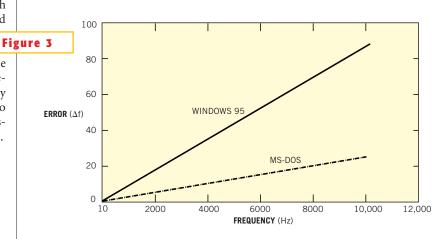

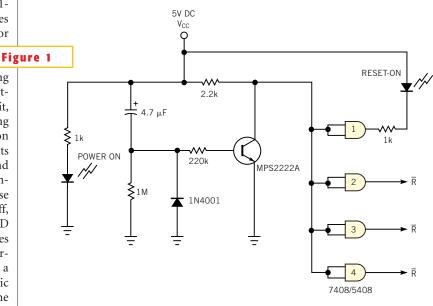

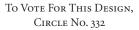

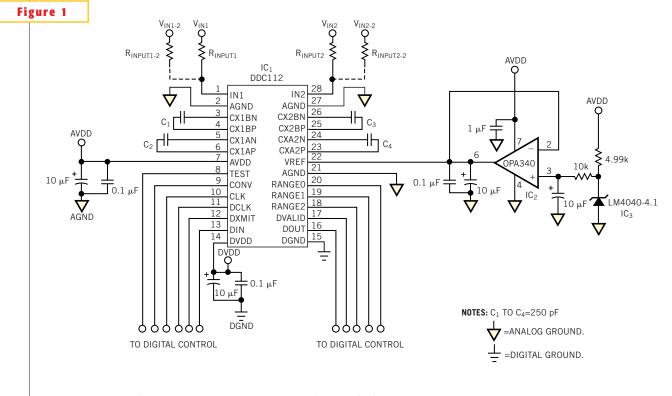

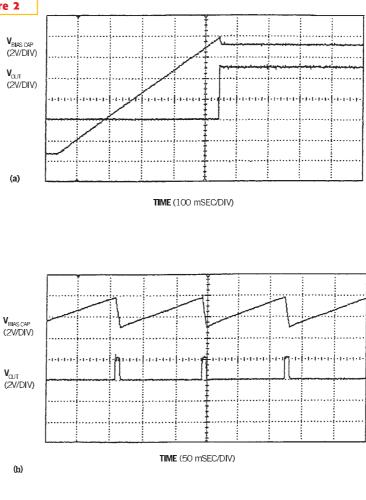

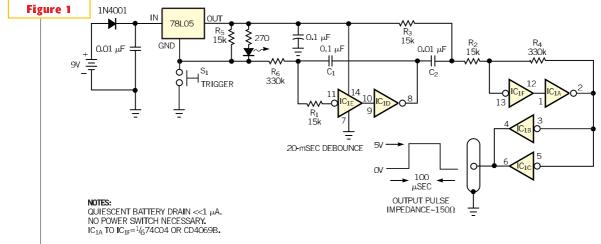

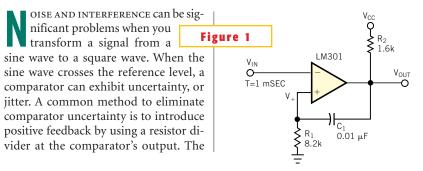

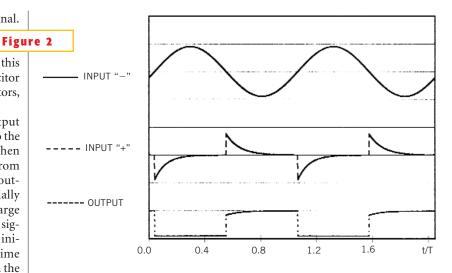

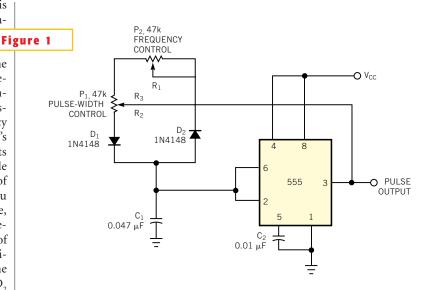

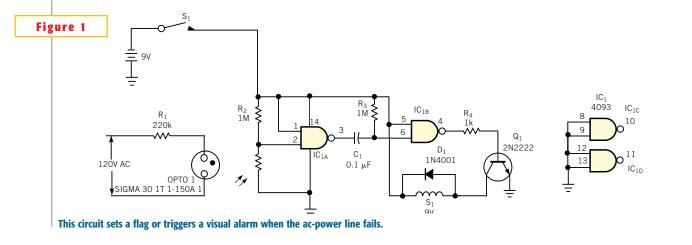

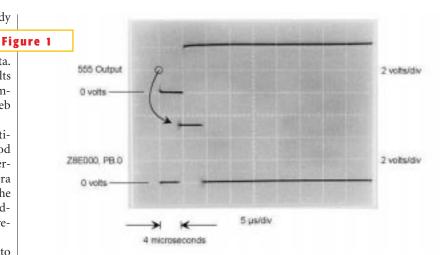

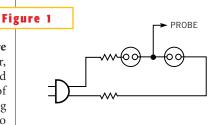

HE PERFORMANCE OF THE WATCHDOG CIRCUIT in **Figure 1** may not match that of a dedicated watchdog circuit, but this circuit is helpful when the only watchdog in the lab doesn't meet your design's temperature requirement and when you are in a hurry to finish a prototype.

The circuit operates on a simple principle. When digital activity occurs on the in-

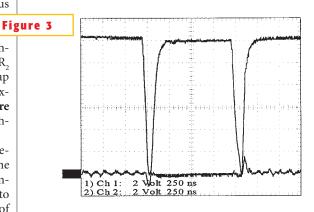

A charge pump comprising  $D_{1}$ ,  $D_{2}$ ,  $C_{1}$ , and  $C_{2}$  inhibits a three-gate oscillator when input activity exists. After 40 msec without input activity, the oscillator starts running and produces a reset signal.

**110** EDN | JANUARY 7, 1999

put, a charge pump comprising  $C_1$ ,  $D_1$ ,  $D_2$ , and  $C_2$  keeps  $C_2$  charged.  $R_1$  is the discharge resistor for  $C_2$ .  $IC_{1A}$  detects the charge level through  $R_2$ . A charged condition inhibits the three-gate oscillator comprising  $IC_{1B}$ ,  $IC_{1C}$ , and  $IC_{1D}$ , and the active-high resethigh output stays low.

When the voltage at the input of  $IC_{1A}$  drops below the CMOS threshold, the oscillator starts working and produces a

square wave. The high time of the resethigh output resets the  $\mu$ P under control, which must start the activity (and activate the watchdog input) before the end of the low time. R<sub>3</sub> and C<sub>3</sub> essentially control the high and low times, which have almost the same value.

Although this design monitors an RS-232C line, you can use the circuit to monitor a digital level. When monitoring an RS- 232C line with the values in **Figure 1**, the watchdog starts resetting 40 msec after detecting no activity and requires less than 20 msec to inhibit the oscillator after input activity resumes. (DI #2311)

To Vote For This Design, Circle No. 429

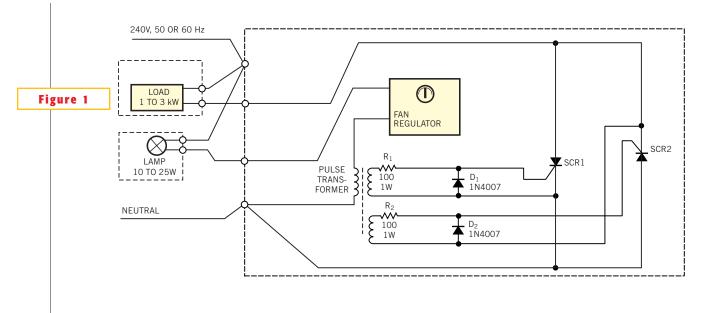

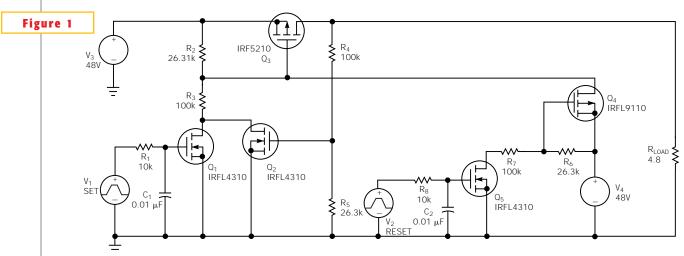

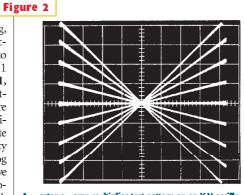

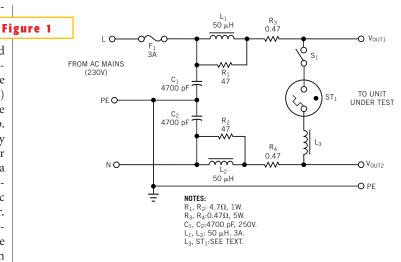

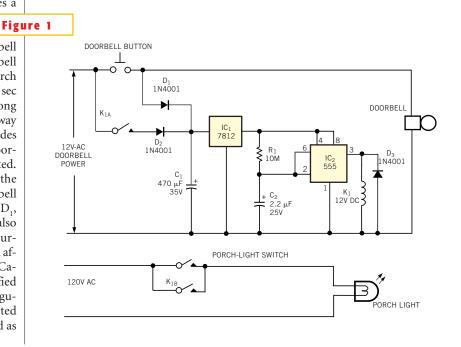

#### Novel circuit controls ac power

Narendra Paranjape, Tata Chemicals Ltd, Mithapur, India

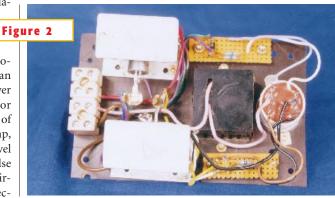

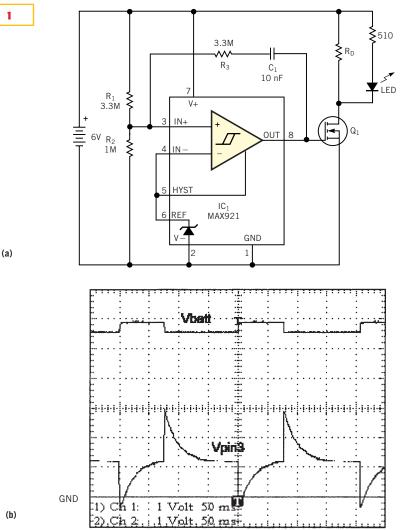

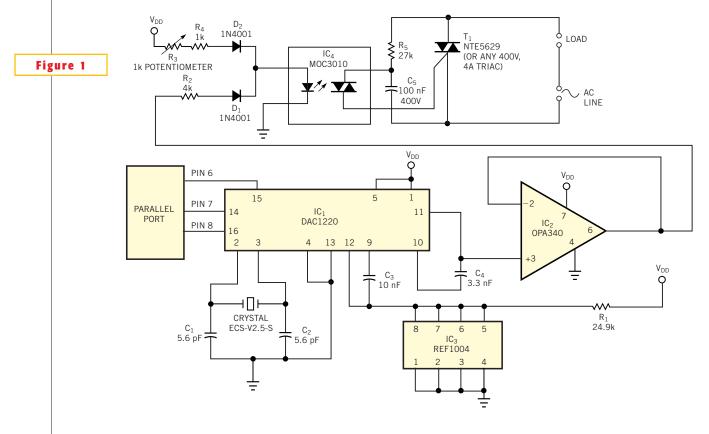

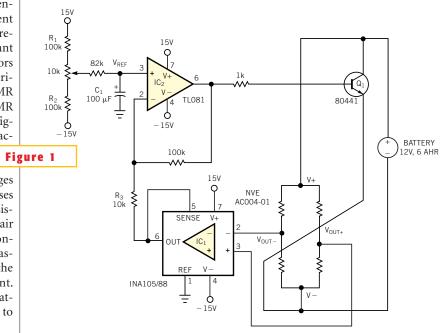

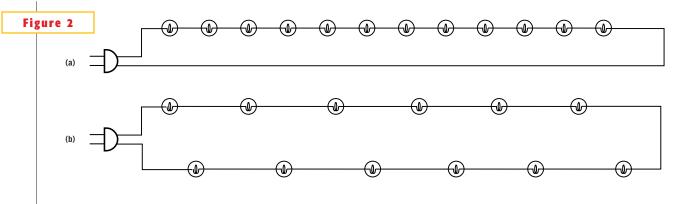

The SIMPLE AND INEXPENSIVE powercontrol circuit in **Figure 1** uses a readily available fan regulator with built-in phase control. Such fan regula-

tors are limited to approximately 100W. The circuit in **Figure 1** adds two SCRs and a few components to turn the humble fan regulator into a mighty power controller. The fan regulator operates with a nominal load of 10 to 25W through a lamp, which also gives a power-level indication. The 1:1:1 pulse transformer completes the circuit. The transformer's secondary windings fire the back-to-back SCRs, which then control a load of 1000 to 3000W. You can house the circuit in any in-

sulated box. You should mount the SCRs on heat sinks.  $R_1$ ,  $D_1$  and  $R_2$ ,  $D_2$  limit the gate current and prevent the application of

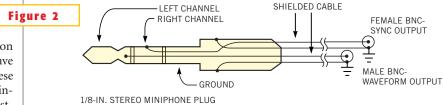

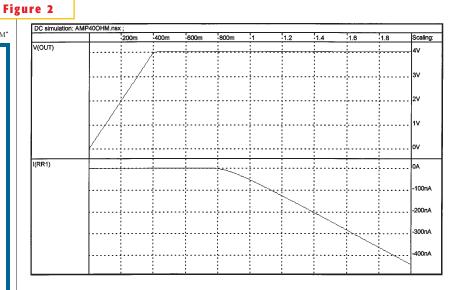

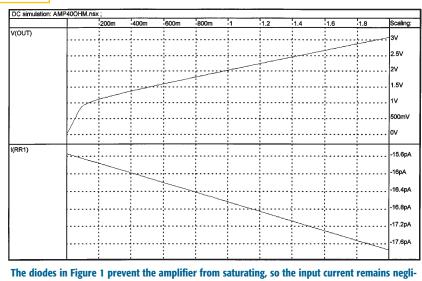

reverse voltage between gate and cathode. **Figure 2** shows construction details of the prototype. (DI #2310)

To Vote For This Design, Circle No. 430

An easy-to-build power controller works with an inexpensive fan regulator to control 1000 to 3000W.

A couple of thyristors, a pulse transformer, and two diodes transform a humble 100W fan regulator into a high-power ac controller.

**112** EDN | JANUARY 7, 1999

## design**ideas**

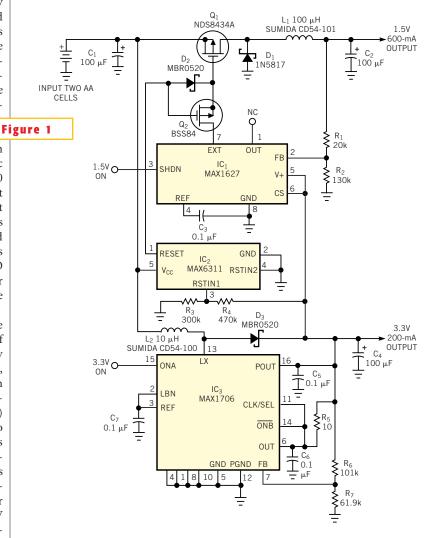

## Two AA cells power step-down regulator

Len Sherman, Maxim Integrated Products, Sunnyvale, CA

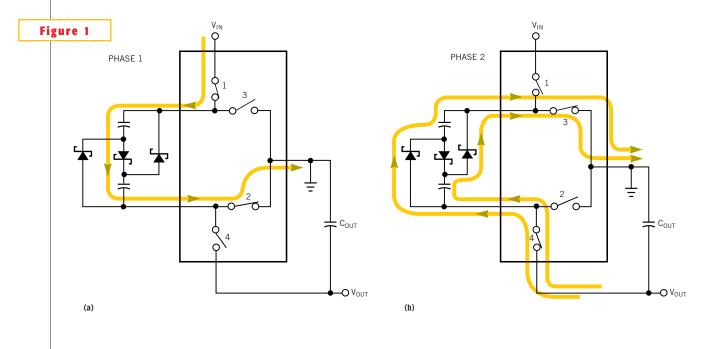

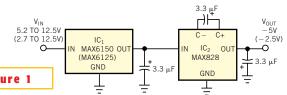

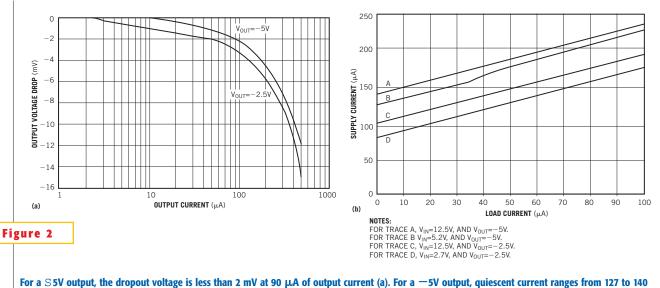

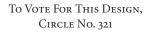

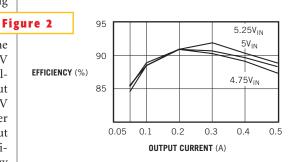

**D** C/DC CONVERSION IS particularly challenging when both the input and output voltages are low. Step-up ICs that operate with inputs lower than 1V are available, but step-down ICs that accept input voltages near 2V are not. Thus, providing efficient power for the low-voltage CPU in a handheld product can be a prob-

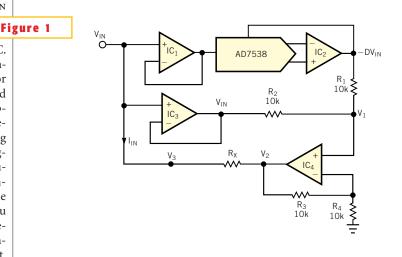

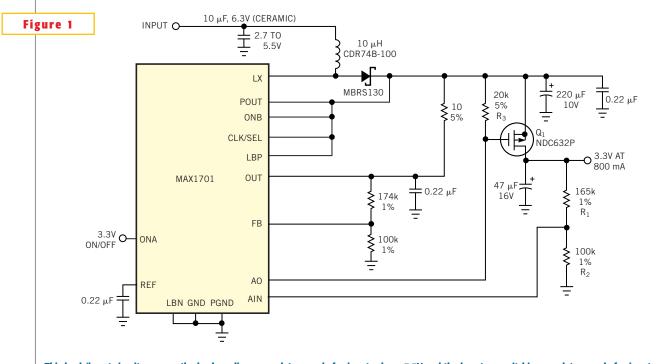

lem if the power source is a two-cell AA battery. The battery's output can drop to 1.8V as the battery discharges. In **Figure 1**, the upper switch-mode dc/dc converter ( $IC_1$ ) generates more than 600 mA at 1.5V, from a two-AA-cell input that varies from 3.4 to 1.8V. The 3.3V rail that powers this step-down controller comes from a high-current, synchronous-rectified boost controller ( $IC_3$ ), which also provides power for external logic and the CPU's I/O blocks.  $IC_1$  receives 3.3V bias, but power for the 1.5V output comes directly from the battery.

$Q_2, D_2$ , and a SOT-23 reset IC (IC<sub>2</sub>) force the switching power MOSFET (Q<sub>1</sub>) off when the 3.3V rail is too low to properly operate IC<sub>1</sub>. Without those components, the conditions at power-up (during which battery voltage is present but 3.3V are momentarily absent, pulling Q<sub>1</sub>'s gate low) may cause the 1.5V output to overshoot to the battery voltage. The 1.5V output's buck-conversion efficiency (approximately 85%) is reasonably good for the circuit's extra-small components: a three-pin SOT-23 power MOSFET and 5-mm-diameter surface-mount inductors. For the 3.3V output, IC,'s on-chip synchronous rectification yields a boost efficiency higher than 90%. (DI #2302)

To Vote For This Design, Circle No. 431

Powered by the 3.3V boost controller  $IC_3$ , this step-down controller  $(IC_1)$  generates 1.5V from inputs as low as 1.8V.

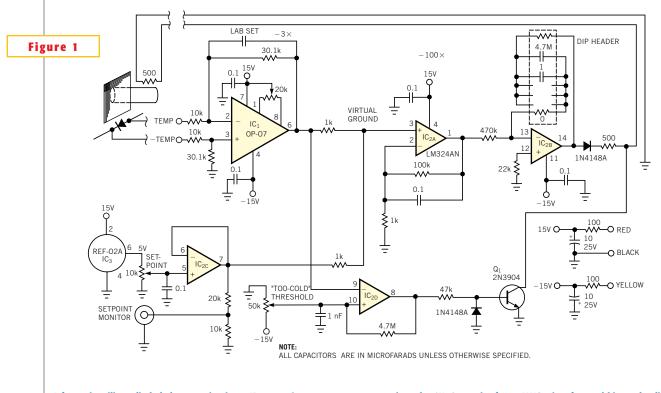

### Temperature controller keeps IR detector at 8°K

Jerry Penegor, Space Sciences Laboratory, University of California—Berkeley

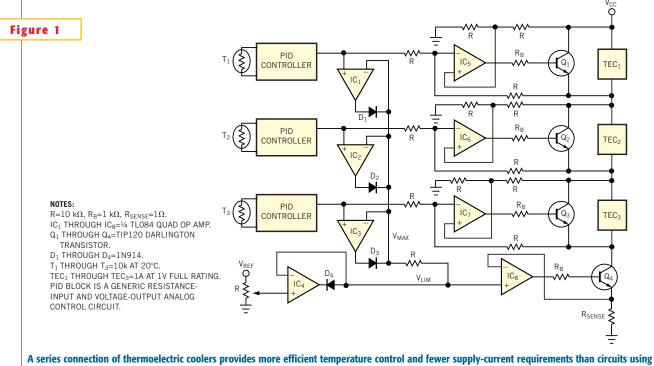

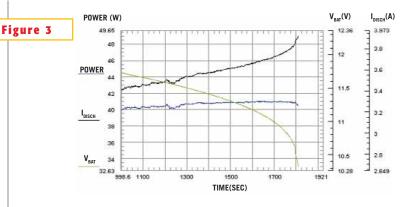

S ENSITIVE INFRARED array detectors must operate at a low temperature to avoid thermally generated dark current throughout the photoconductive elements. This requirement is

particularly true for SiAs array detectors, which need cooling to near liquid-helium temperatures. Furthermore, the sensitivity of these detectors can be temperature-dependent. The optimal operating temperature for a long-wavelength IR camera is about 8°K. This temperature must remain constant despite changes in the radiation level falling on the array, in the liquid helium level as it boils away, and

in the orientation of the Dewar flask.

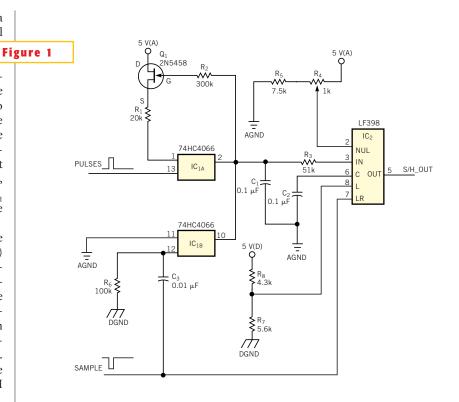

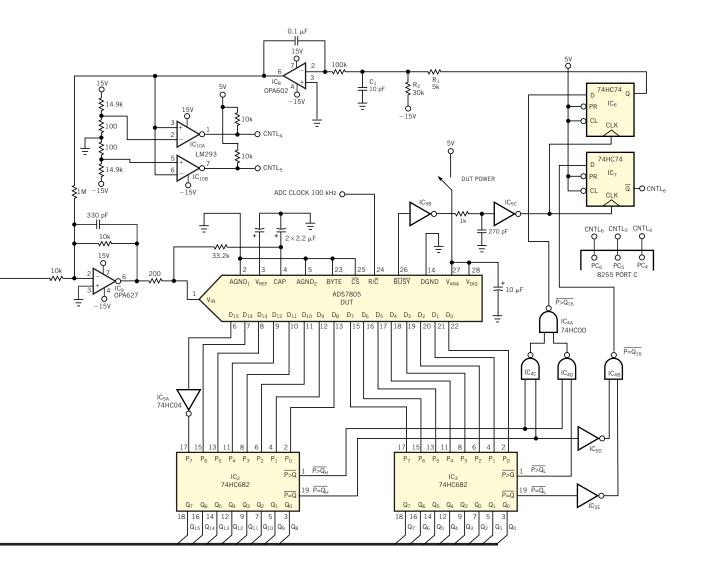

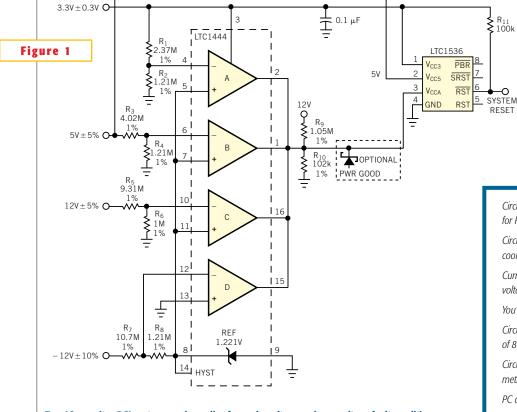

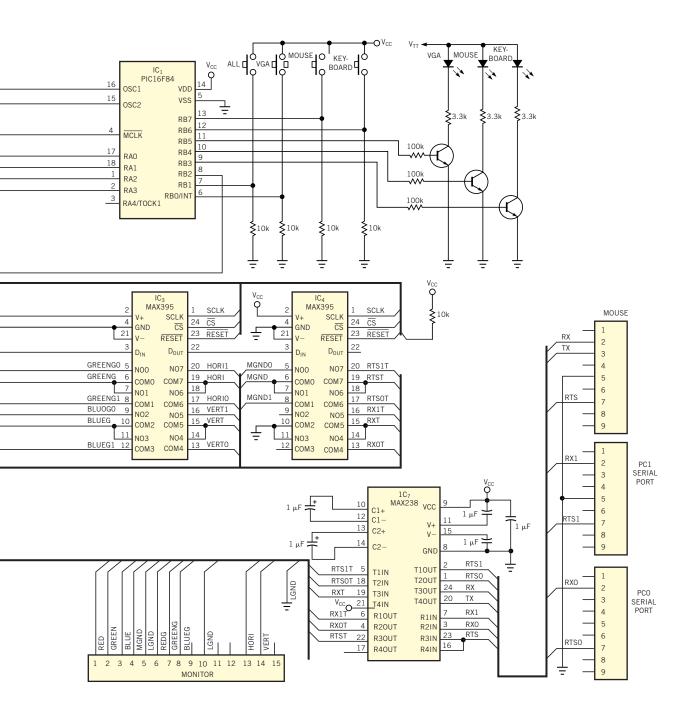

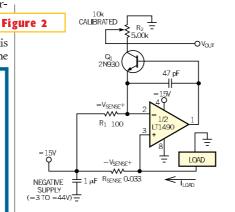

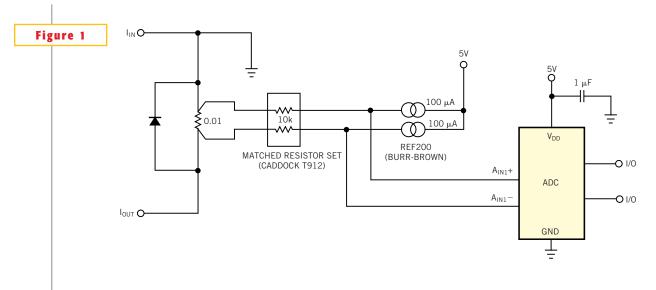

To measure and control these low temperatures, the circuit in **Figure 1** uses a four-wire silicon diode. One pair of #38 AWG wire forward-biases the diode with a fixed 10  $\mu$ A of drive current. The second pair of wires provides for Kelvin-connection measurement of the forward-voltage drop, V<sub>P</sub>, which is a very nonlinear function of temperature. Around 8°K, the V<sub>P</sub> is 1.5V and changes about -35 mV/°K. To accurately measure the array temperature requires mounting the diode as close as possible to the SiAs array in its ceramic chip carrier.

The back of this carrier is spring-loaded against an oxygen-free, high-conductivity copper plug onto which a 500 $\Omega$  wirewound resistor attaches. A heavy copper braid also connects the plug to the liquidhelium reservoir. Good thermal contact between the power resistor and the chip carrier ensures that a simple circuit can control the temperature. The simple proportional-integral servo circuit in **Figure** 1 can control array temperature to  $\pm 5 \text{ m}^\circ\text{K}$ over an 8 to 12°K range. Slewing the array to a new setpoint temperature takes approximately 30 sec.

Special low-thermal-conductivity steel coax cable goes through hermetic connectors in the vacuum Dewar flask wall. This cable makes all electrical connections to the cooled camera. The schematic shows no low-leakage unity-gain buffers that isolate the voltages at the sensor diode's anode and cathode (+ and -T) from all the meters and circuitry that operate at room temperature.

Op amp IC<sub>1</sub> is a differential receiver for the + and -T voltages and has a gain of -3. Because -3 times the coldest expected V<sub>F</sub> is about -4.8V, a stable 5V reference, IC<sub>3</sub>, supplies the voltage at the potentiometer for the temperature setpoint over the necessary range. The setpoint-monitor output has an attenuation of 3, so you can see the setpoint voltage directly on any meter.

When the sensor and setpoint voltages are in balance, the noninverting input to  $IC_{2A}$  is 0V.  $IC_{2A}$  amplifies any imbalance.  $IC_{2B}$  sets the frequency response of the servo with a zero at a corresponding time constant of 10 sec. That is,  $IC_{2B}$ 's gain term of 10 is constant for any ac disturbances but is high for dc error. Mounting the resistors and capacitors that set the servo time constant on a seven-position header allows you to easily add component values when the controller is mounted on the Dewar flask. The output diode ensures that positiveonly current goes to the power resistor on the heat sink; power off is 0V, and no negative currents can flow. (Negative current does not cool the power resistor.) The optional 500 $\Omega$  series resistor in series with the output diode provides additional current limiting for IC<sub>28</sub>.

One condition to guard against is a broken or disconnected sense diode that sends the temperature controller into full-power application.  $IC_{2D}$  senses temperatures that are too cold—excessive negative voltage from IC—to be valid. The 50-k $\Omega$  potentiometer sets the "too-cold" threshold at approximately –5V. If the circuit detects a too-cold condition,  $IC_{2D}$  turns on  $Q_1$ , which shorts the output and sinks the output current within  $Q_1$ . (DI #2296)

> To Vote For This Design, Circle No. 432

A four-wire silicon diode helps to maintain an IR camera's temperature at approximately 8°K. One pair of #38 AWG wires forward-biases the diode with a fixed 10 mA of drive current. A second pair of wires provides for a Kelvin-connection measurement of the diode's forward voltage drop, which is a nonlinear function of temperature.

**116** EDN | JANUARY 7, 1999

## design**ideas**

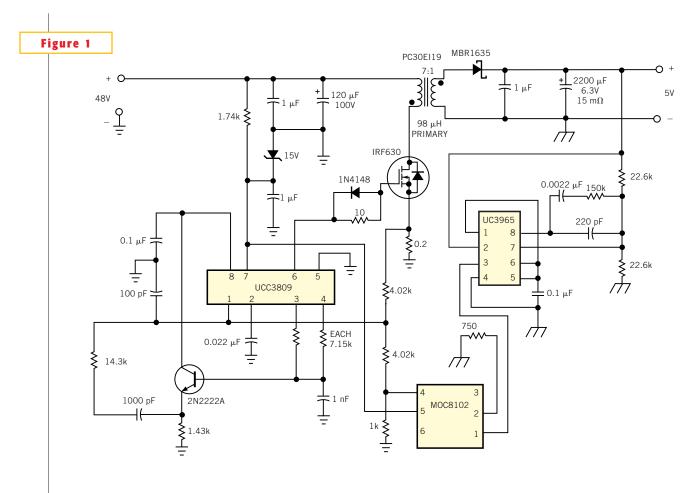

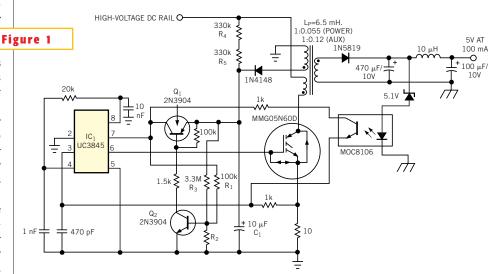

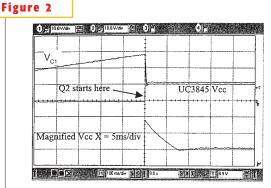

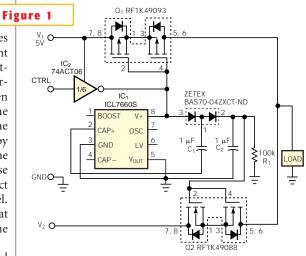

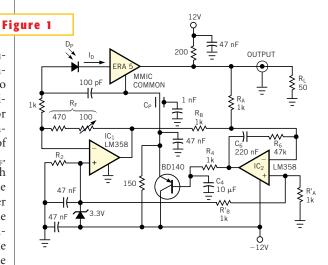

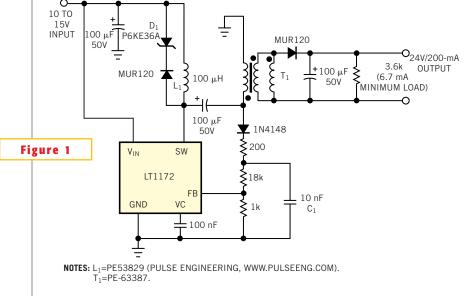

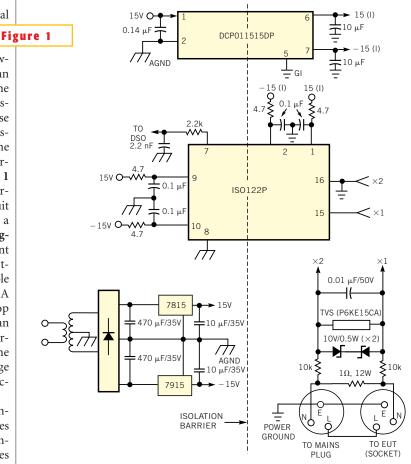

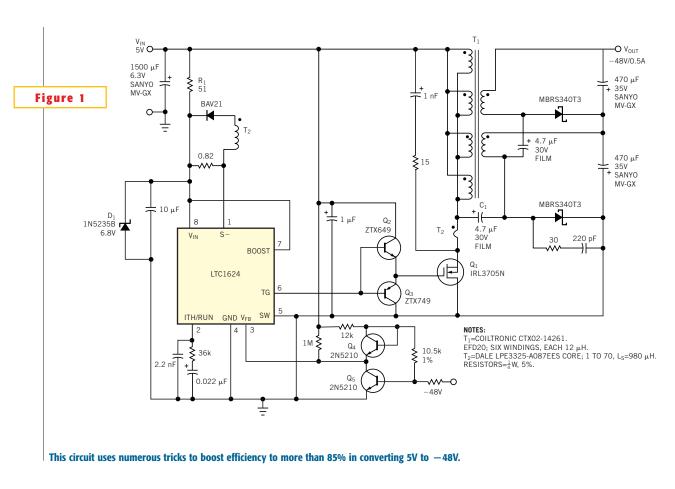

## Flyback circuit provides isolated power conversion

Philip Cooke, Unitrode Corp, Merrimack, NH

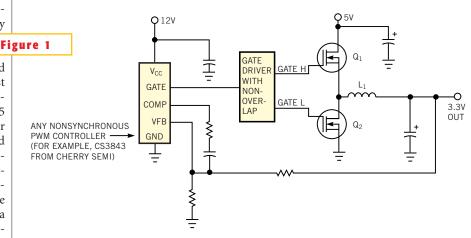

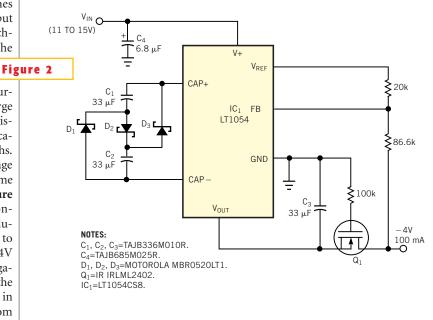

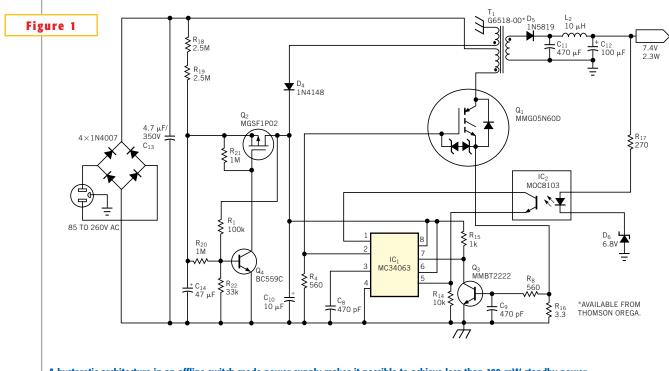

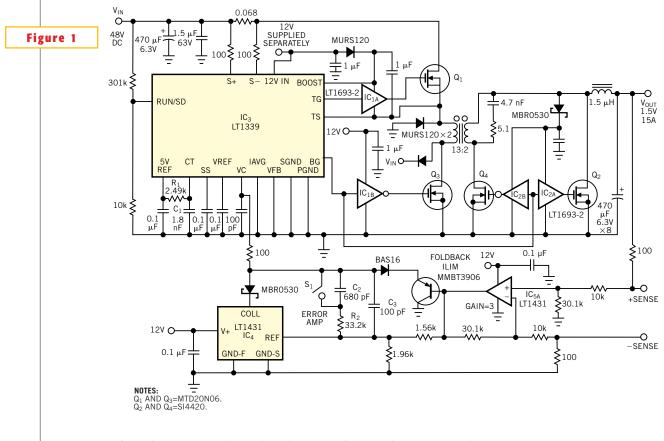

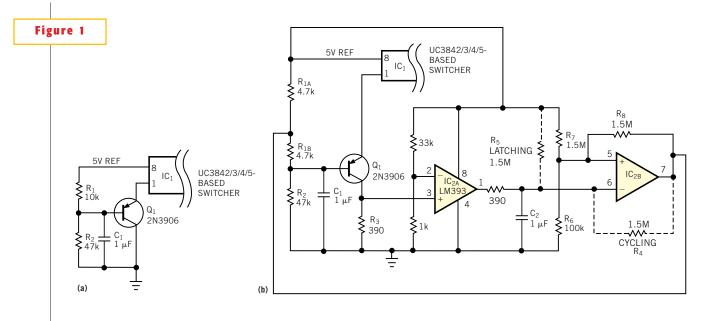

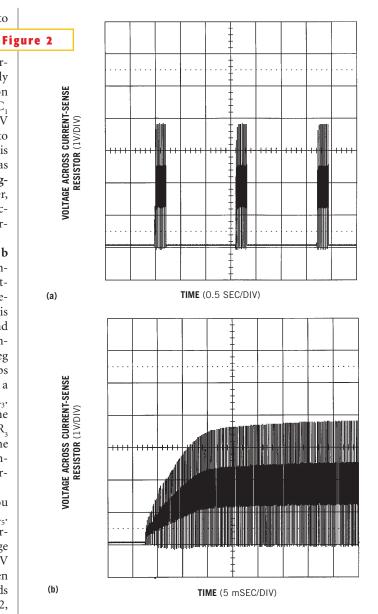

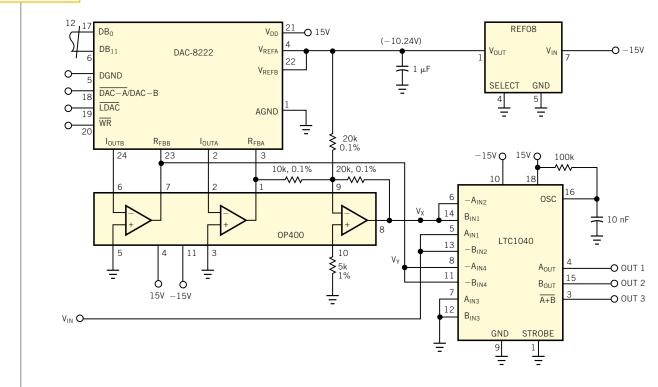

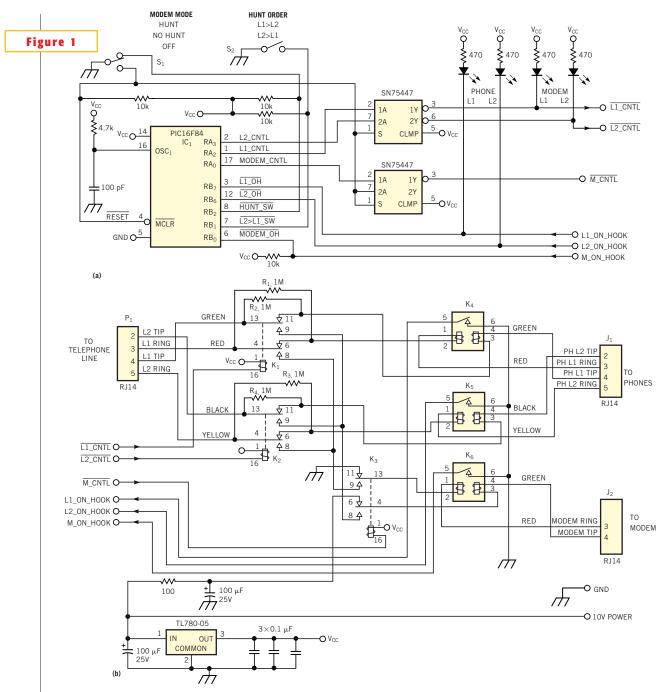

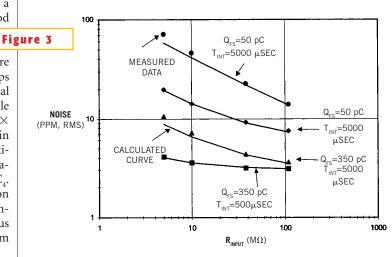

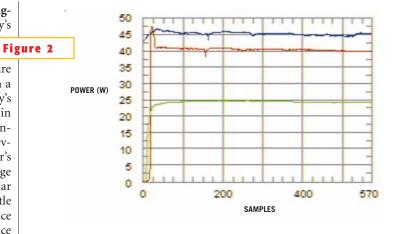

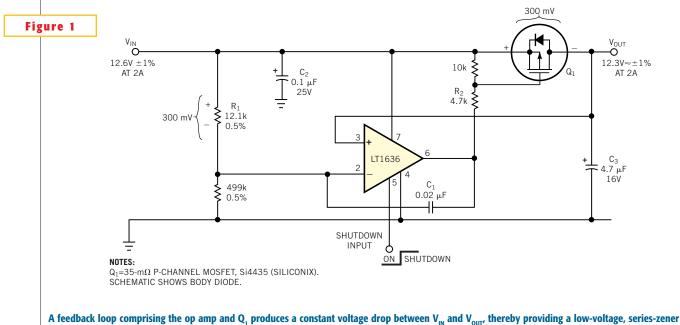

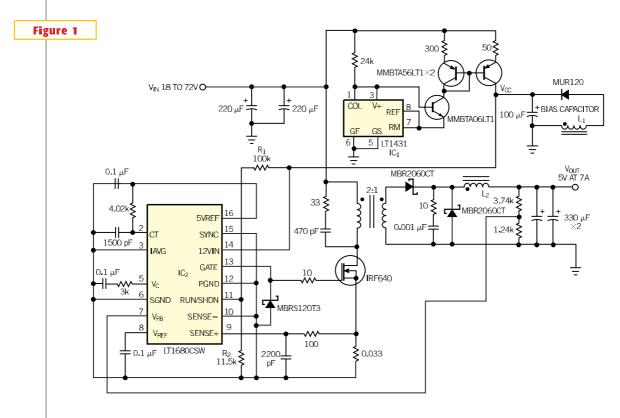

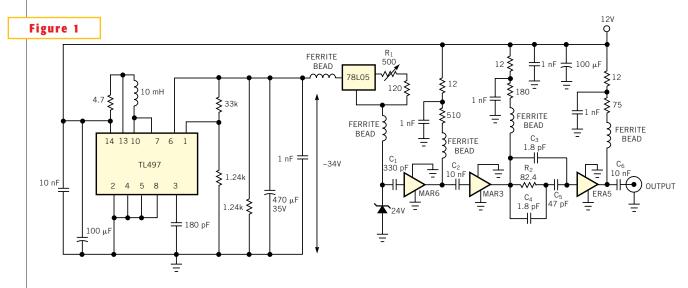

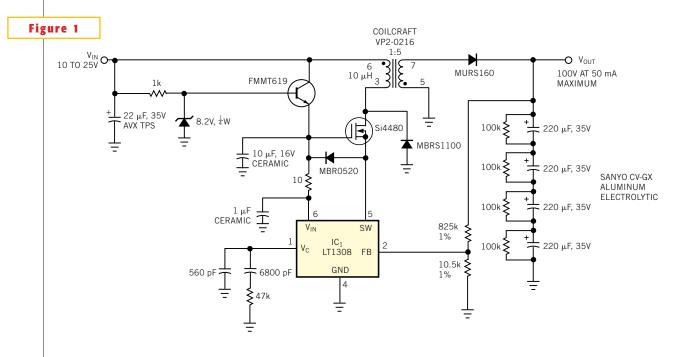

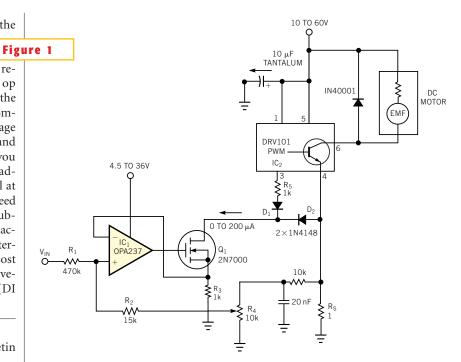

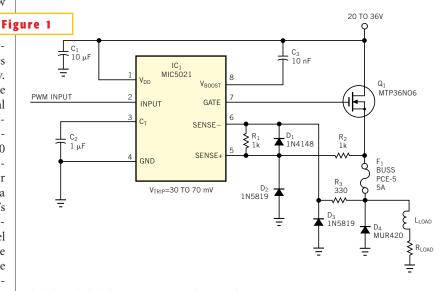

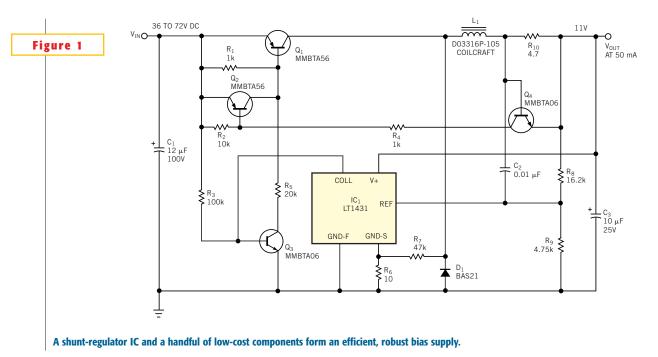

COMMON REQUIREMENT in telecommunications systems is to convert an unregulated 48V line to an isolated, accurate dc supply voltage. The circuit in Figure 1 provides a 5V, 15W output. The circuit uses a UCC3809 primary-side controller, which can also control other single-ended converters. The topology uses peak-current-mode control with a fixedfrequency oscillator. The design is cost-efficient, because it assumes that compensation of the voltage loop occurs on the secondary side, where you would place the error amplifier and reference anyway. By eliminating a primary-side amplifier, you reduce system cost and complexity.

The feedback signal from the secondary comes from the UC3965 precision refer-

ence. In addition to a low-offset error amplifier, this IC also contains an optocoupler driver for simplicity in designing isolated converters. An undervoltage-lockout circuit provides a controlled start-up transient. The design in Figure 1 uses discontinuous-conduction mode (in which the flyback transformer undergoes complete demagnetization in every cycle), with maximum duty cycle set to 50%. Continuous-mode flyback circuits (in which the flyback transformer operates in continuous inductor-current mode) have a righthalf-plane zero that limits the control bandwidth, as opposed to discontinuousmode flybacks that do not restrict bandwidth.

Both ICs operate in either mode; the

choice of mode depends on the powersupply requirements. You can easily buffer the primary-side oscillator with an emitter follower to provide slope compensation for designs requiring duty cycles beyond 50%. Note, however, that you have the option of programming a duty-cycle clamp to 50% or less, which can save cost by eliminating several slope-compensation components. The maximum-dutycycle clamp in the UCC3809 is completely programmable by selecting the two resistors connected to pins 3 and 4. (DI #2288)

> To Vote For This Design, Circle No. 433

A discontinuous-mode flyback regulator provides an isolated, regulated supply, and saves cost by cutting compensation components.

**118** EDN | JANUARY 7, 1999

Edited by Bill Travis and Anne Watson Swager

## RISC $\mu$ P implements fast FIR filter

Sorin Zarnescu, NEC Electronics, Santa Clara, CA

HEN IT COMES TO implementing a fast FIR filter, current RISC μPs can compete with DSP μPs. The FIR algorithm continuously implements the following equation:

N=n-1

Out=Sum[in(t[-]n)coeff(n)] N=0,

where N is the number of taps, or the number of multiply-accumulate (MAC) instructions of the filter.

Using a delay line to implement this equation is common and involves the ability to manage a circular buffer. Specialized DSP  $\mu$ Ps have can manage this task in hardware, and general-purpose  $\mu$ Ps have to implement the buffer management in software. As you might expect, the software implementation is significantly slower than the hardware one. However, modern RISC  $\mu$ Ps operating at high speeds and with features lacking in

previous generations of generalpurpose  $\mu$ Ps can compete in price and performance at executing these types of algorithms.

For example, consider the following algorithm, which you can implement using the V832 RISC processor (NEC Electronics, www.el.nec.com), which runs at 144 MHz. This µP features large internal

| RISC µP imple              | ements fast FIR filter             |

|----------------------------|------------------------------------|

| 1 5                        | hm transforms filter<br><b>120</b> |

| Door/window :<br>tampering | sensor resists<br><b>120</b>       |

| Use a trick to c           | count scope events                 |

| ,                          | inary-arithmetic<br><b>124</b>     |

| Light powers is            | solation amplifier128              |

| 2011 0000100000            | back circuit boosts<br>            |

#### LISTING 1-RISC-µP FAST-FIR ROUTINE

**Ideas**

.data .align 4 .global M1,M2,M3,M4,New

| .set   | 0x00; coef 1                                         |                                                                                                                                                                                                                                   |

|--------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| .set   | 0x10; coef 2                                         |                                                                                                                                                                                                                                   |

| .set   | 0x20; coef 3                                         |                                                                                                                                                                                                                                   |

| .set   | 0x30; coef 4                                         |                                                                                                                                                                                                                                   |

| .hword | 0x0010                                               | ; first sample                                                                                                                                                                                                                    |

| .hword | 0x0020                                               | ; second sample                                                                                                                                                                                                                   |

| .hword | 0x0030                                               | ; third sample                                                                                                                                                                                                                    |

| .hword | 0x0040                                               | ; fourth sample                                                                                                                                                                                                                   |

| .hword | 0x0050                                               | ;new sample - written by the interrupt routine                                                                                                                                                                                    |

|        |                                                      |                                                                                                                                                                                                                                   |

|        |                                                      |                                                                                                                                                                                                                                   |

|        | .set<br>.set<br>.hword<br>.hword<br>.hword<br>.hword | .set         0x10; coef 2           .set         0x20; coef 3           .set         0x30; coef 4           .hword         0x0010           .hword         0x0020           .hword         0x0030           .hword         0x0040 |

| ld.h | M1[r0],r1; load first sample into register 1                  |

|------|---------------------------------------------------------------|

| ld.h | M2,[r0]r2; load second sample into register 2                 |

| muli | c1,r1,r1 ;(coef 1 x sample 1) → accumulator                   |

| st.h | r1,M1[r0]; store first sample into the second memory location |

| ld.h | M3[r0],r3; load third sample into register 3                  |

| maci | c2,r2,r1 ; (coef 2 x sample 2) + accumulator → accumulator    |

| st.h | r2,M3[r0]; store second sample into third memory location     |

| ld.h | M4[r0],r4 ; load 1st sample                                   |

| maci | c3,r3,r1 ; (coef 3 x sample 3) + accumulator → accumulator    |

| st.h | r3,M4[r0]; store third sample into last memory location       |

| maci | c4,r4,r1; (coef 4 x sample 4) + accumulator -> accumulator    |

#### The trick to the RISC- $\mu$ P FIR algorithm is to store the data back into a memory location that's shifted by one position.

memories, the ability to execute instructions from internal memory in one clock cycle, and the ability to execute one MAC instruction in one clock cycle. The algorithm is not new, but it takes advantage of these features.

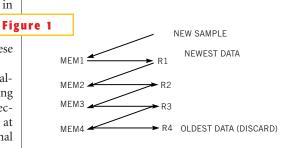

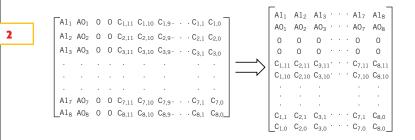

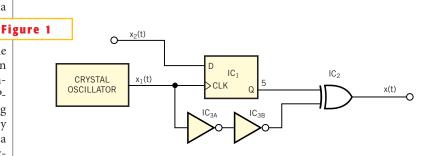

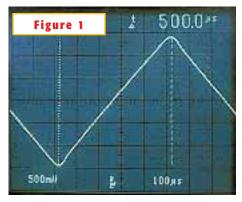

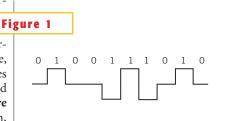

The algorithm runs linearly with no loops and implements the circular buffer with the addition of load/store instructions. Because the V832 is a RISC processor, arithmetic operations can take place only between registers. When a new sample is available, data loads from memory into the registers; the algorithm operates on the data and then stores it back in memory. The trick is to store the data back into the memory but shifted by one position. For the simple case of a four-tap filter, the algorithm looks like **Figure 1**.

For each tap, the processor needs to execute only ld.h (load the sample into the register), maci (multiply-accumulate immediate, in which the immediate value is the coefficient), and st.h (store the register back into the memory according to **Figure 1**).

Listing I comprises sample code for a four-tap FIR filter. (You can download this listing from *EDN*'s web site, www.ednmag.com. At the registereduser area, go into the Software Center to download the file from DI-SIG, #2313.) The instruction arrangement minimizes the dependencies inherent in a pipeline-based µP. The next time the program

executes, all of the samples are in the right position, assuming that the ADC interrupt routine writes the new sample into M1 before calling the filter routine. Regardless of the number of taps, the program takes three clock cycles per tap, which in the case of the V832 translates into 21 nsec/tap and occupies 3N memory locations. (DI #2313).

> To Vote For This Design, Circle No. 385

www.ednmag.com

designideas

## Simple algorithm transforms filter coefficients

Frank Vitaljic, Bellingham, WA

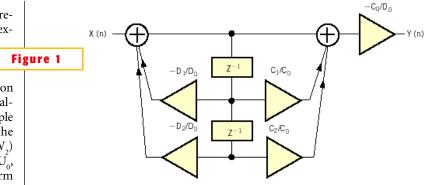

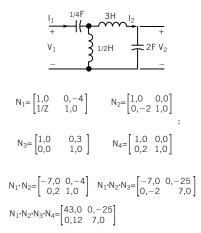

**T** O SYNTHESIZE INFINITE-impulse-response (IIR)-filter functions, expressed as H(z), you commonly use analog prototype-filter functions, expressed as H(s), using the bilinear-z transform. This operation entails some algebraic complexity in calculating the filter coefficients. The simple algorithm shown here transforms the prototype-filter coefficients ( $W_0$ ,  $W_1$ ,  $W_2$ ) to the IIR digital-filter coefficients ( $U_0$ ,  $U_1$ ,  $U_2$ ). These coefficients transform from the s (analog) domain to the z (digital) domain as:

$$W_0 + W_1 s + W_2 s^2 \rightarrow U_0 + U_1 z^{-1} + U_2 z^{-2}$$

The filter conventions are:

$$H(s) = \frac{A_0 + A_1 s + A_2 s^2}{B_0 + B_1 s + B_2 s^2}, \text{ and}$$

$$H(z) = \frac{C_0 + C_1 z^{-1} + C_2 z^{-2}}{D_0 + D_1 z^{-1} + D_2 z^{-2}},$$

where the numerator and denominator polynomials undergo independent transformation. The matrix equations are

$$[U_0U_1U_2]^{T} = M[W_0W_1W_2]^{T}$$

, and

$$[W_0 W_1 W_2]^{T} = M^{-T} [U_0 U_1 U_2]^{T},$$

where

$$\mathbf{M} = \begin{bmatrix} 1/4 & 1/2 & 1\\ 1/2 & 0 & -2\\ 1/4 & -1/2 & 1 \end{bmatrix} \quad \mathbf{M}^{-1} = \begin{bmatrix} 1 & 1 & 1\\ 1 & 0 & -1\\ 1/4 & -1/4 & 1/4 \end{bmatrix},$$

You combine biquad sections in cascade to form high-order IIR digital filters.

and, for first-order filters,

$M = \begin{bmatrix} \frac{1}{2} & 1\\ \frac{1}{2} & -1 \end{bmatrix} \qquad M^{-1} = \begin{bmatrix} 1 & 1\\ \frac{1}{2} & -\frac{1}{2} \end{bmatrix}.$

These equations assume that the prototype filter is normalized with respect to the sampling frequency,  $f_s$ . For example, design a second-order Butterworth unity-gain, lowpass IIR filter with cutoff frequency,  $f_{C}$ =100 Hz, and sampling rate,  $f_s$ =1000 Hz. First, you use  $C_w$  to frequency-scale the Butterworth prototype (in normalized form,  $C_w$ =1). The expression for  $C_w$  is

$$C_{\rm W} = 2\tan\left(\pi \frac{f_{\rm C}}{f_{\rm S}}\right)\pi \frac{f_{\rm C}}{f_{\rm S}} =$$

$$2\tan(0.1\pi) = 0.649839$$

rad/sec.

The prototype filter is thus

$$H(s) = \frac{0.4223}{0.4223 + 0.919s + s^2}$$

Now, calculate the IIR coefficients using the transform in **equations 1** and **2**:

| $\begin{bmatrix} C_0 \\ C_1 \\ C_2 \end{bmatrix} =$ | 0.25 | 0.5  | 1  | 0.4223 | ] | 0.1056  |   |

|-----------------------------------------------------|------|------|----|--------|---|---------|---|

| C <sub>1</sub> =                                    | 0.5  | 0    | -2 | 0      | = | 0.2112  | ; |

| $C_2$                                               | 0.25 | -0.5 | 1  | 0      |   | 0.1056  |   |

|                                                     |      |      |    |        |   |         |   |

| $\begin{bmatrix} D_0 \end{bmatrix}$                 | 0.25 | 0.5  | 1  | 0.4223 | ſ | 1.5651  | ] |

| D <sub>1</sub> =                                    | 0.5  | 0    | -2 | 0.9190 | = | -1.7889 | ŀ |

| $\begin{bmatrix} D_0 \\ D_1 \\ D_2 \end{bmatrix} =$ | 0.25 | -0.5 | 1  | 1.0000 |   | 0.6461  |   |

|                                                     |      |      |    |        |   |         |   |

**Figure 1** gives the filter's flow diagram. (DI #2287).

To Vote For This Design, Circle No. 386

### **Door/window sensor resists tampering**

(1)

(2)

Paul Nocella, Q Research, Brookline, NH

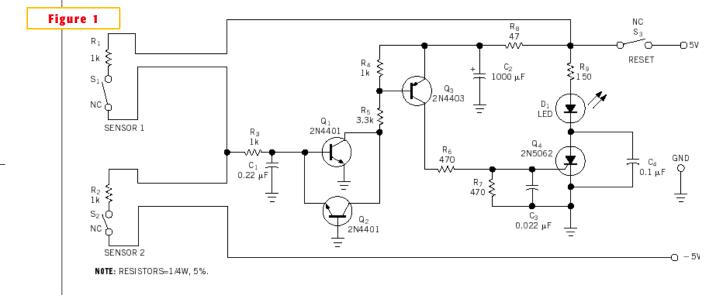

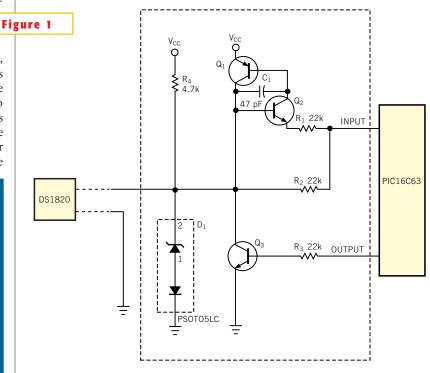

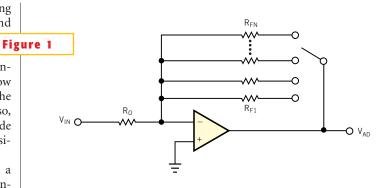

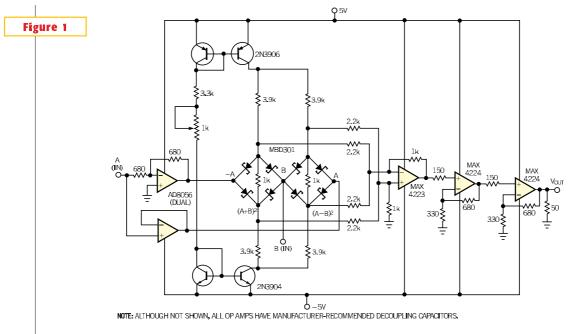

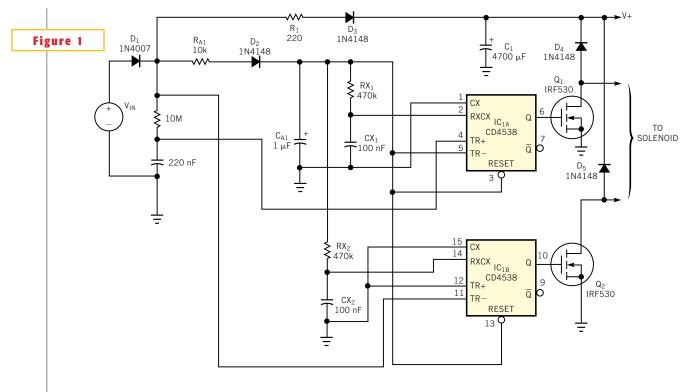

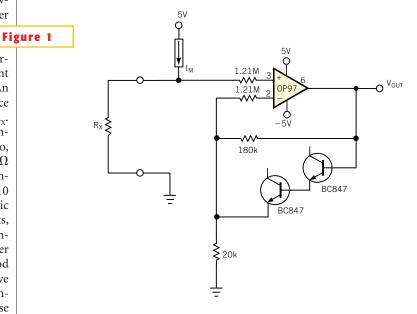

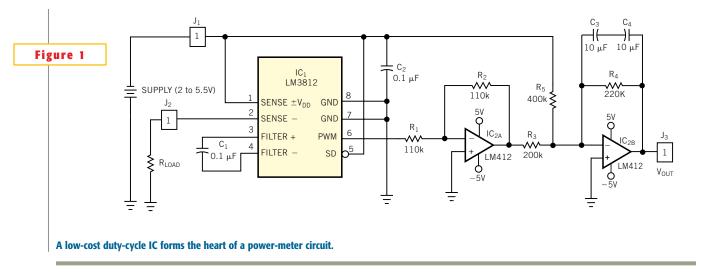

**T**HE SIMPLE, INEXPENSIVE circuit in **Figure 1** detects a failure (or deliberate tampering) on lines connected to normally closed switch sensors. For example, common door interlocks and door/window sensors consist of normal-

ly open or normally closed magnetic reed switches. Depending on the monitoring configuration, an open or short on a line may go undetected, thus preventing alarm activation. Embedding a resistor in a normally closed sensor and using bipolar dc power supplies produces the balanced configuration in **Figure 1**. A short or open on a line (or sensor activation) produces a net positive or negative voltage at the input of the  $Q_1$ - $Q_2$  pair.

A positive-voltage imbalance turns Q<sub>1</sub>

## designideas

on; a negative-voltage imbalance turns  $Q_2$ on. The back-to-back clamping action of the base-emitter junctions of  $Q_1$  and  $Q_2$ protects the transistors from excessive reverse VBE voltages. The clamping prevents intrinsic base-emitter zener breakdown.  $R_3$  limits the input current to  $Q_1$ and  $Q_2$  in the event of a line short. The collectors of  $Q_1$  and  $Q_2$  form a wired-OR configuration that turns  $Q_3$  on by pulling its base toward ground.  $Q_3$  provides gate current to trigger the alarm, SCR  $Q_4$ , which can handle several hundred milliamperes.  $Q_4$  can drive a variety of alarm indicators, including LEDs, piezoelectric buzzers, or relays that control high-power alarms.

It's easy to add monitoring locations, simply by adding sensors in pairs and replicating the  $Q_1$ - $Q_2$  circuit configuration, including the wired-OR connection to  $R_5$ . With power-supply voltages of ±5V, worst-case resistor tolerances of ±5% and a 2.5% supply imbalance do not cause  $Q_1$  or  $Q_2$  to turn on. The ±5V supplies should rise approximately simultaneously; otherwise, a net voltage imbalance would appear at the input of  $Q_1$  and  $Q_2$ , resulting in alarm activation. Momentarily opening  $S_3$  resets  $Q_4$  by interrupting its anode current.  $C_2$  provides a small time delay to allow the voltage at the input of  $Q_1$  and  $Q_2$  to stabilize before enabling  $Q_3$ .  $C_1$ ,  $C_3$ , and  $C_4$  prevent stray ac pickup or transients from triggering  $Q_4$ . (DI #2286).

> To Vote For This Design, Circle No. 387

Normally closed sensor pairs form the detectors in a tamper-resistant and foolproof window/door security system.

#### Use a trick to count scope events

Allen Montijo, Hewlett-Packard, Colorado Springs, CO

**O** NE ADVANTAGE DIGITAL storage oscilloscopes (DSOs) have over analog scopes is trace persistence. You can easily see infrequent waveform features using a scope in infinite-persistence mode. However, the frequency of these features relative to that of a "normal" signal can sometimes be less than obvious. You may wonder, does that glitch appear 10% or only 1% of the time? And how often does that short clock cycle occur? When you take trace noise into account, even a color-graded display does not directly or accurately give the information. A histogram is the

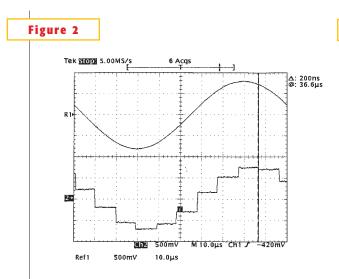

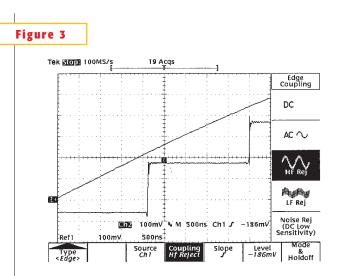

most accurate way to give the information, but it requires time and expertise. The following hint provides a quick way to determine, using a DSO, how often each of two waveforms occurs.

First, use a standard nonaveraging mode to find the voltages of the two states at a fixed point in time  $(V_1 \text{ and } V_2)$ . Now, turn averaging on using a large number of averages. After the trace settles, measure the average level $(V_A)$ . The percentage of time the signal at  $V_2$  is:

$$\frac{\frac{V_{A} - V_{1}}{V_{2} - V_{1}} \times 100\%}{15}.$$

The accuracy of your answer depends on the accuracy of your  $V_1$ ,  $V_2$ , and  $V_A$ measurements. To increase the accuracy of  $V_A$ , simply increase the number of averages on the scope. If you can use your DSO's advanced triggering capabilities to trigger on only one waveform, then you can use the DSO's averaging mode to make more accurate measurements of  $V_1$ ,  $V_2$ , or both. (DI #2298).

> To Vote For This Design, Circle No. 388

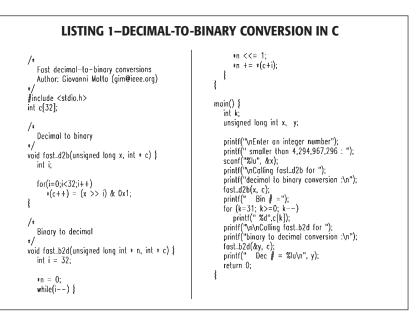

## A primer on binary-arithmetic rounding

Tom Balph, Motorola SPS, Tempe, AZ

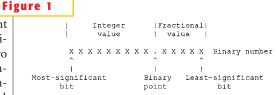

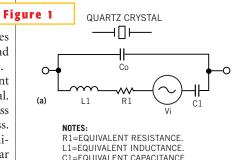

A S DIGITAL COMMUNICATIONS and data compression/decompression proliferate, signal-processing functions grow in importance. Whether you're dealing with hard-wired logic or programmable engines, an understanding of binary-arithmetic rounding is important in getting correct and consistent results. Before we discuss rounding, consider a binary number (**Figure 1**).

At first glance, rounding seems a simple matter. However, several variations on rounding exist. Depending on the application, you may use one of the following techniques:

- Truncation (round to minus infinity)—This form of rounding ignores any information in the fractional value to the right of the binary point. You discard these bits, leaving the integer value to the left of the binary point unaffected. Truncation is also called round to minus infinity because it has the effect of rounding to the more negative number. Truncation is in wide use because it is simple to implement: Just ignore the unused bits.

- Round to plus infinity—This variation is essentially the inverse of truncation. If the fractional value to the right of the binary point is not exactly zero, then you round up (make more positive) the integer value. The implementation is more complex than truncation, because you must test all the fractional bits for the existence of a one and then increment the integer value if you find a one.

- Round to zero—Round to zero applies to 2's complement numbers. (For the case of positive numbers only, round to zero reduces to truncation.) For negative numbers, this rounding technique depends on the fractional value—the existence of any nonzero LSBs causes a round up to a less negative number. The positive-number case is simply truncation. The implementation must consider both the fractional-number value and the sign bit.

You increment the integer value only when the sign bit equals one (negative number) and the fractional value is not zero.

- Up-magnitude (round to infinity)-Up-magnitude is the inverse of round to zero and applies to 2's complement numbers. If the number is positive, round up for any fractional number not equal to zero. If the number is negative, round down (truncate) for any fractional number not equal to zero. This algorithm is perhaps most useful for maintaining the largest possible magnitude for digital-to-analog conversion. The technique finds use in recent standards, such as ISO/IEC 11172-3 MPEG audio. Implementation again considers the sign and fractional values: Increment the integer only when the sign bit equals zero (positive number) and the fractional value is not zero.

- Simple round (2's complement round)—Simple round applies to both magnitude-only and 2's-complement numbers. You round up the integer value for all fractional values greater than or equal to half the fullscale value of the fractional number. Half the full-scale value is a one and all zeros at the right of the binary point. For fractional values lower than half full-scale, the integer number remains unchanged (truncation). Implementation is relatively simple in that you can add a one to

A binary number can consist of any number of bits with the binary point at any bit position. All bits to the left of the binary point are the integer, or most-significant, bits of the number. All bits to the right of the point are the fractional, or least-significant, bits of the number. For 2's complement numbers, the most-significant bit has a negative binary weight and is the sign bit. If no sign bit exists, the number is magnitude only and unsigned.

the number at the bit position directly to the right of the binary point. This action increments the integer for any fractional value equal to or greater than half the fractional full-scale value.

Convergent round—Convergent round is similar to simple round. The difference has to do with the half-full-scale value of the fractional number. A fractional number greater than half full-scale always causes rounding up of the integer number, a fractional number less than half full-scale causes the integer to remain unchanged, and a fractional number equal to half fullscale causes the integer to round up to the nearest even value. Convergent round is most useful for iterative processes in which cumulative addition causes errors to occur more readily. Implementation requires testing the fractional value, as well as the LSB of the integer number. The integer number increments if the fractional value is greater than half full-scale or if the fractional value equals half full-scale and the integer LSB is one (producing an odd number).

**Listing 1** illustrates the rounding methods using Verilog HDL. A 12-bit number, "x," with the binary point located to the left of Bit 3 serves as the input (yielding an 8-bit integer and a 4bit fraction). Each of the rounded results are 8-bit integer numbers. Part A

> of Listing 1 is the module listing, which defines and exercises the rounding outputs and displays the results. Part B gives the displayed simulation results, which you can use to observe the rounding differences. Be aware that, although this HDL routine is fully synthesizable, the resulting logic may not deliver the best performance or be the minimum configuration. You can download Listing 1 from EDN's Web site, www.ednmag.com. At the registered-user area, go into the Software Center to down-

## designideas

load the file from DI-SIG, #2285.

When you implement rounding, performance can suffer if an additional add occurs, because of the rounding algorithm. At times, however, the logic producing the original number can hide the additional add. As an example, if you use simple round (2's complement round) with a multiplier to round the results, a constant one can appear in the partial-product array (at the proper location), and summing the one along with all the partial products produces no loss in performance. Here, the increment of the integer product is buried in the multiplier-adder array. (DI #2285).

To Vote For This Design, Circle No. 389

#### LISTING 1–ROUNDING EXAMPLES USING VERILOG HDL

| A) Module listing                                                                                                           | x = 12'h008;<br>#10; \$display("x = %h trunc = %h plus_inf = %h zero = %h up_mag = %h twos_comp = %h                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| # File : round.v                                                                                                            | converg = %h",<br>x,trunc,plus_inf,zero,up_mag,twos_comp,converg);                                                                                                       |

| module test;                                                                                                                | x = 12'h018;<br>#10; \$display("x = %h trunc = %h plus_inf = %h zero = %h up_mag = %h twos_comp = %h                                                                     |

| reg [11:0] x;                                                                                                               | converg = %h°,                                                                                                                                                           |

| # Simple truncation                                                                                                         | x,trunc,plus_inf,zero,up_mag,twos_comp,converg);                                                                                                                         |

| wire [7:0] trunc = x[11:4];                                                                                                 | x = 12'h808;<br>#10; \$display("x = %h trunc = %h plus_inf = %h zero = %h up_mag = %h twos_comp = %h                                                                     |

| // Round-to-plus-infinity // Increment the integer when the fraction is not equal to zero.                                  | converg = %h",<br>x,trunc,plus_inf,zero,up_mag,twos_comp,converg);                                                                                                       |

| wire [7:0] plus_inf = (x[3:0] == 4'h0)? x[11:4] : x[11:4] + 8'h01;                                                          | x = 12'h818;<br>#10; \$display("x = %h trunc = %h plus_inf = %h zero = %h up_mag = %h twos_comp = %h                                                                     |

| # Round-to-zero $#$ lncrement the integer when a negative number and the fraction is not equal to zero.                     | converg = %h*,<br>x,trunc,plus_inf,zero,up_mag,twos_comp,converg);                                                                                                       |

| wire [7:0] zero = (x[11] & (x[3:0] != 4'h0))? x[11:4] + 8'h01 : x[11:4];                                                    | x = 12'h019;<br>#10; \$display("x = %h trunc = %h plus_inf = %h zero = %h up_mag = %h twos_comp = %h                                                                     |

| # Up-magnitude round $#$ Increment the integer when a positive number and the fraction is not equal to zero.                | converg = %h",<br>x,trunc,plus_inf,zero,up_mag,twos_comp,converg);                                                                                                       |

| wire [7:0] up_mag = (~x[11] & (x[3:0] != 4'h0))? x[11:4] + 8'h01 : x[11:4];                                                 | x = 12'h819;<br>#10; \$display("x = %h trunc = %h plus_inf = %h zero = %h up_mag = %h twos_comp = %h                                                                     |

| // 2's Complement round // Add fractional number 4'h8 to original number before using integer                               | converg = %h",<br>x,trunc,plus_inf,zero,up_mag,twos_comp,converg);                                                                                                       |

| wire [11:0] temp = x[11:0] + 12'h008;<br>wire [7:0] twos_comp = temp[11:4];                                                 | x = 12'h028;<br>#10; 5display!"x = %h trunc = %h plus_inf = %h zero = %h up_mag = %h twos_comp = %h<br>converg = %h",                                                    |

| // Convergent round<br>// Increment the integer when; a) fraction is greater than 4°h8,                                     | x,trunc,plus_inf,zero,up_mag,twos_comp,converg);                                                                                                                         |

| // or b) fraction = 4'h8 & integer is odd (lsb = 1).<br>reg [7:0] converg:                                                  | x = 12h828;<br>#10; \$display("x = %h trunc = %h plus_inf = %h zero = %h up_mag = %h twos_comp = %h<br>converg = %h",                                                    |

|                                                                                                                             | x,trunc,plus_inf,zero,up_mag,twos_comp,converg);                                                                                                                         |

| always @( x )                                                                                                               | x = 12'h029:                                                                                                                                                             |

| if (x[3:0] > 4'h8) converg = x[11:4] + 8'h01;                                                                               | #10; \$display("x = %h trunc = %h plus_inf = %h zero = %h up_mag = %h twos_comp = %h                                                                                     |

| else if ((x[3:0] == 4'h8) & (x[4])) converg = x[11:4] + 8'h01;<br>else converg = x[11:4];                                   | converg = %h",<br>x,trunc,plus_inf,zero,up_mag,twos_comp,converg);                                                                                                       |

| // display input and outputs                                                                                                | x = 12'h829;                                                                                                                                                             |

| initial                                                                                                                     | #10; \$display("x = %h trunc = %h plus_inf = %h zero = %h up_mag = %h twos_comp = %h<br>converg = %h",                                                                   |

| begin                                                                                                                       | x,trunc,plus_inf,zero,up_mag,twos_comp,converg);                                                                                                                         |

| x = 12'h000;<br>#10; \$display("x = %h trunc = %h plus_inf = %h zero = %h up_mag = %h twos_comp = %h                        | \$finish;<br>endmodule // test module                                                                                                                                    |

| converg = %h",<br>x,trunc,plus_inf,zero,up_mag,twos_comp,converg);                                                          |                                                                                                                                                                          |

| x = 12'h001;<br>#10; \$display("x = %h trunc = %h plus_inf = %h zero = %h up_mag = %h twos_comp = %h<br>convera = %h".      | B) Simulation results:                                                                                                                                                   |

| converg = ~n";<br>x,trunc,plus_inf,zero,up_mag,twos_comp,converg);                                                          | Compiling source file "round.v"                                                                                                                                          |

| x = 12'h800;<br>#10; \$display("x = %h trunc = %h plus_inf = %h zero = %h up_mag = %h twos_comp = %h                        | Highest level modules:<br>test                                                                                                                                           |

| converg = %h",<br>x,trunc,plus_inf,zero,up_mag,twos_comp,converg);                                                          | x = 000 trunc = 00 plus_inf = 00 zero = 00 up_mag = 00 twos_comp = 00 converg = 00<br>x = 001 trunc = 00 plus_inf = 01 zero = 00 up_mag = 01 twos_comp = 00 converg = 00 |

| x = 12'h801;                                                                                                                | x = 800 trunc = 80 plus_inf = 80 zero = 80 up_mag = 80 twos_comp = 80 converg = 80<br>x = 801 trunc = 80 plus_inf = 81 zero = 81 up_mag = 80 twos_comp = 80 converg = 80 |

| #10; \$display("x = %h trunc = %h plus_inf = %h zero = %h up_mag = %h twos_comp = %h<br>converg = %h",                      | x = 011 trunc = 01 plus_inf = 02 zero = 01 up_mag = 02 twos_comp = 01 converg = 01<br>x = 811 trunc = 81 plus_inf = 82 zero = 82 up_mag = 81 twos_comp = 81 converg = 81 |

| x,trunc,plus_inf,zero,up_mag,twos_comp,converg);<br>x = 12'h011;                                                            | x = 008 trunc = 00 plus_inf = 01 zero = 00 up_mag = 01 twos_comp = 01 converg = 00<br>x = 018 trunc = 01 plus_inf = 02 zero = 01 up_mag = 02 twos_comp = 02 converg = 02 |

| #10; \$display("x = %h trunc = %h plus_inf = %h zero = %h up_mag = %h twos_comp = %h                                        | x = 808 trunc = 80 plus_inf = 81 zero = 81 up_mag = 80 twos_comp = 81 converg = 80<br>x = 818 trunc = 81 plus_inf = 82 zero = 82 up_mag = 81 twos_comp = 82 converg = 82 |

| converg = %h",<br>x,trunc,plus_inf,zero,up_mag,twos_comp,converg);                                                          | x = 019 trunc = 01 plus_inf = 02 zero = 01 up_mag = 02 twos_comp = 02 converg = 02<br>x = 819 trunc = 81 plus_inf = 82 zero = 82 up_mag = 81 twos_comp = 82 converg = 82 |

| x = 12'h811;<br>#10; \$display("x = %h trunc = %h plus_inf = %h zero = %h up_mag = %h twos_comp = %h                        | x = 028 trunc = 02 plus_inf = 03 zero = 02 up_mag = 03 twos_comp = 03 converg = 02<br>x = 828 trunc = 82 plus_inf = 83 zero = 83 up_mag = 82 twos_comp = 83 converg = 82 |

| <pre>#ru; susplay( x = "on trunc = "on plus_int = "on zero = "on up_mag = "on twos_comp = "on<br/>converg = %h",<br/></pre> | x = 029 trunc = 02 plus_inf = 03 zero = 02 up_mag = 03 twos_comp = 03 converg = 03<br>x = 829 trunc = 82 plus_inf = 83 zero = 83 up_mag = 82 twos_comp = 83 converg = 83 |

|                                                                                                                             | L114 "round.v": \$finish at simulation time 160<br>161 simulation events                                                                                                 |

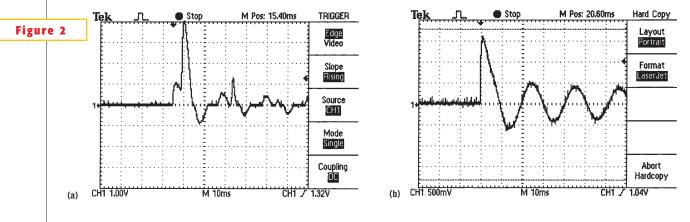

#### Light powers isolation amplifier

Stephen Woodward, University of North Carolina, Chapel Hill, NC

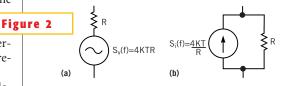

**S** ELF-POWERED isolation amplifiers, which need no external isolated power supply, provide versatile and convenient interfaces in many applications that require galvanic isolation of the signal source. Examples of such applications include circuits that serve in industrial or medical environments, in which isolation is necessary for noise reduction or safety. You can use a variety of isolated signal-coupling techniques for the signal paths of these amplifiers. Transformers, differential-capacitor, and optoisolator schemes are all popular choices. For the internal isolated power supply,

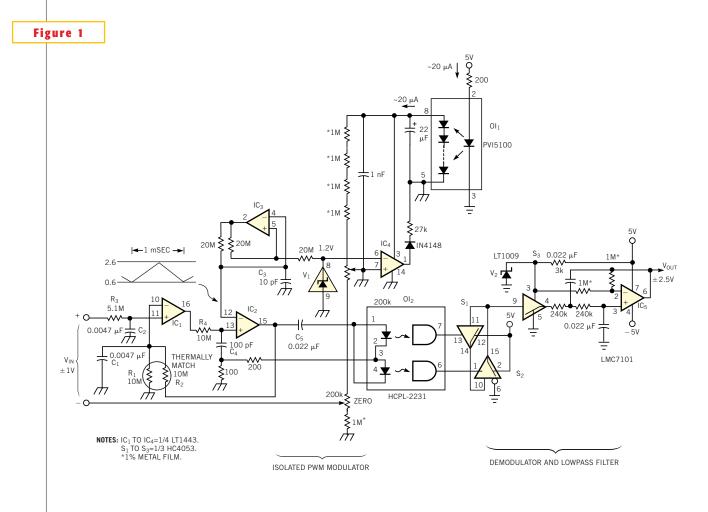

transformer coupling is virtually universal, despite the problems inherent in inductively coupled circuits. These problems include relatively high interwinding stray capacitance and a tendency to couple switching noise into the signal. In contrast, the self-powered amplifier in **Figure 1** is different in that it incorporates optoisolators to effect communication of both signal and power around the isolation barrier.

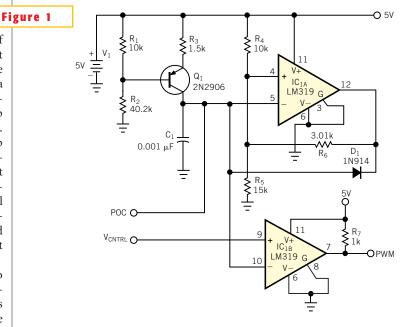

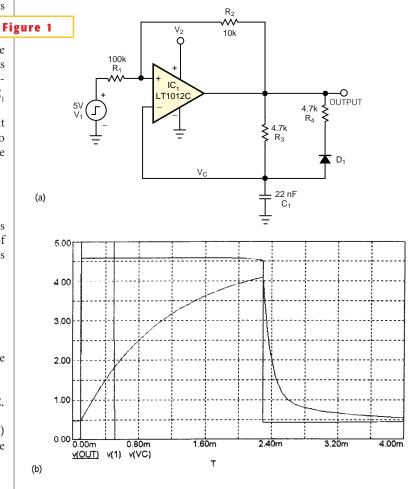

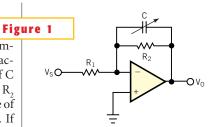

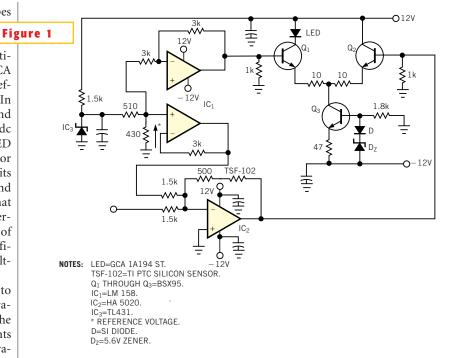

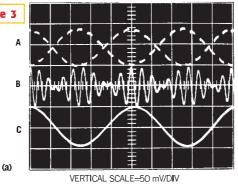

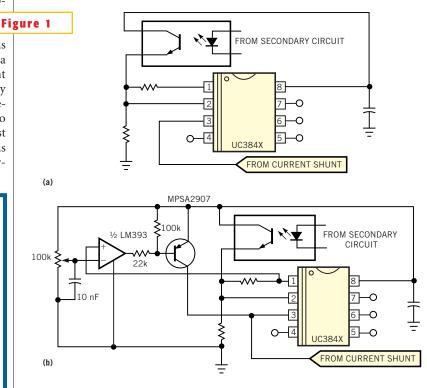

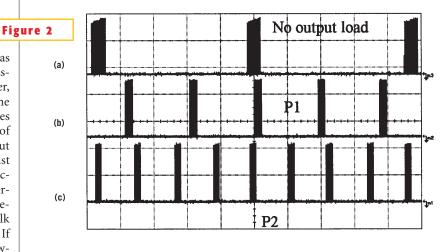

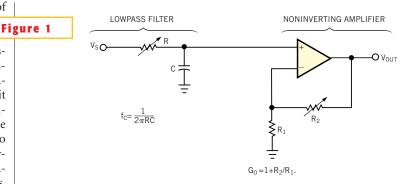

As in many isolation-amplifier designs, the signal processing in **Figure 1**'s circuit uses PWM. The isolated-modulator front-end circuitry derives from an earlier ADC design and works as follows.  $IC_1$  compares the ±1V filtered input signal with the voltage on  $C_1$ . The  $R_4C_4$  time constant smoothes  $IC_1$ 's output, and  $IC_2$  compares the output with  $IC_3$ 's approximately 1-kHz triangle waveform.  $R_1$ ,  $R_2$ , and  $C_1$  scale and average the resulting variable-duty-factor square wave and feed the signal back to  $IC_1$ . This feedback loop continuously adjusts  $IC_2$ 's duty factor to maintain equal voltages on  $C_1$  and  $C_2$ . In doing so, the feedback forces  $IC_2$ 's output square wave to track the unique  $T_+/(T_++T_-)$  duty factor that maintains balance at  $IC_1$ 's inputs.

A virtual perpetual-motion machine (when there's light), this self-powered amplifier provides complete galvanic isolation for both power and signal.

**128** EDN | JANUARY 21, 1999

## designideas

$C_5$  differentiates the IC<sub>2</sub> square wave to provide bipolar drive pulses to the antiparallel LEDs in the high-speed, lowcurrent optoisolator OI<sub>2</sub>. In turn, OI<sub>2</sub> produces ground-referred pulses. The rather unusual RS flip-flop formed by cross-connected switches S<sub>1</sub> and S<sub>2</sub> converts these pulses back to a logic-level square wave having the same duty factor as IC<sub>2</sub>'s output. Demodulation and filtering of the square wave to accurately reproduce the original analog signal occurs through the action of the single-pole, double-throw switch, S<sub>3</sub>, which chops the 2.500V V, reference voltage according to the  $T_{+}/(T_{+}+T_{-})$  square-wave duty factor. The lowpass, gain-of-two filter,  $IC_{5^{2}}$  then extracts the dc component of  $S_{3}$ 's 0 to 2.5V waveform and scales and offsets it to produce a low-ripple,  $\pm 2.5V$  signal, according to the formula

$V_{\rm O} = 2.5 \times T_+ \; / (T_+ + T_-) = 2.5 \times V_{\rm IN} \, . \label{eq:VO}$

Power for the isolated-modulator side of the amplifier comes from  $OI_1$ , an International Rectifier (El Segundo, CA) PVI5100 photovoltaic opto IC. Marketed as an isolated MOSFET-gate driver, the PVI5100 can source approximately 20  $\mu$ A of current at 4V (80  $\mu$ W), just enough to keep the anorexic LT1443 alive and functional. IC<sub>4</sub> shunt-regulates OI<sub>1</sub>'s output to provide a stable 4V ratioed against the MAX924's 1.2V $\pm$ 1% internal reference. Overall frequency response is dc to 10 kHz; input impedance is approximately 1 T $\Omega$  with less than 1-pA bias. The circuit can thus provide good overall accuracy with high-impedance input sources. You can trim gain and offset errors to zero; the excellent drift specs of the LT1443 maintain the trim over temperature. (DI #2304).

> To Vote For This Design, Circle No. 390

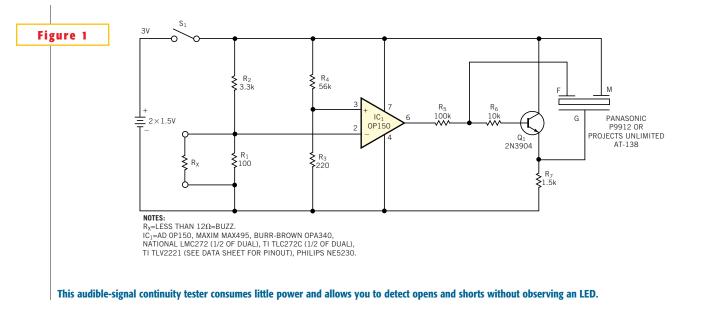

#### Low-cost feedback circuit boosts efficiency

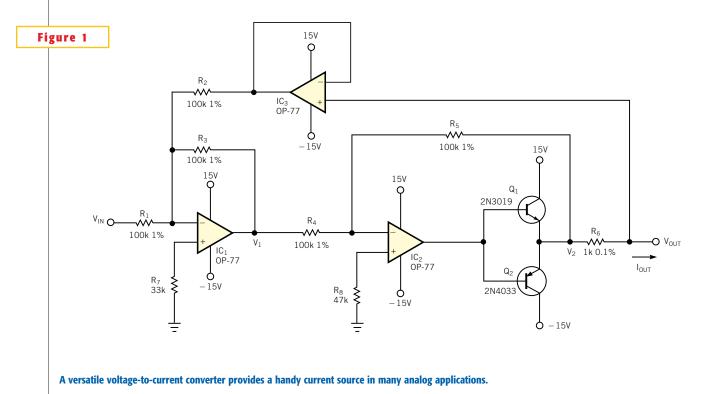

John Guy, Maxim Integrated Products, Sunnyvale, CA

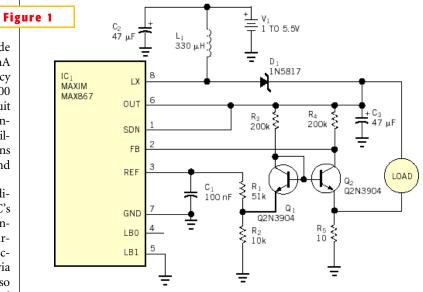

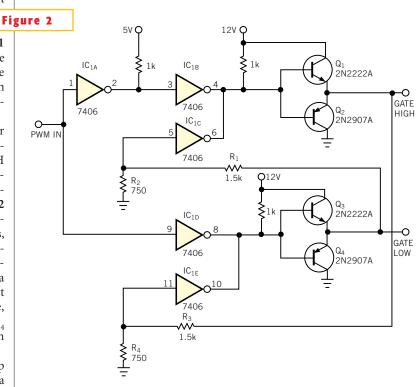

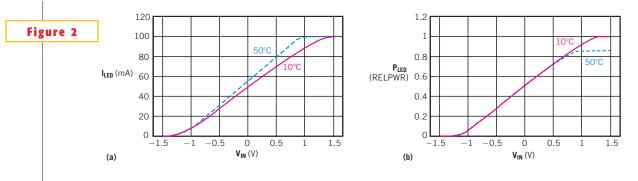

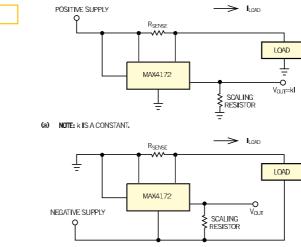

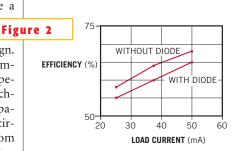

**T** O IMPLEMENT A STEP-UP converter with a current output, designers often simply connect the load in place of the top resistor in a resistive-divider feedback network. The bottom resistor then serves as a current-sense resistor. Though simple, this approach is ineffi-

cient. Low efficiency results from the relatively high sense voltages—usually, 1.25V but as high as 2.5V for some ICs. A switch-mode dc/dc converter configured as a 20-mA current source minimizes the efficiency loss by lowering the sense voltage to 200 mV (**Figure 1**). Advantages of this circuit include the factor-of-six gain in efficiency; minimal board area; and readily available, low-cost components. Applications include battery charging, LED drive, and general-purpose current sources.

Resistors  $R_1$  and  $R_2$  form a voltage divider that derives 200 mV from the IC's reference output. This sense voltage connects to one emitter of the current mirror comprising  $Q_1$  and  $Q_2$ . Both collectors connect to the output voltage via 200-k $\Omega$  resistors. The collector of  $Q_2$  also connects to the IC's feedback pin, and  $Q_2$ 's emitter connects to the low-side current-sense resistor,  $R_5$ . The feedback network appears to the IC's control loop as

a common-base amplifier. Selecting a 2N3904 for  $Q_2$  yields sufficient emitterto-collector gain for the purpose: approximately 80V/V. Moreover, the network's large bandwidth (characteristic of

common-base configurations) prevents instability in the IC's control loop. (DI #2307).

To Vote For This Design, Circle No. 391

Edited by Bill Travis and Anne Watson Swager

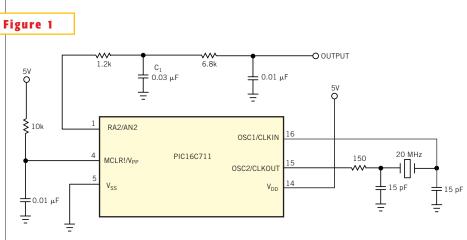

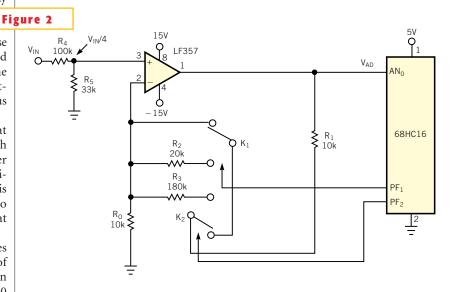

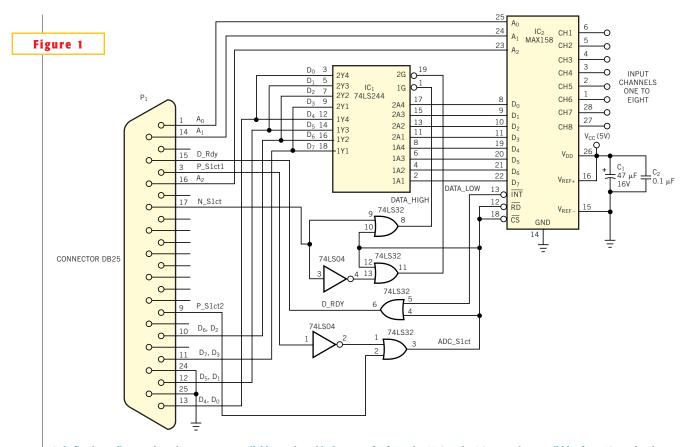

### ADC circuit optimizes key encoding

Vitor Amorim, Siemens, and J Simões, University of Coimbra, Coimbra, Portugal

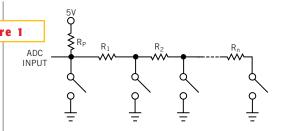

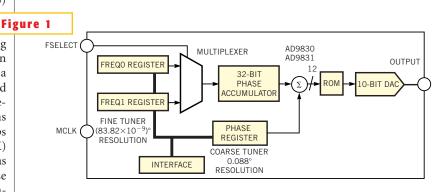

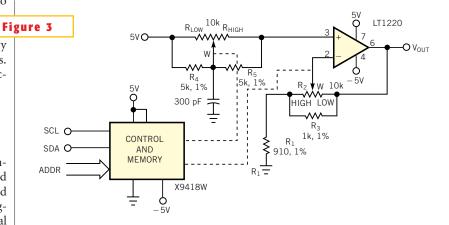

OU CAN IMPLEMENT a simple and

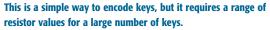

**Figure 1** low-cost keyboard encoder by using a key-controlled resistive divider connected to an ADC (**Figure 1**). This type of circuit is especially suitable for embedded systems that use a  $\mu$ C with an integrated ADC section. To obtain the best noise margin between keys, select resistors to yield an equal division of the voltage levels. To meet this criterion using the circuit in **Figure 1**, you must use a set of resistors

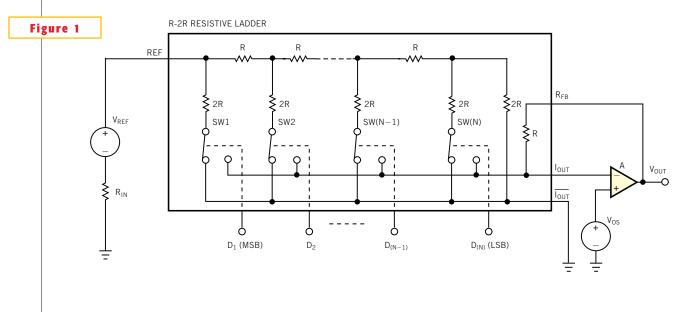

with all-different, specific values. For example, a 10-key **Figure 2** keyboard uses a 10-k $\Omega$  pullup resistor, R<sub>p</sub>, and values of 1.1, 1.3, 1.8, 2.4, 3.3, 5.1, 8.2, 16, and 51 k $\Omega$  for R<sub>1</sub> through R<sub>9</sub>. Using commonly available resistor values and tolerances and taking account of the key resistivity and ADC linearity errors, you're limited in the number of keys you can encode with a safe noise margin. Using an 8-bit ADC, the cited 10-key example is close to that limit.

The circuit in **Figure 2**, despite its many resistors, overcomes the problem of the many restore values. The circuit is symmetric and uses the same two resis-

| ADC circuit optimizes key encoding             | 101 |

|------------------------------------------------|-----|

| RS-232C circuit has galvanic<br>isolation      | 102 |

| Digital pot adjusts LCD's contrast             | 104 |

| Add speech encoding/decoding<br>to your design | 106 |

| Cheap PWM IC makes synchronous gate driver     | 110 |

| Circuit detects total on-time                  | 112 |

deas

#### This key-encoding circuit simplifies resistor inventories, and provides a comfortable noise margin to boot.

tor values for all keys. It is also easy to expand the circuit for more keys. As in **Figure 1**'s circuit, if you simultaneously press more than one key, the circuit detects only the key whose connection is closest to the ADC. The chain of R<sub>1</sub> resistors de-

fines the voltage level associated with each key. Their nominal value is a trade-off between the power dissipation and the values of  $R_2$ and  $R_3$ , which depend on  $R_1$ ; the total number of keys; and the desired noise margin.  $R_2$  minimizes the voltage deviations at the nodes of the  $R_1$  chain whenever you simultane-

ously press two or more keys. Therefore, you should calculate its value, much higher than that of  $R_1$ , by taking into account  $R_1$  and the desired width of the voltage window associated with each key. Similarly,  $R_3$ 's value should be much higher than that of  $R_2$  to ensure that the voltage level associated with each key almost completely transfers to the ADC's input.

The circuit was tested by encoding 15 keys with one 8-bit analog input of the Microchip PIC16C71  $\mu$ C. The resistor values are 47 $\Omega$ , 3.9 k $\Omega$ , and 4.7 M $\Omega$ for R<sub>1</sub>, R<sub>2</sub>, and R<sub>3</sub>, respectively. Only R<sub>1</sub> needs a tight tolerance; the others are less demanding. The window of key acceptance is set to a 7-LSB interval centered on the theoretical key level. This interval is large enough to accommodate the worst case (simultaneously pressing the two

more-distant keys from the analog input) with a safety noise margin between valid keys of 10 LSBs. (DI #2319).

To Vote For This Design, Circle No. 332

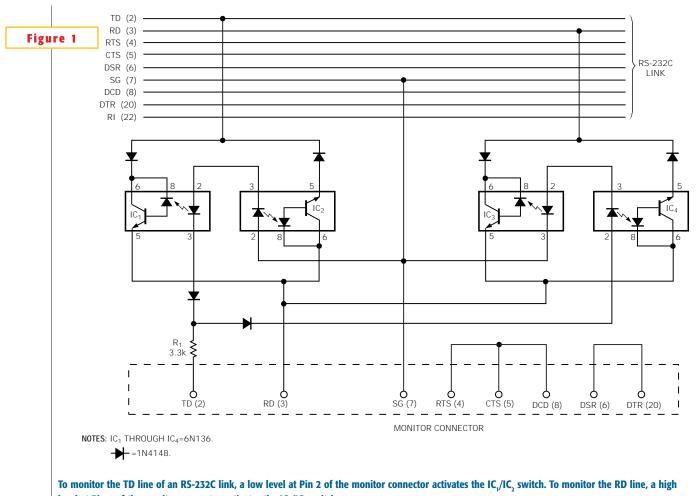

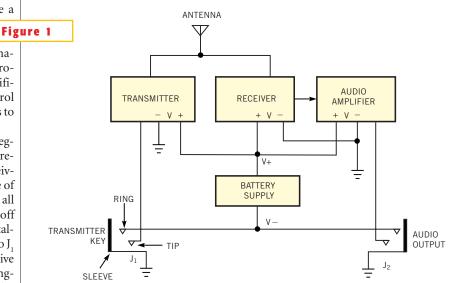

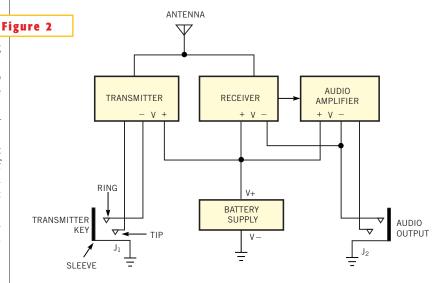

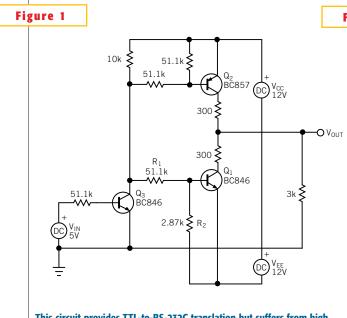

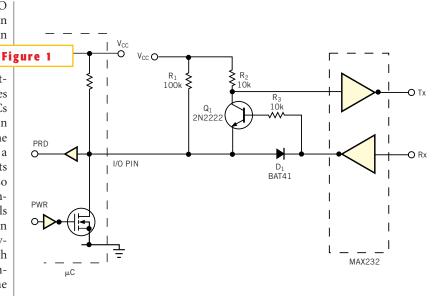

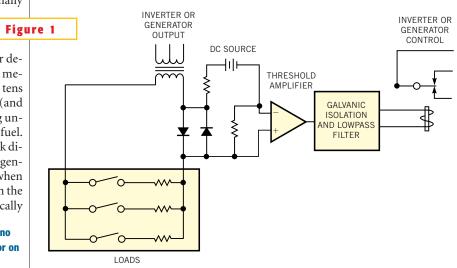

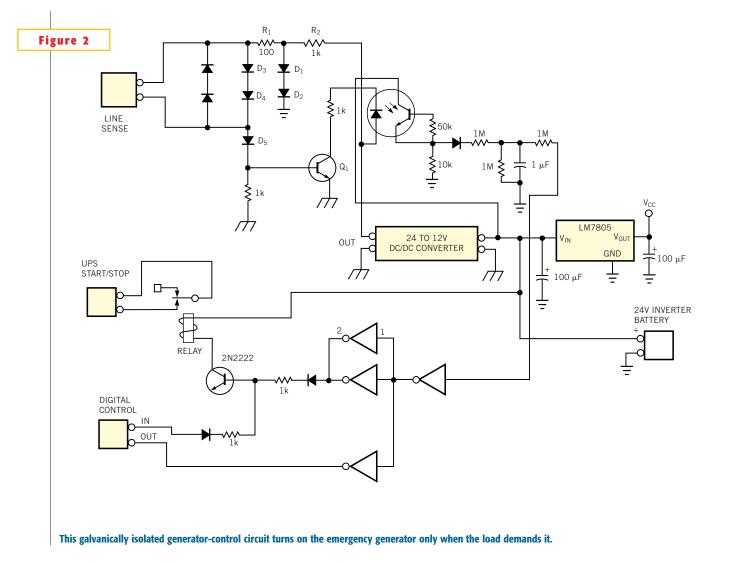

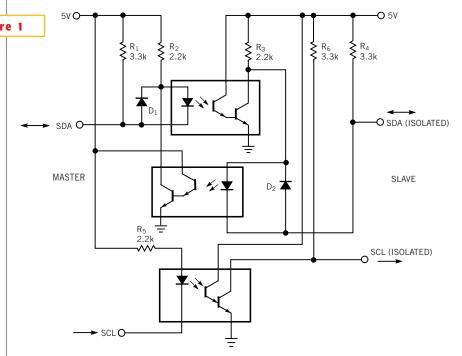

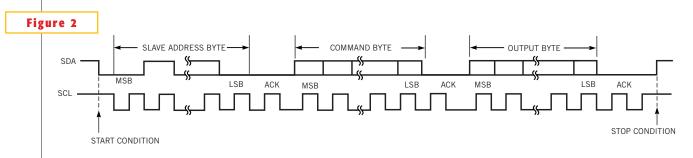

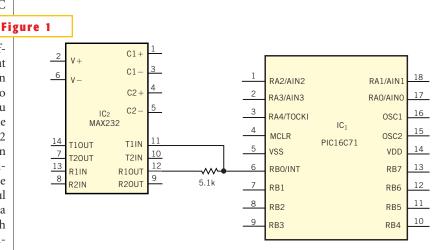

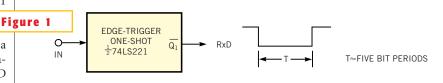

#### **RS-232C** circuit has galvanic isolation

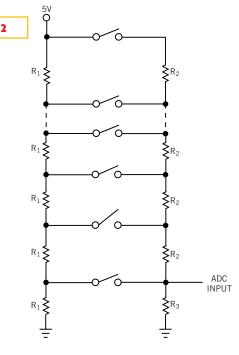

Ioan Ciascai, REI Data, Napoca, Romania

Y OU CAN OBTAIN LONGER TRANSMIS-SION distances with the RS-232C interface if you use galvanic isolation between the two linked terminals. Galvanic isolation also eliminates problems arising from disparate potentials between terminals. Using two MAX860/861 ICs and two TPL2200 optoisolators, you can obtain galvanic isolation for three-wire transmission without external supplies (**Figure 1**). The MAX860/861 circuits, which generate two voltages of different polarity, regardless of the polarity of TxD, which provides the supply voltage, are the basis of the design. For the positive TxD polarity, the MAX860/861 ICs function as voltage inverters, whereas for negative-polarity TxD, the ICs function as voltage doublers. Diodes  $D_1$  and  $D_7$  provide the positive supply voltages;  $D_4$  and  $D_9$  provide the negative supply voltages, depending on the polarity of TxD. The diode-resistor pairs  $D_5$ ,  $R_1$  and  $D_{10}$ ,  $R_2$  determine the operating mode (doubler or inverter) of the MAX860/861 ICs, depending on the polarity of TxD. Zener diodes  $D_2$ ,  $D_3$ ,  $D_6$ , and  $D_8$  protect the MAX860/861 ICs from supply overvoltages.

The digital-output TLP2200 optoiso-

lators provide galvanic isolation and generate the RxD received signals with RS-232C logic levels. The circuit provides galvanically isolated communication in full-duplex mode at any standard transmission speed. The use of galvanic isolation allows transmission over nearly twice the distance for nonisolated systems. If you use a four-wire cable and split the separation circuits at the cable ends, you can further increase the transmission distance. (DI #2315).

> To Vote For This Design, Circle No. 333

RS-232C-interface ICs and optoisolators provide a supplyless RS-232C transmission link with galvanic isolation for increased distance.

**102** EDN | FEBRUARY 4, 1999

## design**ideas**

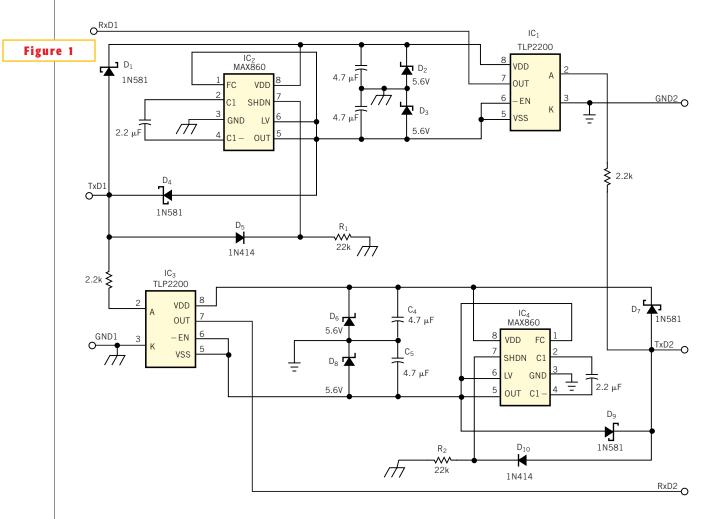

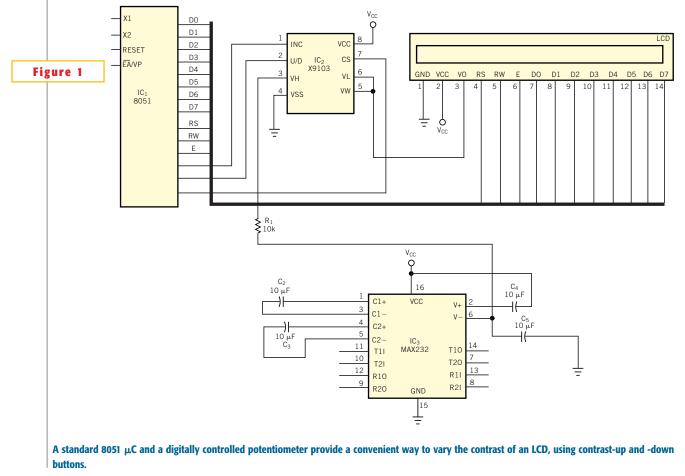

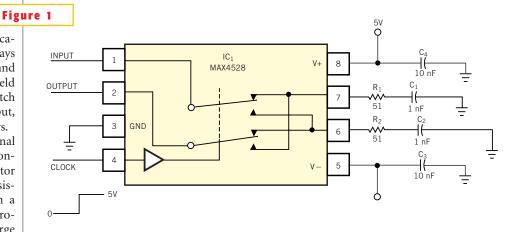

## **Digital pot adjusts LCD's contrast**

Jef Collin, CSE Systems, Turnhout, Belgium

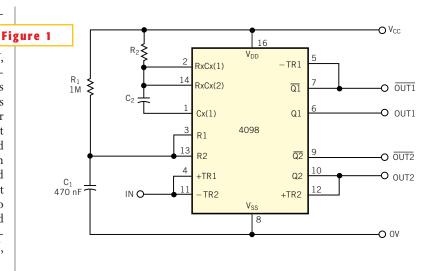

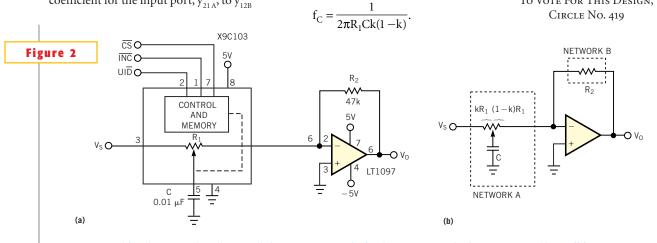

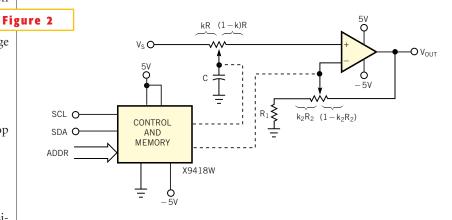

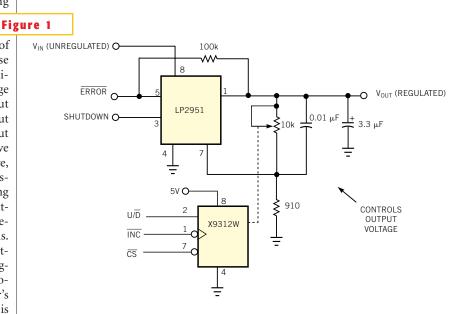

OU CAN USE A DIGITALLY controlled potentiometer for many purposes. In this example, you can use the device to regulate the contrast of a standard (such as two lines by 40 characters) LCD. You can use the circuit in Figure 1 in a portable test system, in which you need to change the contrast of the LCD as a function of the viewing angle. You choose the contrast setup from a menu and then use up or down buttons with  $\mu C IC_1$  to adjust the contrast. The µC stores the contrast value in the digital potentiometer, IC<sub>2</sub>. This design uses a Xicor 10-k $\Omega$ unit (dubbed "EEPOT"), but you could use other devices in the design.

The EEPOT connects to the LCD's VO line. You could connect the other side of the potentiometer to ground, but, for better contrast, you can apply a negative voltage to this terminal. This circuit has a

serial interface, so it uses the negativevoltage generator in the MAX232 RS-232C/TTL converter. **Listing 1** is the subroutine for the 8051  $\mu$ C. The program calls the routines for contrast-up or -down. (DI #2314).

To Vote For This Design, Circle No. 334

## Add speech encoding/decoding to your design

/\* Table of index changes \*/

int step;

1

step >>= 1;

{

}

}

if( diff >= step )

Rodger Richey, Microchip Technology Inc, Chandler, AZ

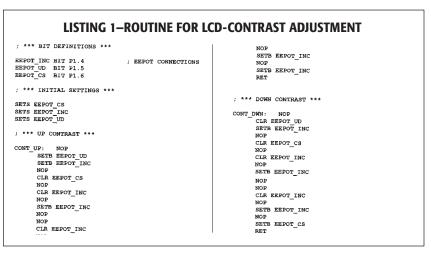

DDING SPEECH capabilities to a design can sometimes lead to complex algorithms and expensive DSPs or specialized audio chips. However, with the completion of a simplified adaptive differential pulse-codemodulation (ADPCM) algorithm, you can now implement these audio capabilities in low-cost 8-bit µCs, which typically have lower power consumption and cost than their DSP or audio-chip counterparts. A two-chip design is feasible by offloading the encoding and decoding tasks onto the  $\mu$ C as if it were a peripheral.

Since 1991, the Interactive Multimedia Association (IMA) Digital Audio Technical Working Group (DATWG) has been working to define a cross-platform digital-audio exchange format. An inherent problem exists with the exchange of audio data between PC, Mac, and workstation computers. Each computer has its own data types and sampling rates. In May 1992, IMA DATWG published the first revision of the Cross-Platform Digital Audio Interchange recommendation that specifies three uncompressed and one compressed data type at various sample rates. The compressed data type is the Intel (www. intel.com) 4-bit DVI ADPCM algorithm. This algorithm compresses a 16-bit signed audio sample into 4 bits and takes advantage of the high correla-

tion between consecutive samples, which enables the prediction of future samples. Instead of encoding the sample itself, ADPCM encodes the difference between a predicted sample and the actual sample. This method provides more efficient

#### /\* Quantizer step size lookup table \* const long StepSizeTable(89] = {7,8,9,10,11,12,13,14,16,17,19,21,23,25,28,31,34,37,41, 45,50,55,60,66,73,80,88,97,107,118,130,143,157,173,190, 209,230,253,279,307,337,371,408,449,494,544,598,658,724 796,876,963,1060,1166,1282,1411,1552,1707,1878,2066,2272, 2499, 2749, 3024, 3327, 3660, 4026, 4428, 4871, 5358, 5894, 6484, 7132, 7845, 8630, 9493, 10442, 11487, 12635, 13899, 15289, 16818, 18500,20350,22385,24623,27086,29794,32767}; signed int diff; // Diff. between sample and predicted sample // Quantizer step size // ADPCM predictor output, Predicted diff. signed int predsample, diffq; char index; // Index into step size table char ADPCMEncoder( signed int sample ) char code: // ADPCM output value predsample = state.prevsample; // Restore previous values of predicted index = state.previndex; step = StepSizeTable[index]; // sample and quantizer step size index diff = sample - predsample; // Compute diff. between actual sample $if(diff \ge 0)$ // and the predicted sample code = 0;else code = 8; diff = -diff; diffq = step >> 3; // Ouantize the diff. into 4-bit ADPCM code if( diff >= step ) // using the quantizer step size code |= 4; diff -= step; // Inverse quantize the ADPCM code into a // predicted diff. using the quantizer step diffq += step; // size step >>= 1; if( diff >= step ) code |= 2; diff -= step; diffq += step;

LISTING 1-ADPCM ENCODER

const char IndexTable[16] = {-1,-1,-1,-1,2,4,6,8,-1,-1,-1,-1,2,4,6,8};

code |= 1; diffq += step; if( code & 8 ) // Compute new predicted sample by adding predsample -= diffq; // the old predicted sample to new diff. else predsample += diffq; // Check if overflow of the new pred. sample index += IndexTable[code]; // Find new quantizer stepsize if( index < 0 )  $\,$ // Check if overflow of new quantizer step index = 0;if( index > 88 ) index = 88; state.prevsample = predsample; // Save values for next iteration state.previndex = index; return ( code & 0x0f ); // Return the ADPCM code

compression with fewer bits per sample and yet preserves the overall quality of the audio signal. Both the encoder routine (Listing 1) and the decoder routine (Listing 2) are written in C to ease readability.

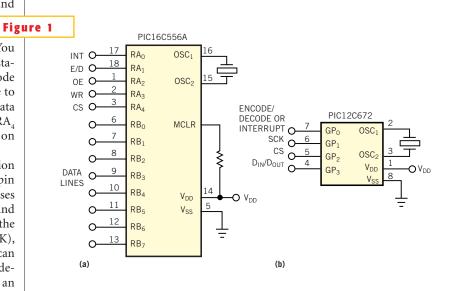

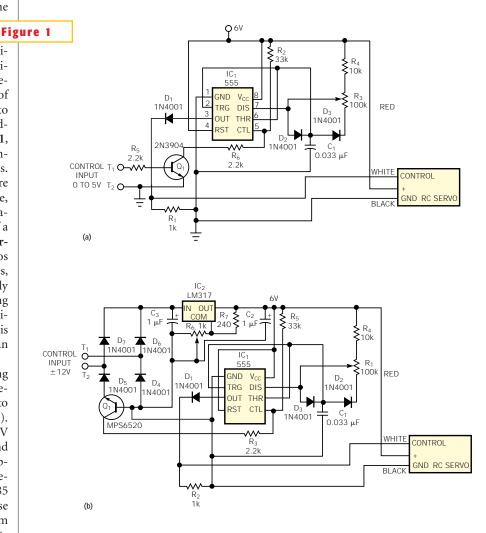

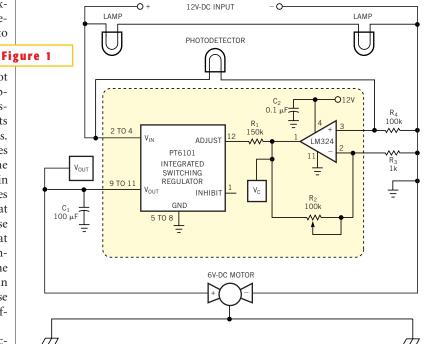

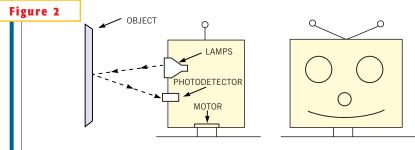

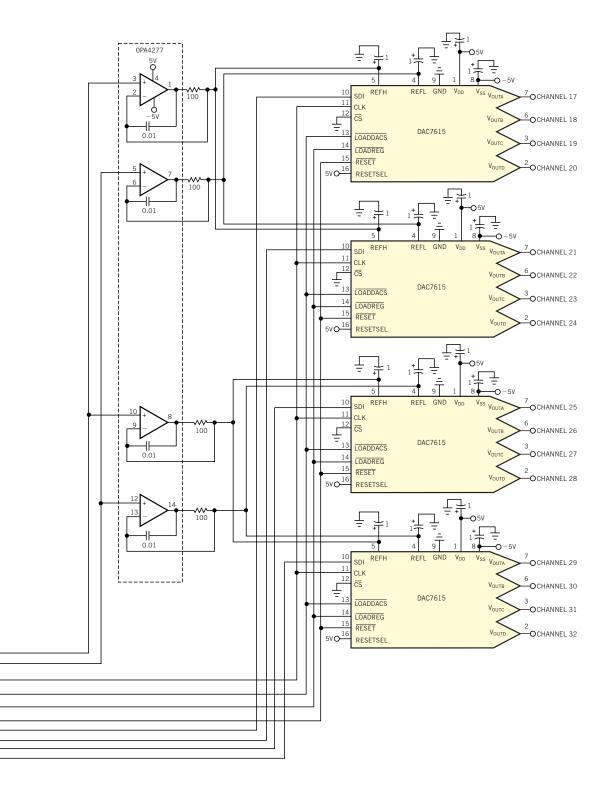

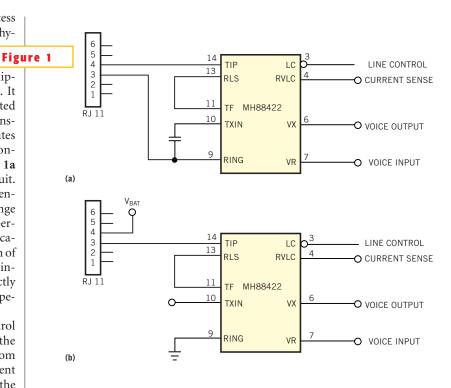

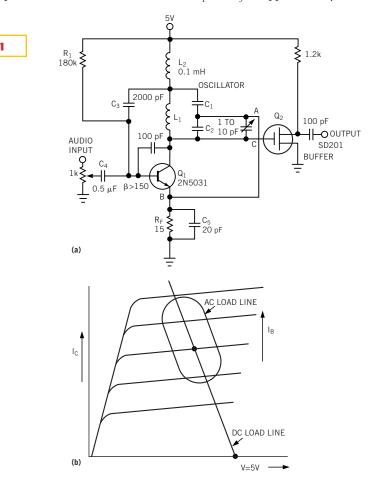

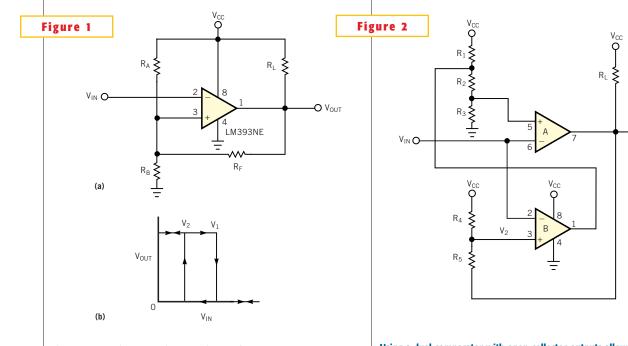

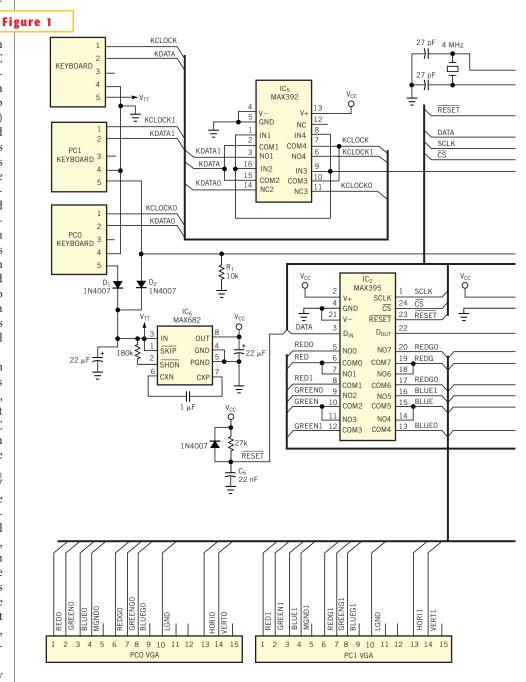

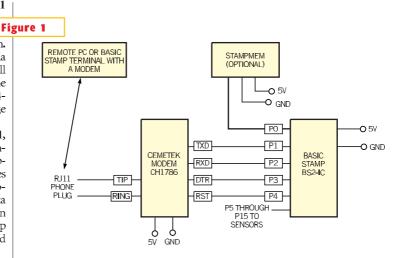

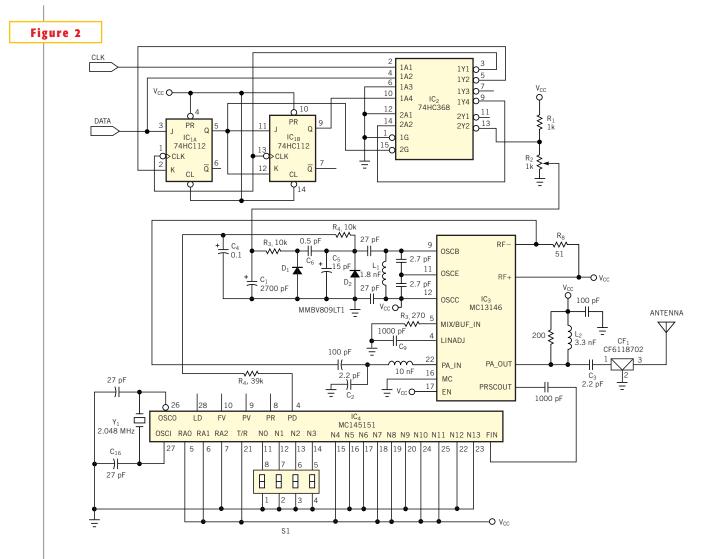

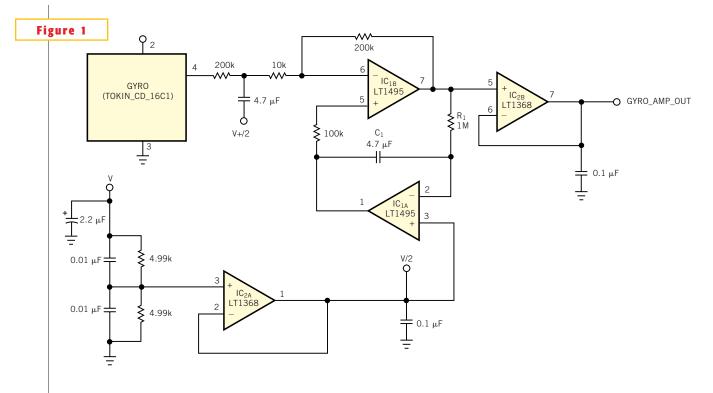

The hardware implementation depends on the type of interface. With a parallel interface, you can use the PIC16C556A (Microchip Technology, www.microchip.com) (Figure 1a). A standard parallel interface uses the chip-

select (CS), output-enable (OE), and write-enable (WR) pins on Port A. The 8-bit data interface connects to the 8-bit Port B on the  $\mu$ C. You can use two additional I/O lines for status information, such as encode/decode select, to the  $\mu$ C or an interrupt line to the main controller to indicate when data is ready. CS, which connects to the RA<sub>4</sub> pin, can interrupt the PIC16C556A on the start of a transmission.

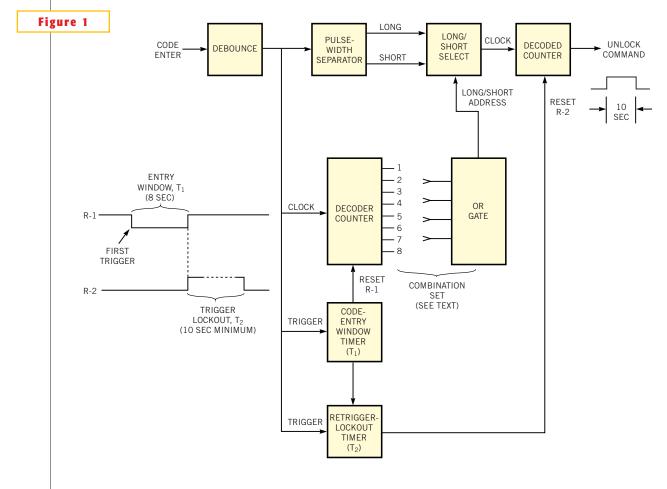

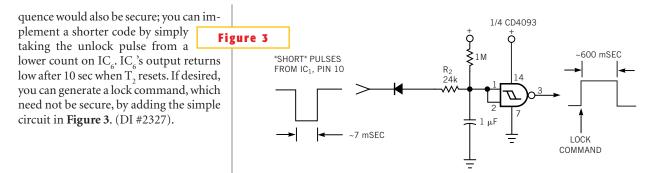

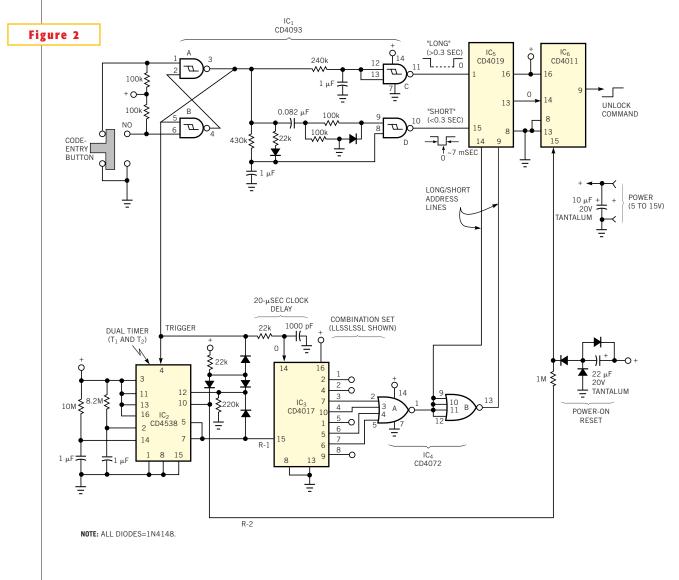

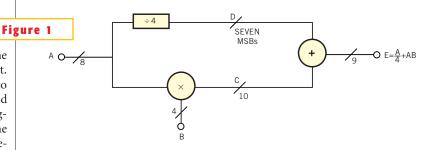

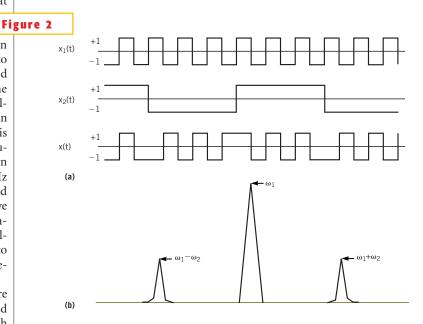

The second hardware implementation uses a serial interface and an eight-pin  $\mu$ C (**Figure 1b**). The PIC12C672 uses four of the pins for power, ground, and oscillator input and output. Three of the remaining I/O pins are for clock (SCK), data in/out (D<sub>IN</sub>/D<sub>OUT</sub>), and CS. You can use the other I/O pin to indicate the desired encode/decode operation or as an interrupt to the main controller. CS connects to the external interrupt pin, GP<sub>2</sub>, to detect the start of a transmission.