#### ELTR 140 (Digital 1), section 1

#### **Recommended schedule**

## $\underline{\text{Day } 1}$

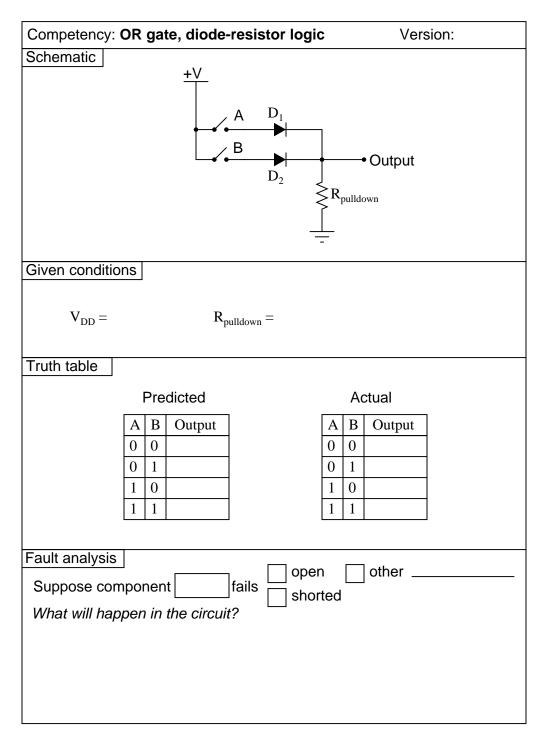

Topics: Logic states and simple gate circuits Questions: 1 through 10 Lab Exercise: OR gate, diode-resistor logic (question 51)

## Day 2

Topics: *TTL logic gates and truth tables* Questions: 11 through 20 Lab Exercise: AND gate, simple BJT logic (question 52)

## <u>Day 3</u>

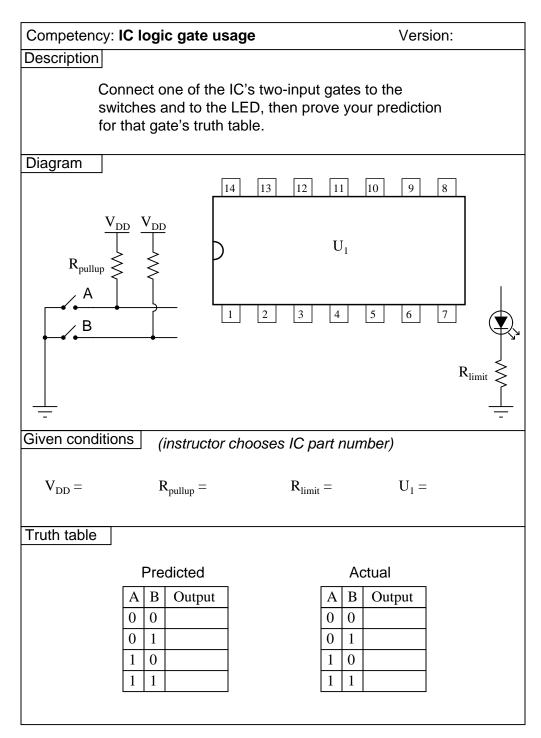

Topics: CMOS logic gates and truth tables Questions: 21 through 30 Lab Exercise: IC logic gate usage (question 53)

#### Day 4

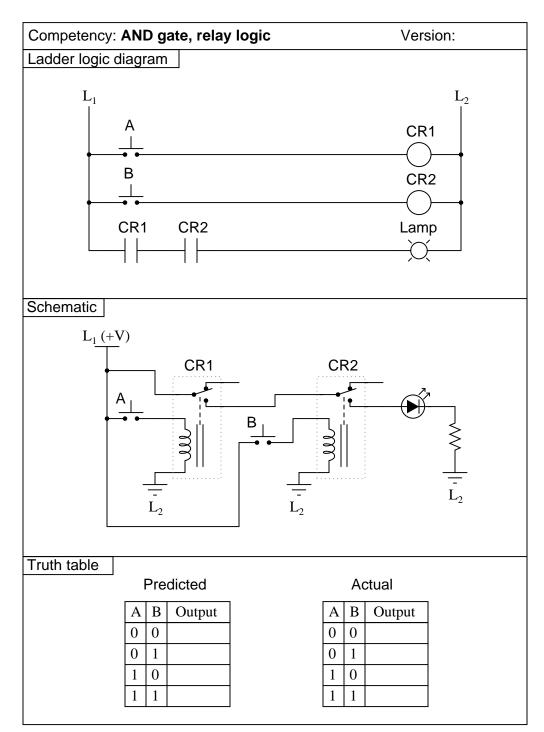

Topics: Relay circuits and truth tables Questions: 31 through 40 Lab Exercise: AND gate, relay logic (question 54)

## $\underline{\text{Day } 5}$

Topics: Logic circuit performance parameters Questions: 41 through 50 Lab Exercise: Gate-relay interposing (question 55)

#### Day 6

Exam 1: includes IC logic gate performance assessment

Troubleshooting practice problems Questions: 57 through 66

DC/AC review problems Questions: 67 through 86

Basic principles of microcontrollers Questions: 87 through 96

<u>General concept practice and challenge problems</u> Questions: 97 through the end of the worksheet

## Impending deadlines

Project due at end of ELTR140, Section 3

Question 56: Sample project grading criteria

#### **Project** ideas

<u>Logic probe</u>: Uses a comparator and at least one logic gate to drive three LEDs: "High", "Low", and "Indeterminate", showing three different voltage levels detected at the probe. The thresholds for high and low logic levels shall be adjustable for use in different types of logic circuits.

<u>Digital combination lock</u>: Drives a solenoid or other power device only when the input code matches the "key" code (set by a series of switches on the circuit board), and drives an alarm siren if the input code does *not* match the "key" code. The logic function may be done with Exclusive-OR gates or with a magnitude comparator IC. Remember, the more bits in the codes, the harder it is to guess!

#### Skill standards addressed by this course section

EIA Raising the Standard; Electronics Technician Skills for Today and Tomorrow, June 1994

#### F Technical Skills – Digital Circuits

- F.01 Demonstrate an understanding of the characteristics of integrated circuit (IC) logic families.

- F.05 Understand principles and operations of types of logic gates.

- **F.06** Fabricate and demonstrate types of logic gates.

- F.07 Troubleshoot and repair types of logic gates.

#### **B** Basic and Practical Skills – Communicating on the Job

- B.01 Use effective written and other communication skills. Met by group discussion and completion of laborek.

- **B.03** Employ appropriate skills for gathering and retaining information. Met by research and preparation prior to group discussion.

- **B.04** Interpret written, graphic, and oral instructions. Met by completion of laborate.

- B.06 Use language appropriate to the situation. Met by group discussion and in explaining completed labwork.

- B.07 Participate in meetings in a positive and constructive manner. Met by group discussion.

- **B.08** Use job-related terminology. Met by group discussion and in explaining completed labork.

- **B.10** Document work projects, procedures, tests, and equipment failures. *Met by project construction and/or troubleshooting assessments.*

- C Basic and Practical Skills Solving Problems and Critical Thinking

- C.01 Identify the problem. Met by research and preparation prior to group discussion.

- C.03 Identify available solutions and their impact including evaluating credibility of information, and locating information. *Met by research and preparation prior to group discussion.*

- C.07 Organize personal workloads. Met by daily labwork, preparatory research, and project management.

- C.08 Participate in brainstorming sessions to generate new ideas and solve problems. Met by group discussion.

D Basic and Practical Skills Reading

- **D.01** Read and apply various sources of technical information (e.g. manufacturer literature, codes, and regulations). *Met by research and preparation prior to group discussion.*

#### E Basic and Practical Skills – Proficiency in Mathematics

- **E.01** Determine if a solution is reasonable.

- **E.02** Demonstrate ability to use a simple electronic calculator.

- E.06 Translate written and/or verbal statements into mathematical expressions.

- E.07 Compare, compute, and solve problems involving binary, octal, decimal, and hexadecimal numbering systems.

- E.12 Interpret and use tables, charts, maps, and/or graphs.

- E.13 Identify patterns, note trends, and/or draw conclusions from tables, charts, maps, and/or graphs.

- E.15 Simplify and solve algebraic expressions and formulas.

- E.16 Select and use formulas appropriately.

- E.18 Use properties of exponents and logarithms.

## **F** Additional Skills – Electromechanics

**B.01b** Relays and relay circuits.

#### Common areas of confusion for students

#### **Difficult concept:** Necessary conditions for transistor operation.

It is vitally important for students to understand the conditions necessary for transistor operation, both for understanding how circuits work and for troubleshooting faulty circuits. Bipolar junction transistors require a base current (in the proper direction) to conduct, and the collector-to-emitter voltage must be of the correct polarity to push a collector current in the proper direction as well. Both currents join at the emitter terminal, making the emitter current the sum of the base and collector currents. Field-effect transistors are not so picky about the direction of the controlled current, and they only require the correct gate voltage (no gate current) to establish conduction. What makes this so confusing is that there are two types of bipolar transistors (NPN and PNP), two types of junction field-effect transistors (N-channel and Pchannel), and four types of MOSFETs (E-type N-channel, E-type P-channel, D-type N-channel, and D-type P-channel).

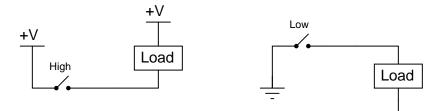

#### **Difficult concept:** Current sourcing versus current sinking.

It is very common in electronics work to refer to current-controlling devices as either *sourcing* current to a load or *sinking* current from a load. This is an overt reference to conventional-flow notation, referring to whether the conventional flow moves *out* of the transistor from the positive power supply terminal to the load (sourcing), or whether the conventional flow moves *in* to the transistor from the load and then "down" to ground (sinking). Some students grasp this concept readily, while others seem to struggle mightily with it. It is something rather essential to understand, because this terminology is extensively used by electronics professionals and found in electronics literature. The key detail distinguishing the two conditions is which power supply rail (either +V or Gnd) is *directly* connected to the current-controlling device.

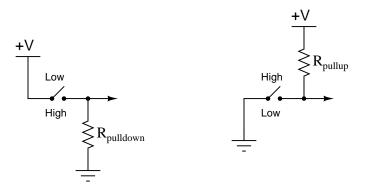

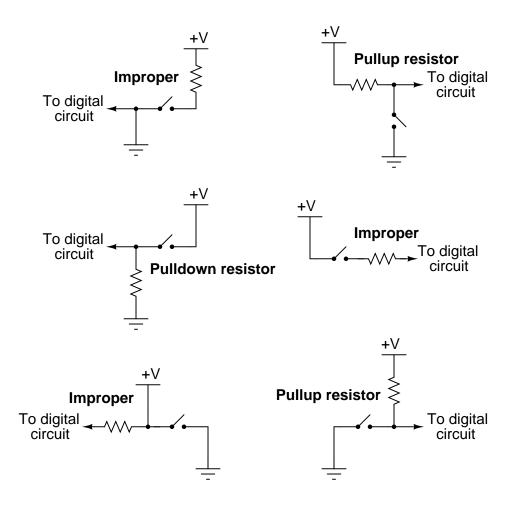

#### **Difficult concept:** Pullup and pulldown resistor placement.

In digital circuits, resistors are often used to provide a secure logic state when an input device (such as a switch) goes to a high-impedance (open) mode. Students often have difficulty figuring out exactly where these resistors should go in a circuit. The most common mistake I've seen is to place one of these "pullup" or "pulldown" resistors in *series* with a gate input, which will accomplish absolutely nothing. The "trick" to getting this placement right, if you can call it a trick at all, is to literally follow the word "pullup" or "pulldown." A *pullup* resistor pulls the logic state of a wire up to the positive supply rail, and so must connect between the gate input and +V. A *pulldown* resistor pulls the logic state of a wire down to ground potential, and so must connect between the gate input and ground. In either case, the resistor provides a sure path to the opposite power rail that the input device connects to when active (closed).

A rheostat (variable resistor) and a switch are both examples of electric components exhibiting different degrees of conductivity:

Which of these devices would be considered *discrete* and which would be considered *continuous* in terms of their electrical conductivity? What do each of these words mean, and how might they apply to variables in electric circuits other than conductivity?

## $\underline{\text{file } 02753}$

## Question 2

Digital logic circuitry makes use of discrete voltage levels: each "logic gate" sub-circuit inputs and outputs voltages that are either considered "high" or "low". Define what both of these terms means in a digital logic circuit powered by 5 volts DC.

$\underline{\text{file } 02755}$

### Question 3

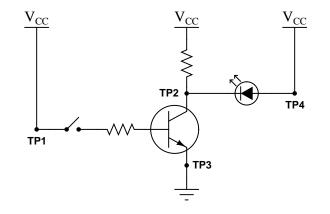

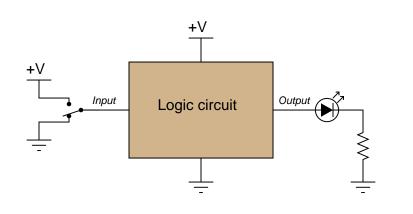

Determine the logic levels (either "high" or "low") at each of the test points in this circuit with the toggle switch in the open position, as well as the status of the transistor and LED:

- $V_{TP1} = (high \text{ or } low?)$

- $V_{TP2} = (high \text{ or } low?)$

- $V_{TP3} = (high \text{ or } low?)$

- $V_{TP4} = (high \text{ or } low?)$

- Transistor = (on or off?)

- LED = (on or off?)

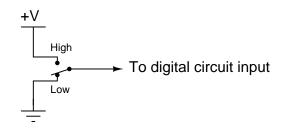

If we need to produce a discrete logic signal ("high" or "low") from a mechanical switch, the most direct way of doing so is to use a single-pole, double-throw switch (SPDT) like this:

In the "High" position, the switch directly connects the signal line to +V, ensuring a high logic state; in the "Low" position, the switch directly connects the signal line to ground, ensuring a low logic state. What could be simpler?

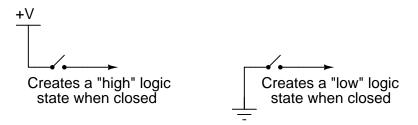

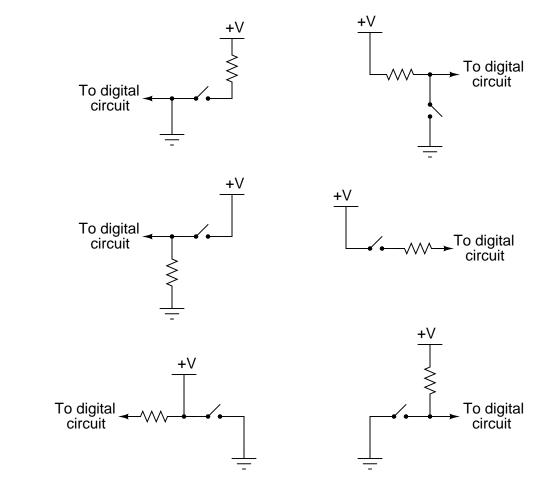

However, often a SPDT switch is not feasible and we must use a SPST (single-pole, single-throw) switch instead:

A problem often arises with such configurations because in the open position there is neither a connection to +V nor ground. In other words, these two SPST configurations produce the exact same indeterminate logic state ("floating") when their respective switches are open. To remedy this, resistors are often added to such circuits:

Explain what functions the *pulldown* and *pullup* resistors serve, and also why they are referred to by those names.

<u>file 03001</u>

A common mistake made by students new to digital circuits is to misplace the pullup or pulldown resistors in schematic diagrams, and also in the circuits they build. Study the following schematics and determine whether the resistor in each one is a properly-placed *pullup* or *pulldown* resistor, or if it is improperly placed:

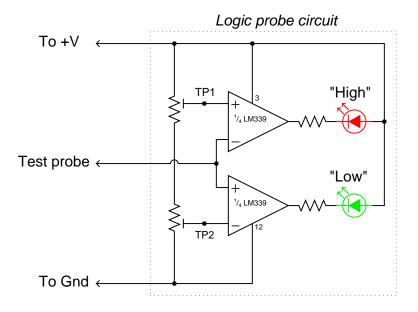

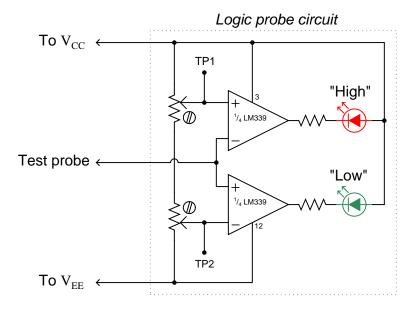

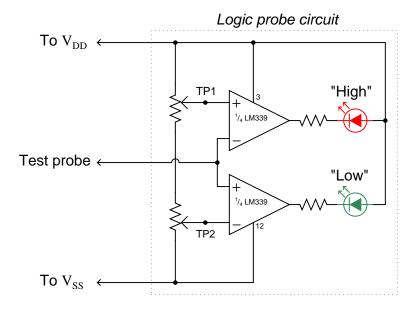

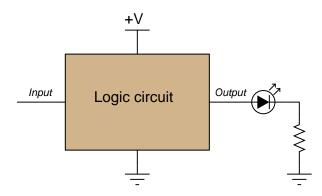

A *logic probe* is a very useful tool for working with digital logic circuits. It indicates "high" and "low" logic states by means of LED's, giving visual indication only if the voltage levels are appropriate for each state.

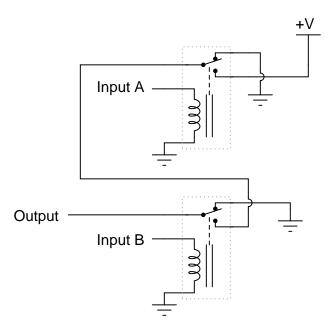

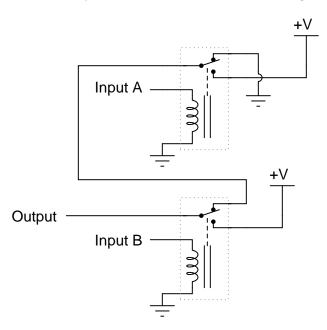

Here is a schematic diagram for a logic probe built using comparators. Each comparator has a threshold adjustment potentiometer, so that it may be set to indicate its respective logic state only if the signal voltage is well within the range stated by the logic manufacturer:

Explain how this circuit functions. file 02758

## Question 7

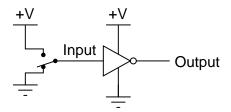

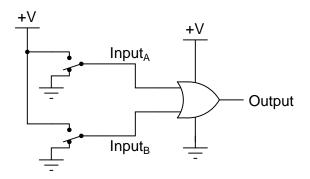

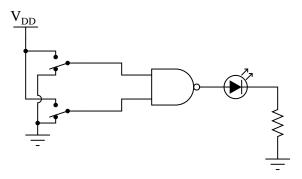

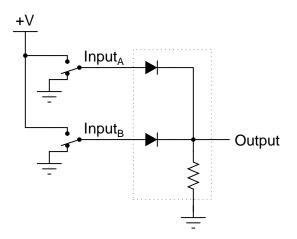

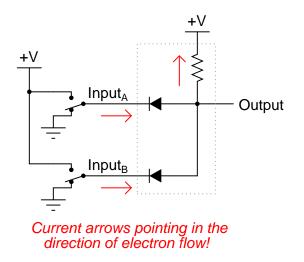

Identify the type of logic gate shown in this schematic diagram, and explain why it has the name it does:

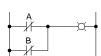

Identify the type of logic gate shown in this schematic diagram, and explain why it has the name it does:

<u>file 02760</u>

## Question 9

Identify the type of logic gate shown in this schematic diagram, and explain why it has the name it does:

# $\underline{\mathrm{file}\ 02759}$

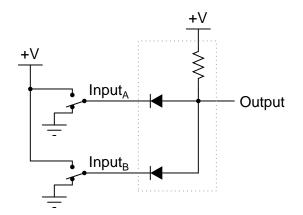

Crude logic gates circuits may be constructed out of nothing but diodes and resistors. Take for example this logic gate circuit:

Identify what type of logic function is represented by this gate circuit (AND, OR, inverter, etc.). Also, trace the directions of all currents in this circuit.

<u>file 02762</u>

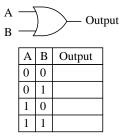

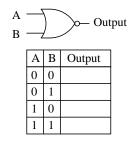

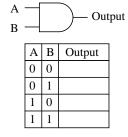

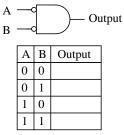

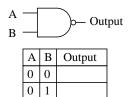

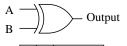

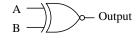

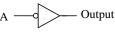

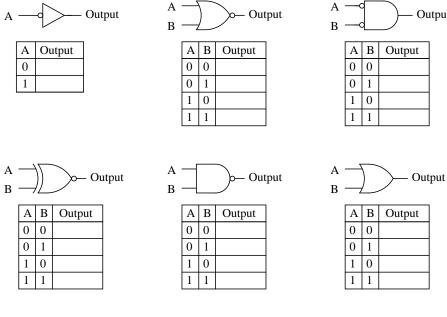

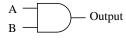

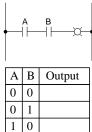

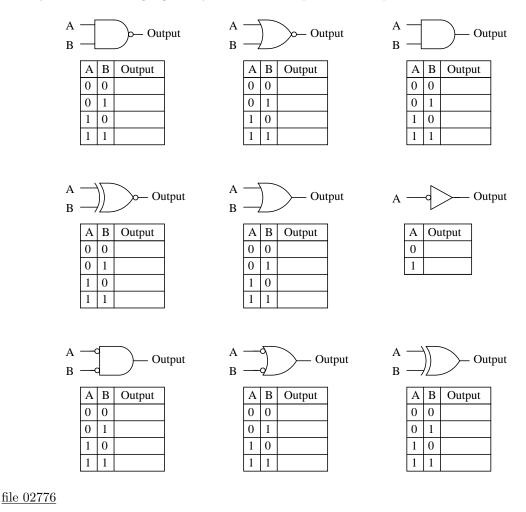

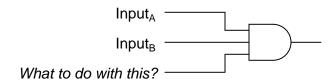

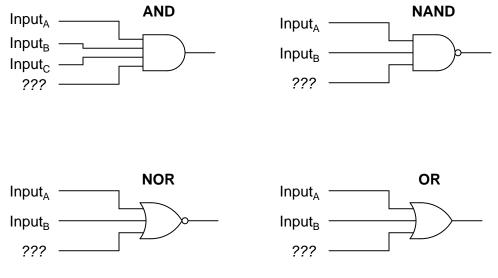

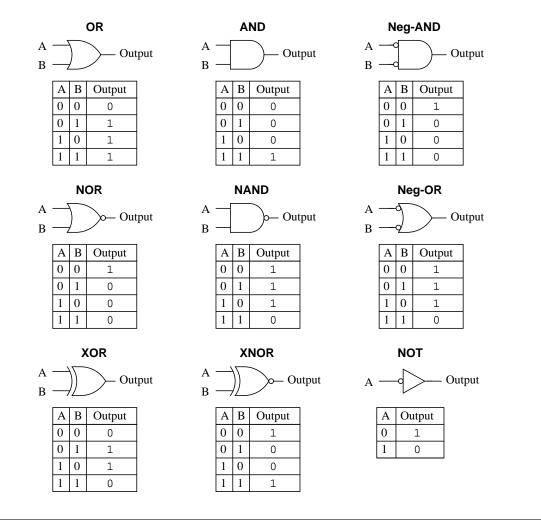

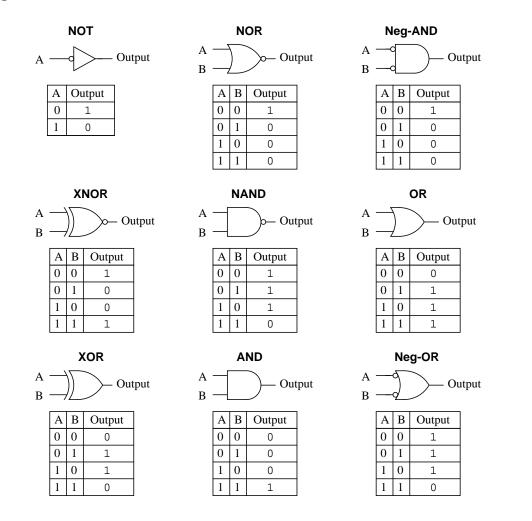

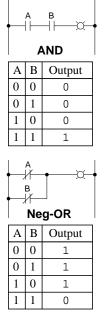

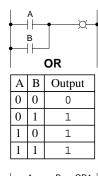

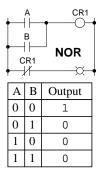

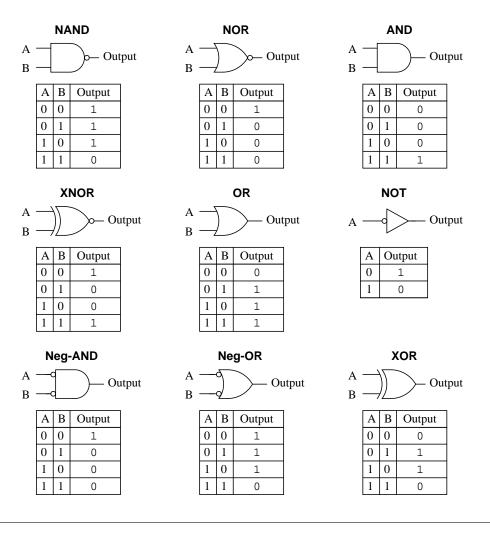

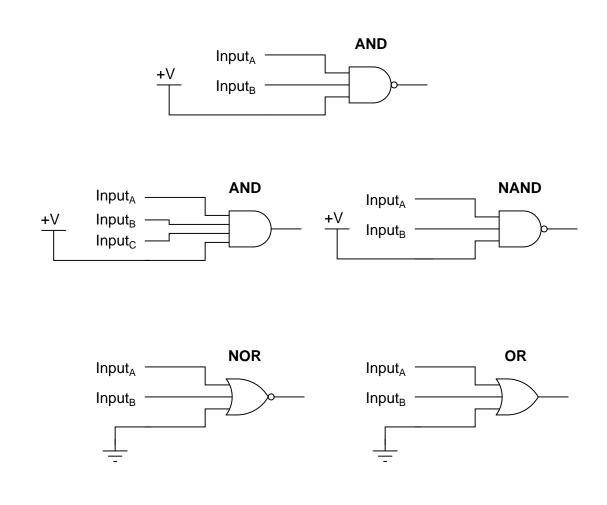

Identify each of these logic gates by name, and complete their respective truth tables:

1 0

1 1

1 1

| А | В | Output |

|---|---|--------|

| 0 | 0 |        |

| 0 | 1 |        |

| 1 | 0 |        |

| 1 | 1 |        |

| А | В | Output |

|---|---|--------|

| 0 | 0 |        |

| 0 | 1 |        |

| 1 | 0 |        |

| 1 | 1 |        |

| A | Output |

|---|--------|

| 0 |        |

| 1 |        |

| _ |        |

<u>file 01249</u>

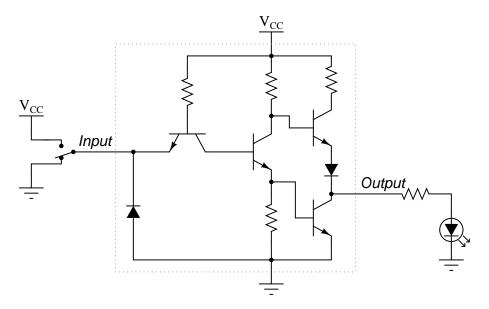

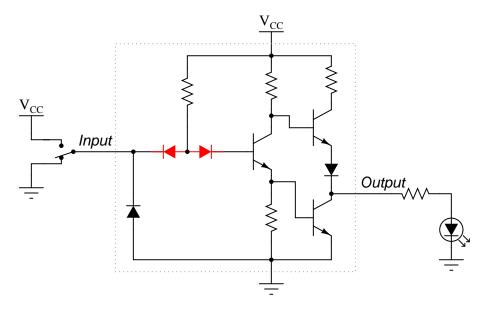

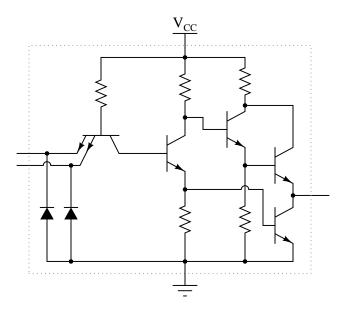

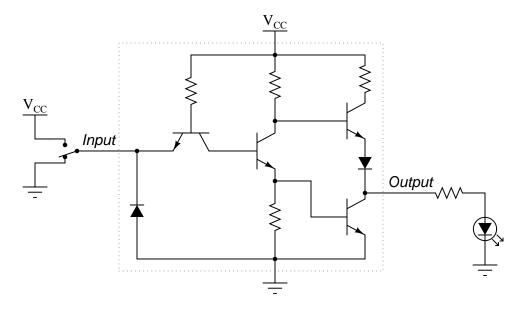

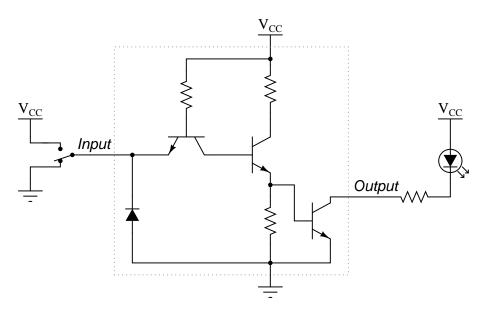

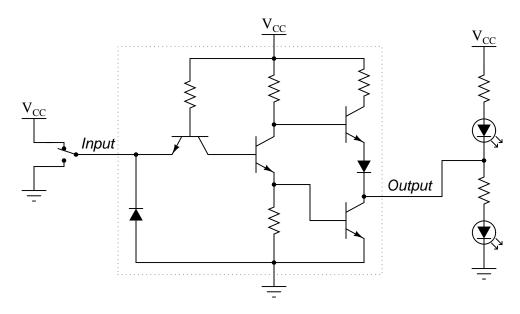

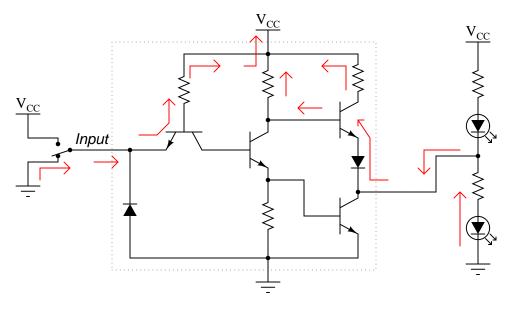

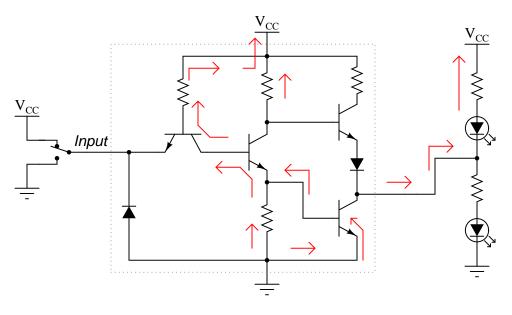

The simplest type of digital logic circuit is an *inverter*, also called an *inverting buffer*, or *NOT gate*. Here is a schematic diagram for an inverter gate constructed from bipolar transistors (transistor-to-transistor-logic, also known as *TTL*), shown connected to a SPDT switch and an LED:

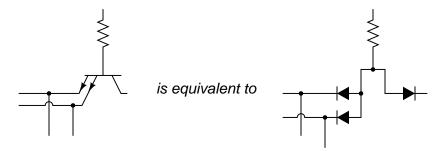

The left-most transistor in this schematic is actually not being used as a transistor, but rather it functions as a "steering diode" network, like this:

Determine the status of the LED in each of the input switch's two positions. Denote the logic level of switch and LED in the form of a truth table:

| Input | Output |

|-------|--------|

|       |        |

|       |        |

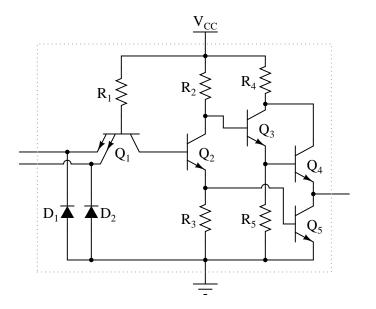

The following is an internal schematic of a TTL logic gate. Based on your analysis of the transistor circuit, determine what type of gate (AND, OR, NAND, NOR, XOR, etc.) it is:

Hint: the double-emitter transistor is being used as a pair of diodes, and not as an amplifying device!

<u>file 01250</u>

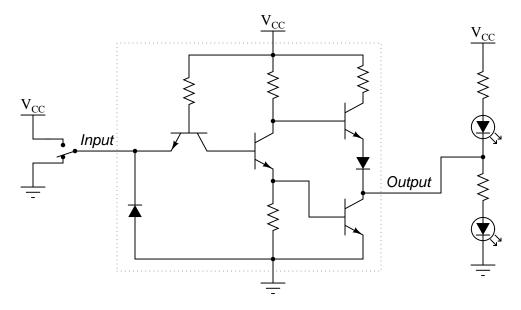

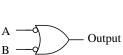

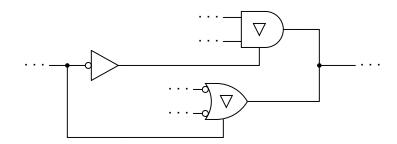

A very important concept to understand in digital circuitry is the difference between *current sourcing* and *current sinking*. For instance, examine this TTL inverter gate circuit, connected to a load:

The output circuitry of this particular gate is commonly referred to as "totem-pole," because the two output transistors are stacked one above the other like figures on a totem pole. Is a gate circuit with a totem-pole output stage able to *source* load current, *sink* load current, or do both?

$\underline{\text{file } 01666}$

A very important concept to understand in digital circuitry is the difference between *current sourcing* and *current sinking*. For instance, examine this open-collector TTL inverter gate circuit, connected to a load:

Open-collector gates are specially designated in their schematic symbols by a marker within the gate shape:

Is this gate circuit able to *source* load current, sink load current, or do both? <u>file 01258</u>

#### Question 16

Based on an analysis of a typical TTL logic gate circuit (consult a datasheet for a TTL logic gate if you need an internal schematic diagram for a gate circuit), determine what logic state is "assumed" by a TTL gate input when left "floating" (disconnected).

What ramification does this have for us when choosing input devices for TTL logic gates? If, for instance, we wished to use a single-pole, single-throw (SPST) switch as the input device for a TTL logic gate, what is the *best* way to connect such a device to a TTL input? Should the switch connect the TTL input to  $V_{CC}$  when closed, or should it connect the input to  $V_{EE}$  when closed? Why does it matter? Explain your answer in detail.

A *logic probe* is a very useful tool for working with digital logic circuits. It indicates "high" and "low" logic states by means of LED's, giving visual indication only if the voltage levels are appropriate for each state.

Here is a schematic diagram for a logic probe built using comparators. Each comparator has a threshold adjustment potentiometer, so that it may be set to indicate its respective logic state only if the signal voltage is well within the range stated by the logic manufacturer:

When this logic probe circuit is connected to the  $V_{CC}$  and  $V_{EE}$  power supply terminals of a powered TTL circuit, what voltage levels should test points TP1 and TP2 be adjusted to, in order for the probe to properly indicate "high" and "low" TTL logic states? Consult a datasheet for the quad NAND gate numbered either 74LS00 or 54LS00. Both are legacy TTL integrated circuits.

<u>file 01262</u>

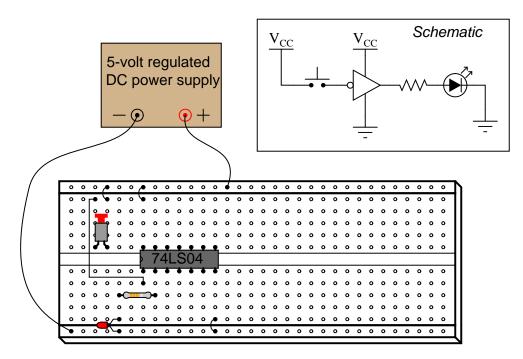

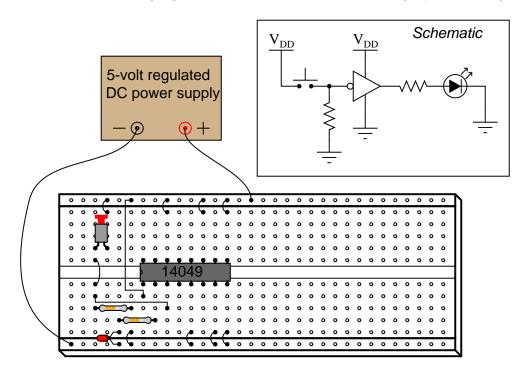

A student builds the following digital circuit on a solderless breadboard (a "proto-board"):

The DIP circuit is a TTL hex inverter (it contains *six* "inverter" or "NOT" logic gates), but only one of these gates is being used in this circuit. The student's intent was to build a logic circuit that energized the LED when the pushbutton switch was unactuated, and de-energized the LED when the switch was pressed: so that the LED indicated the reverse state of the switch itself. However, in reality the LED fails to energize no matter what state the switch is in.

First question: how would you use a multimeter as a logic probe to check the logic states of points in this circuit, in order to troubleshoot it?

Second question: suppose you checked the logic states of pin #1 on the IC, for both states of the switch (pressed and unpressed), and found that pin #1 was always "high". How does this measurement indicate the student's design flaw in this circuit? How would you recommend this design flaw be corrected? file 01252

Draw the paths of all currents in this circuit with the input in a "low" state:

Now, draw the paths of all currents in this circuit with the input in a "high" state:

Where is the power supplied for each LED? What relationship is there between the load current (LED) and the gate input current (through the SPDT switch)?

Also, explain how you would calculate the values for appropriate LED current-limiting resistors in this circuit.

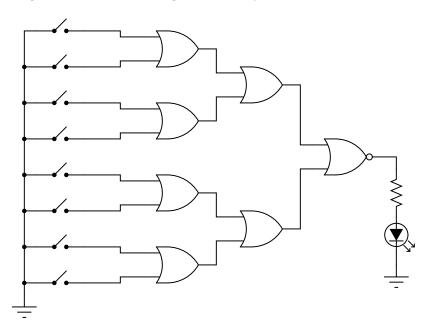

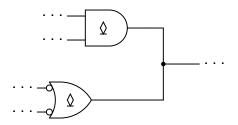

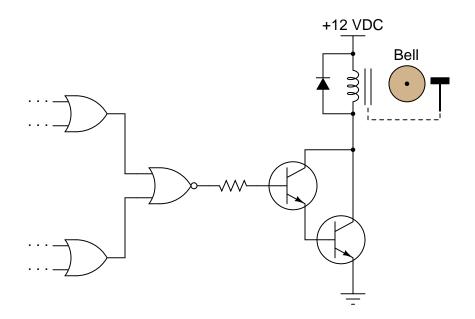

The digital circuit shown here is a unanimous-yea vote detector. Votes are cast by eight different voters by the setting of switches in either the closed (yea) or open (nay) positions. According to the logic function provided by the TTL gates, the LED will energize if and only if all switches are closed:

As is common in digital circuit schematics, the power supply  $(V_{CC})$  is omitted for the sake of simplicity. This is analogous to the omission of power supply connections in many operational amplifier circuit schematics.

If we were to draw a truth table for this circuit, how large (number of rows and columns) would the table have to be?

Suppose we wished to modify this circuit, such that an electromechanical bell would ring whenever a unanimous-yea vote was cast, rather than merely lighting a small LED. The bell we have in mind to use is rather large, its solenoid coil drawing 3 amps of current at a voltage of 12 volts DC: well beyond the final gate's ability to source. How could we modify this circuit so that the final gate is able to energize this bell instead of just an LED?

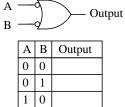

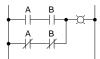

Identify each of these logic gates by name, and complete their respective truth tables:

| Α | В | Output |

|---|---|--------|

| 0 | 0 |        |

| 0 | 1 |        |

| 1 | 0 |        |

| 1 | 1 |        |

Output

| Α | В | Output |

|---|---|--------|

| 0 | 0 |        |

| 0 | 1 |        |

| 1 | 0 |        |

| 1 | 1 |        |

<u>file 02772</u>

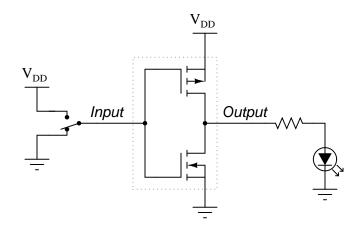

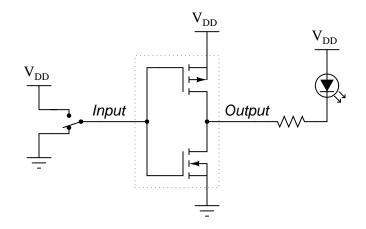

The simplest type of digital logic circuit is an *inverter*, also called an *inverting buffer*, or *NOT gate*. Here is a schematic diagram for an inverter gate constructed from complementary MOSFETs (CMOS), shown connected to a SPDT switch and an LED:

Determine the status of the LED in each of the input switch's two positions. Denote the logic level of switch and LED in the form of a truth table:

| Input | Output |

|-------|--------|

|       |        |

|       |        |

<u>file 01254</u>

## Question 23

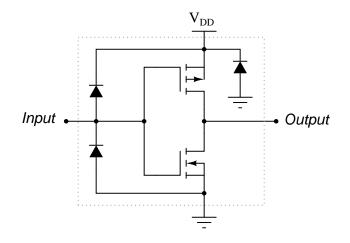

Practical CMOS logic gates contain more than just MOSFETs. Here is a schematic diagram for a typical inverter gate circuit, with protection diodes:

Explain what specific conditions each protection diode protects against.  $\underline{file~01255}$

A student builds the following digital circuit on a solderless breadboard (a "proto-board"):

The DIP circuit is a hex inverter (it contains *six* "inverter" or "NOT" logic gates), but only one of these gates is being used in this circuit. The student's intent was to build a logic circuit that energized the LED when the pushbutton switch was unactuated, and de-energized the LED when the switch was pressed: so that the LED indicates the reverse state of the switch itself. The student builds this circuit, and it is found to function perfectly well.

Explain the purpose of the resistor on the input of the inverter. What is it there for? What might happen if it were to be removed from the circuit?

Also, explain why the inputs of all the unused inverter gates in this IC have been either connected to ground or to  $V_{DD}$ . Is this necessary for the circuit to work properly, or is it just a precautionary measure? file 01253

# ${\it Question}~25$

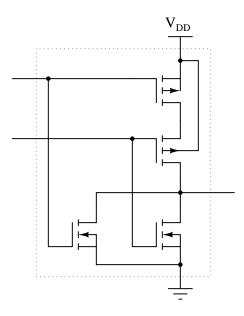

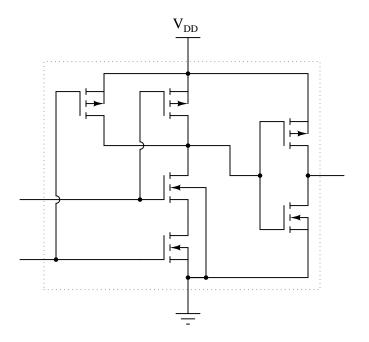

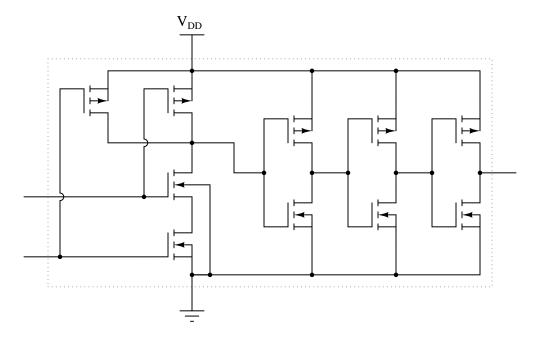

The following is an internal schematic of a CMOS logic gate. Based on your analysis of the transistor circuit, determine what type of gate (AND, OR, NAND, NOR, XOR, etc.) it is:

## file 01272

## Question 26

What is the typical power supply voltage range for a CD4xxx series (or MC4xxx series) CMOS logic gate? How does this compare with the allowable power supply voltage range for a standard (5 volt) TTL logic gate? Consult a datasheet for your answer.

<u>file 01274</u>

A *logic probe* is a very useful tool for working with digital logic circuits. It indicates "high" and "low" logic states by means of LED's, giving visual indication only if the voltage levels are appropriate for each state.

Here is a schematic diagram for a logic probe built using comparators. Each comparator has a threshold adjustment potentiometer, so that it may be set to indicate its respective logic state only if the signal voltage is well within the range stated by the logic manufacturer:

When this logic probe circuit is connected to the  $V_{DD}$  and  $V_{SS}$  power supply terminals of a powered CMOS circuit, what voltage levels should test points TP1 and TP2 be adjusted to, in order for the probe to properly indicate "high" and "low" CMOS logic states? Consult a datasheet for the quad NAND gate numbered 4011. This is a legacy CMOS integrated circuit. <u>file 01275</u>

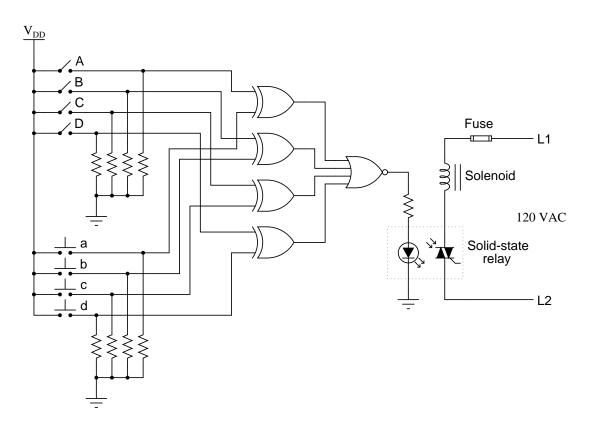

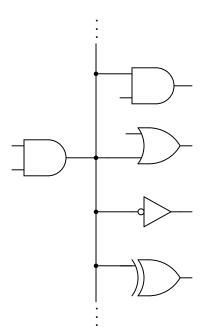

Here is a schematic diagram for a simple electronic combination lock, controlling power to a door lock solenoid:

The four pushbutton switches (a, b, c, and d) are accessible to the person wishing to enter the door. The four toggle switches (A, B, C, and D) are located behind the door, and are used to set the code necessary for entering.

Explain how this system is supposed to work. What are the logic states of the respective gate outputs when a matching code is entered through the pushbutton switches? How about when a non-matching code is entered?

Do you see any security problems with this door lock circuit? How easy would it be for someone to enter, who does not know the four-bit code? Do you have any suggestions for improving this lock design? file 01277

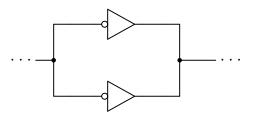

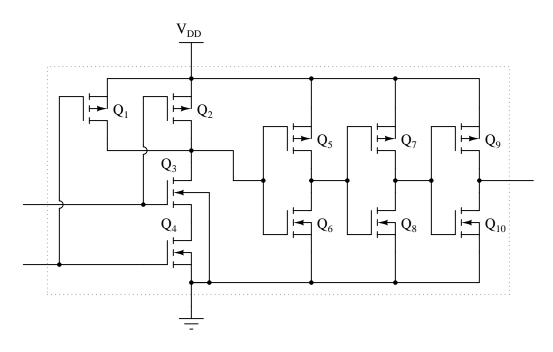

Many modern CMOS gate circuits are *buffered* with additional transistor stages on their outputs. For example, an unbuffered AND gate is shown here, with no more transistors than is necessary to fulfill the "AND" logic function:

One type of "buffered" CMOS AND gate looks like this:

As far as the basic logic function is concerned, the additional transistors are unnecessary. However, the "buffering" they provide does serve a useful function. What is that function? Are there any disadvantages to buffered logic gates, versus unbuffered?

In the early days of solid-state logic gate circuit technology, there was a very clear distinction between TTL and CMOS. TTL gates were capable of switching on and off very fast, required a tightly regulated power supply voltage, and used a lot of power. CMOS gates were not quite as fast as TTL, but could tolerate a much wider range of power supply voltages and were far less wasteful on power.

Then, during the 1980's a new technology known as *high-speed CMOS*, or HCMOS, entered the scene. Explain what HCMOS is, how it compares to the older TTL and CMOS families (54/74xx and 4xxx number series, respectively), and where it is often used. Hint: high-speed CMOS bears the same numerical codes as the old TTL 54xx and 74xx series ICs (e.g. 74HC00 instead of 7400).

<u>file 02773</u>

#### Question 31

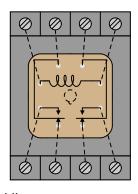

Though many electronics students and professionals alike associate semiconductor components with the word "digital," electromechanical relays are also digital logic (on or off) devices. In fact, some of the first digital computers were built with electromechanical relays as their active elements.

In what ways are electromechanical relays similar to semiconductor logic gates? In what ways do the two digital technologies differ?

<u>file 01287</u>

#### Question 32

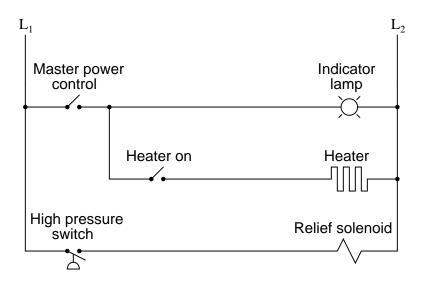

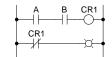

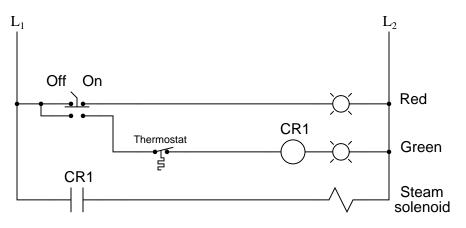

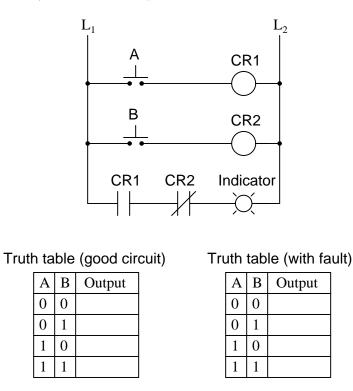

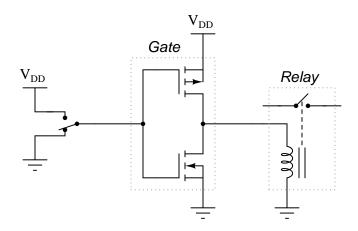

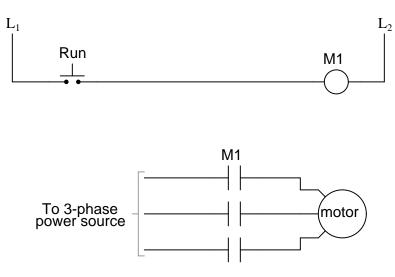

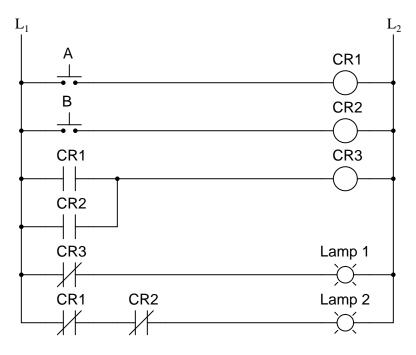

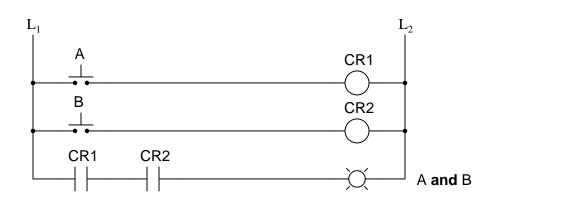

The following schematic is of a relay circuit that emulates a standard digital logic gate function:

Write a truth table for this circuit's function, and determine what name best represents it (AND, OR, NAND, NOR, or NOT).

<u>file 01288</u>

# ${\it Question}~33$

The following schematic is of a relay circuit that emulates a standard digital logic gate function:

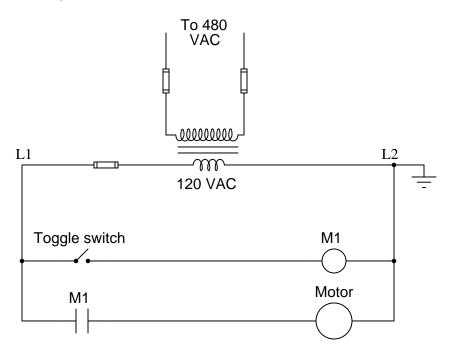

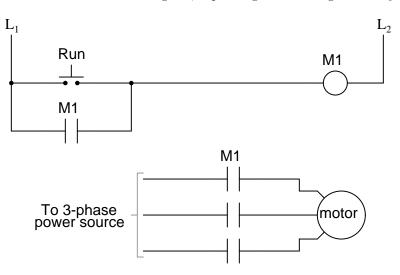

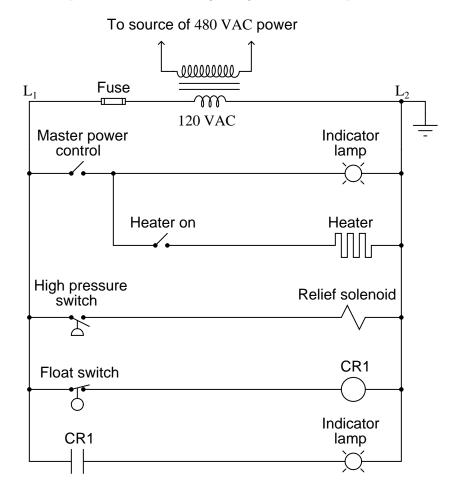

A type of electrical diagram convention optimal for representing electromechanical relay circuits is the *ladder logic diagram*. An example of a "ladder logic" diagram is shown here:

Each parallel circuit branch is represented as its own horizontal "rung" between the two vertical "rails" of the ladder. As you may have noticed, some of the symbols resemble standard electrical/electronic schematic symbols (toggle switches, for instance), while others are unique to ladder logic diagrams (heater elements, solenoid coils, lamps).

Where do the circuits shown obtain their electrical power? What do "L1" and "L2" represent? How are relay coils and contacts represented in a ladder logic diagram? Answer each of these questions by expanding upon the diagram shown above: draw the components necessary to show a complete electrical circuit (i.e. details of the power source), as well as an additional rung (or two) showing a relay coil actuated by some sort of switch contact, and the relay contact controlling power to a second indicator lamp.

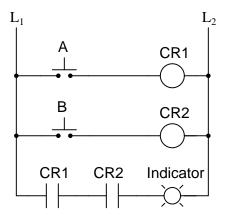

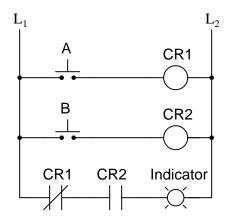

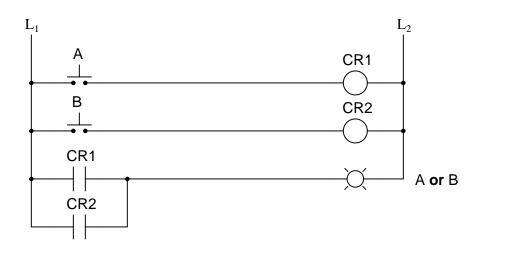

In ladder logic symbolism, an electromechanical relay coil is shown as a circle, and the contact(s) actuated by the coil as two parallel lines, almost like a capacitor symbol. Given this knowledge, interpret the following ladder logic diagram:

How do we know which relay contact is actuated by which relay coil? How does this convention differ from that of standard electrical/electronic schematic diagrams, where the relay coil is shown as an actual coil of wire (inductor symbol) with the contact "linked" to the coil by a dashed line? Also, what type of logic function behavior (AND, OR, NAND, or NOR) does the above circuit exhibit?

<u>file 02774</u>

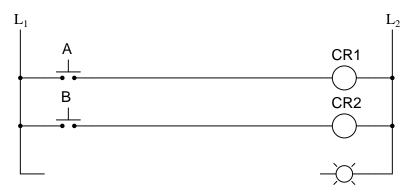

### Question 36

Complete the following ladder logic diagram so that an OR gate function is formed: the indicator lamp energizes if either switch A *or* switch B is actuated.

In ladder logic diagrams, a normally-open relay contact is drawn as a set of parallel lines, almost like a non-polarized capacitor in an electronic schematic diagram. Normally-closed relay contacts differ in symbolism by having a diagonal line drawn through them.

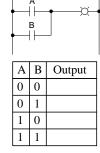

Analyze the following relay logic circuit, completing the truth table accordingly:

Truth table

| Α | В | Output |

|---|---|--------|

| 0 | 0 |        |

| 0 | 1 |        |

| 1 | 0 |        |

| 1 | 1 |        |

<u>file 02775</u>

# ${\it Question}~38$

Identify each of these relay logic functions by name (AND, OR, NOR, etc.) and complete their respective truth tables:

1 1

| А | В | Output |

|---|---|--------|

| 0 | 0 |        |

| 0 | 1 |        |

| 1 | 0 |        |

| 1 | 1 |        |

|   | A            | B  |  |

|---|--------------|----|--|

|   | A            | B  |  |

| - | $-\hat{\mu}$ | /  |  |

|   |              | 21 |  |

| Α | В | Output |

|---|---|--------|

| 0 | 0 |        |

| 0 | 1 |        |

| 1 | 0 |        |

| 1 | 1 |        |

| Γ | Á | B | Output |  |

|---|---|---|--------|--|

| ( | ) | 0 |        |  |

| ( | ) | 1 |        |  |

|   | 1 | 0 |        |  |

|   | 1 | 1 |        |  |

| А | В | Output |

|---|---|--------|

| 0 | 0 |        |

| 0 | 1 |        |

| 1 | 0 |        |

| 1 | 1 |        |

|   | A   | C      |    |

|---|-----|--------|----|

| Ī | CR1 |        | 0- |

| + |     |        | ф– |

|   |     |        |    |

|   | Δ   | Output |    |

| Α | Output |

|---|--------|

| 0 |        |

| 1 |        |

$\underline{\text{file } 01335}$

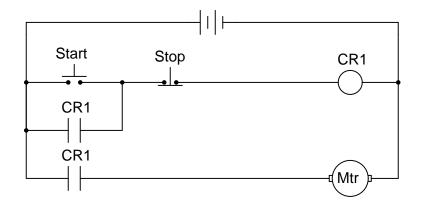

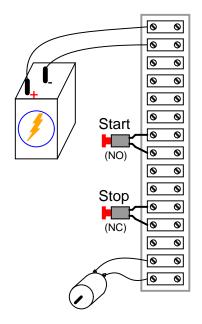

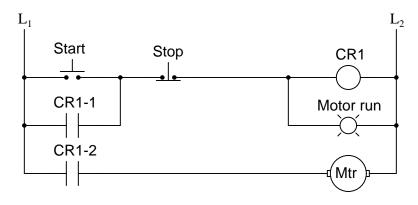

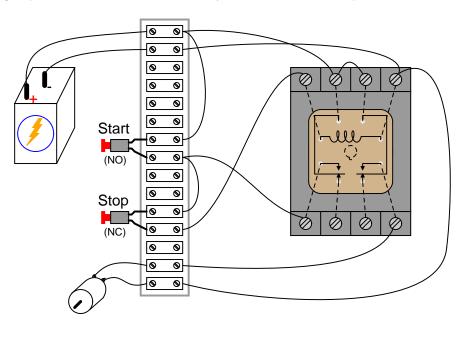

A *very* common application of electromechanical relay logic is motor control circuitry. Here is a ladder diagram for a simple DC motor control, where a momentary pushbutton switch starts the motor, and another pushbutton switch stops the motor:

Translate this ladder diagram into point-to-point connections between the following components (shown in the following illustration):

(Dashed lines represent connections between relay terminals and socket screw lugs, hidden from sight)

<u>file 01295</u>

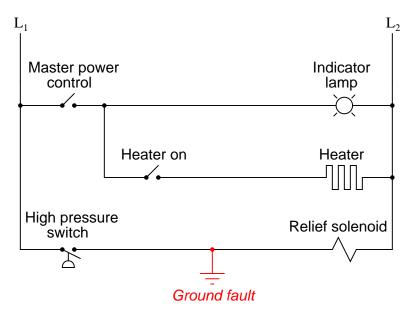

The following ladder logic diagram (for a steam heater control) contains a serious mistake:

This is a mistake I've seen many students make. Explain what the mistake is, and draw a corrected version of this relay circuit.

<u>file 01350</u>

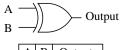

Identify each of these logic gates by name, and complete their respective truth tables:

Question 42

Totem-pole TTL gates usually differ greatly in their maximum source current versus maximum sink current ( $I_{OH}$  versus  $I_{OL}$ ). Identify which current rating is usually greater, and also explain why this is. file 01667

#### Question 43

In high-speed digital circuits, a very important logic gate parameter is *propagation delay*: the delay time between a change-of-state on a gate's input and the corresponding change-of-state on that gate's output. Consult a manufacturer's datasheet for any TTL logic gate and report the typical propagation delay times published there.

Also, explain what causes propagation delay in logic gates. Why isn't the change in output state instantaneous when an input changes states?

<u>file 01264</u>

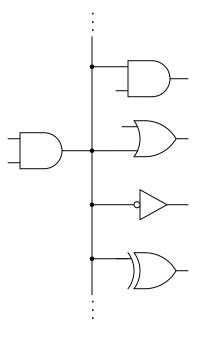

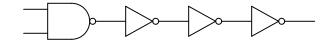

Logic gates are limited in the number of gate inputs which one output can reliably drive. This limit is referred to as *fan-out*:

Explain why this limit exists. What is it about the construction of TTL logic gates that inherently limits the number of TTL inputs that any one TTL output can drive? What might happen if this limit is exceeded?

Locate a datasheet for a TTL gate and research its fan-out limit. Note: this number will vary with the particular type of TTL referenced (L, LS, H, AS, ALS, etc.).

<u>file 01267</u>

# $\overline{\text{Question } 45}$

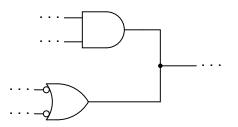

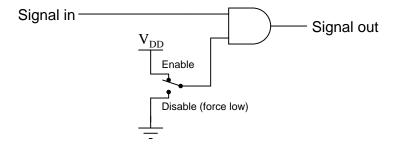

Explain why it is generally a *very bad* design practice to connect the outputs of different logic gates together, like this:

However, there are certain specific circumstances in which "paralleling" gate outputs is acceptable. For instance, it is okay to parallel two or more inverters, like this:

No damage will be done if open-collector gate outputs are paralleled, either (although the resulting logic function may be strange):

And finally, gates that have *tri-state* outputs may also have their outputs paralleled if certain precautions are taken:

What, specifically, causes gates to be damaged by "paralleling" their outputs? Generally speaking, what principle must be followed in order to "parallel" logic gate outputs without risk of damage? Explain how each of the three acceptable "paralleled" scenarios shown here meet this criterion.

Suggestion: the issue of multiple gates having to output logic voltage signals onto common conductors ("busses") is called *bus contention*. Try looking for this term in your research to see what useful information you find on paralleled gates!

An important parameter of logic gate circuitry is *noise margin*. What exactly is "noise margin," and how is it defined for logic gates?

Specifically, how much noise margin do digital circuits exclusively composed of TTL gates have?

Note: you will need to consult TTL gate datasheets to answer this question properly. file 01269

#### Question 47

In high-speed digital circuits, a very important logic gate parameter is *propagation delay*: the delay time between a change-of-state on a gate's input and the corresponding change-of-state on that gate's output. Consult a manufacturer's datasheet for any CMOS logic gate and report the typical propagation delay times published there.

Also, explain what causes propagation delay in logic gates. Why isn't the change in output state instantaneous when an input changes states?

file 01276

#### Question 48

Logic gates are limited in the number of gate inputs which one output can reliably drive. This limit is referred to as *fan-out*:

Explain why this limit exists. What is it about the construction of CMOS logic gates that inherently limits the number of CMOS inputs that any one CMOS output can drive? What might happen if this limit is exceeded?

Fan-out for CMOS is a quite different than fan-out for TTL. Most importantly is that CMOS fan-out is inversely proportional to operating frequency. Explain why.

An important parameter of logic gate circuitry is *noise margin*. What exactly is "noise margin," and how is it defined for logic gates?

Specifically, how much noise margin do digital circuits exclusively composed of CMOS gates have? How does this compare with the noise margin of all-TTL circuitry?

Note: you will need to consult CMOS gate datasheets to answer this question properly.  $\underline{file}~01270$

#### Question 50

A trend in CMOS logic gate development is toward lower and lower operating voltages. The "AUC" family of CMOS logic, for example, is able to operate at less than 2 volts  $V_{DD}$ !

Explain why this is a trend in modern logic circuit design. What benefits result from lower operating voltages? What possible disadvantages also result?

<u>file 01279</u>

<u>file 02787</u>

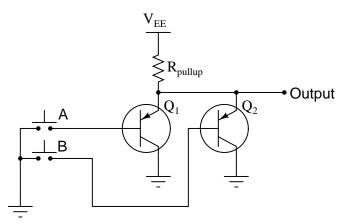

| Competency:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | AND gate, simple BJT logic                           | Version:                                 |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------|--|--|--|--|

| Schematic $V_{EE}$<br>$R_{pullup}$<br>$Q_1$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_1$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>$Q_2$<br>Q |                                                      |                                          |  |  |  |  |

| Given conditio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ons                                                  |                                          |  |  |  |  |

| V <sub>EE</sub> =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $R_{pullup} =$                                       |                                          |  |  |  |  |

| Truth table<br>Fault analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0 0<br>0 1<br>1 0<br>1 1<br>0 0<br>0 0<br>0 0<br>0 0 | A       B       Output         0       0 |  |  |  |  |

| Suppose con<br>What will hap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | nponentfails short                                   | ed                                       |  |  |  |  |

<u>file 02793</u>

<u>file 02791</u>

| Competency:                        | Gate-relay interposing                                    | Version:                  |  |  |  |

|------------------------------------|-----------------------------------------------------------|---------------------------|--|--|--|

| Schematic<br>+V<br>A<br>B<br>R     | $ R_2$                                                    | +V CR1<br>$D_1$ $Q_1$ $-$ |  |  |  |

| Given conditio                     |                                                           | P                         |  |  |  |

| +V =                               | $R_1 = R_2 =$                                             | R <sub>3</sub> =          |  |  |  |

| Truth table                        |                                                           |                           |  |  |  |

|                                    | Predicted                                                 | Actual                    |  |  |  |

|                                    | A B Output                                                | A B Output                |  |  |  |

|                                    | 0 0                                                       | 0 0                       |  |  |  |

|                                    | $\begin{array}{c c} 0 & 1 \\ \hline 1 & 0 \\ \end{array}$ | 0 1 1 0                   |  |  |  |

|                                    |                                                           |                           |  |  |  |

| Fault analysis                     |                                                           |                           |  |  |  |

| Suppose component fails open other |                                                           |                           |  |  |  |

| What will happen in the circuit?   |                                                           |                           |  |  |  |

|                                    |                                                           |                           |  |  |  |

$\underline{\text{file } 02795}$

#### **Project Grading Criteria**

PROJECT: \_

You will receive the highest score for which *all* criteria are met.

100 % (Must meet or exceed all criteria listed)

- A. Impeccable craftsmanship, comparable to that of a professional assembly

- B. No spelling or grammatical errors anywhere in any document, upon first submission to instructor

95 % (Must meet or exceed these criteria in addition to all criteria for 90% and below)

- A. Technical explanation sufficiently detailed to teach from, inclusive of every component (supersedes 75.B)

- B. Itemized parts list complete with part numbers, manufacturers, and (equivalent) prices for *all* components, including recycled components and parts kit components (supersedes 90.A)

- 90% (Must meet or exceed these criteria in addition to all criteria for 85% and below)

- A. Itemized parts list complete with prices of components purchased for the project, plus total price

- B. No spelling or grammatical errors anywhere in any document upon final submission

- 85 % (Must meet or exceed these criteria in addition to all criteria for 80% and below)

- A. "User's guide" to project function (in addition to 75.B)

- B. Troubleshooting log describing all obstacles overcome during development and construction

$\underline{80~\%}$  (Must meet or exceed these criteria in addition to all criteria for 75% and below)

- A. All controls (switches, knobs, etc.) clearly and neatly labeled

- B. All documentation created on computer, not hand-written (including the schematic diagram)

$\underline{75\%}$  (Must meet or exceed these criteria in addition to all criteria for  $\underline{70\%}$  and below)

- A. Stranded wire used wherever wires are subject to vibration or bending

- B. Basic technical explanation of all major circuit sections

- C. Deadline met for working prototype of circuit (Date/Time = \_\_\_\_\_ / \_\_\_\_ )

$70 \ \%$  (Must meet or exceed these criteria in addition to all criteria for 65%)

- A. All wire connections sound (solder joints, wire-wrap, terminal strips, and lugs are all connected properly)

- B. No use of glue where a fastener would be more appropriate

- C. Deadline met for submission of fully-functional project (Date/Time = \_\_\_\_\_ / \_\_\_\_ ) supersedes 75.C if final project submitted by that (earlier) deadline

65 % (Must meet or exceed these criteria in addition to all criteria for 60%)

- A. Project fully functional

- B. All components securely fastened so nothing is "loose" inside the enclosure

- C. Schematic diagram of circuit

60 % (Must meet or exceed these criteria in addition to being safe and legal)

- A. Project minimally functional, with all components located inside an enclosure (if applicable)

- B. Passes final safety inspection (proper case grounding, line power fusing, power cords strain-relieved)

0 % (If any of the following conditions are true)

- A. Fails final safety inspection (improper grounding, fusing, and/or power cord strain relieving)

- B. Intended project function poses a safety hazard

- C. Project function violates any law, ordinance, or school policy <u>file 03173</u>

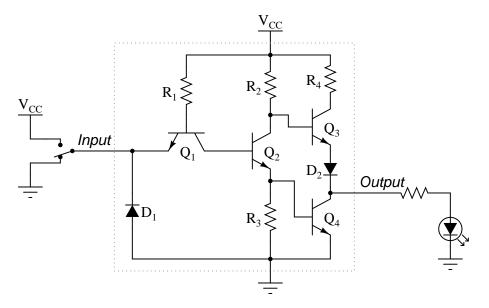

Predict how the operation of this logic gate circuit will be affected as a result of the following faults. Consider each fault independently (i.e. one at a time, no multiple faults):

- Diode  $D_1$  fails open:

- Diode  $D_1$  fails shorted:

- Diode  $D_2$  fails open:

- Resistor  $R_1$  fails open:

- Resistor  $R_2$  fails open:

- Resistor  $R_4$  fails open:

For each of these conditions, explain why the resulting effects will occur.  $\underline{file~03822}$

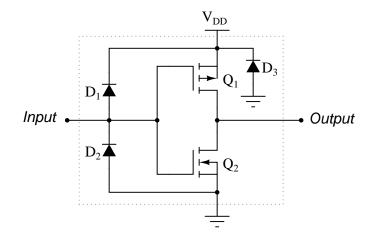

Predict how the operation of this logic gate circuit will be affected as a result of the following faults. Consider each fault independently (i.e. one at a time, no multiple faults):

- Diode  $D_1$  fails open:

- Diode  $D_1$  fails shorted:

- Diode  $D_2$  fails open:

- Resistor  $R_1$  fails open:

- Resistor  $R_2$  fails open:

- Transistor  $Q_2$  emitter terminal fails open:

- Transistor  $Q_3$  emitter terminal fails open:

For each of these conditions, explain why the resulting effects will occur.  $\underline{file~03823}$

## ${\it Question}~59$

Predict how the operation of this logic gate circuit will be affected as a result of the following faults. Consider each fault independently (i.e. one at a time, no multiple faults):

- Diode  $D_1$  fails open:

- Diode  $D_1$  fails shorted:

- Diode  $D_2$  fails open:

- Diode  $D_2$  fails shorted:

- Transistor  $Q_1$  fails open (drain to source):

- Transistor  $Q_2$  fails open (drain to source):

For each of these conditions, explain why the resulting effects will occur.  $\underline{file~03824}$

Identify at least three different transistor faults in this CMOS logic gate that could cause the output to fail *low*:

## <u>file 03825</u>

### Question 61

Identify at least two faults in this simple logic gate circuit that could cause its output to fail in the "low" logic state:

Be sure to explain why the proposed faults would cause the output to fail low.  $\underline{file~03830}$

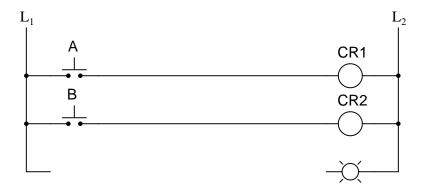

Complete the truth table for the following relay logic circuit, and then complete a second truth table for the same circuit with relay coil CR2 failed open:

Explain why the truth table will be modified as a result of the fault. <u>file 03826</u>

Predict how the operation of this motor control circuit will be affected as a result of the following faults. Consider each fault independently (i.e. one at a time, no multiple faults):

- "Stop" pushbutton switch fails open:

- Relay contact CR1-1 fails open:

- Relay contact CR1-2 fails open:

- Relay coil CR1 fails open:

For each of these conditions, explain why the resulting effects will occur.  $\underline{\mathrm{file}~03827}$

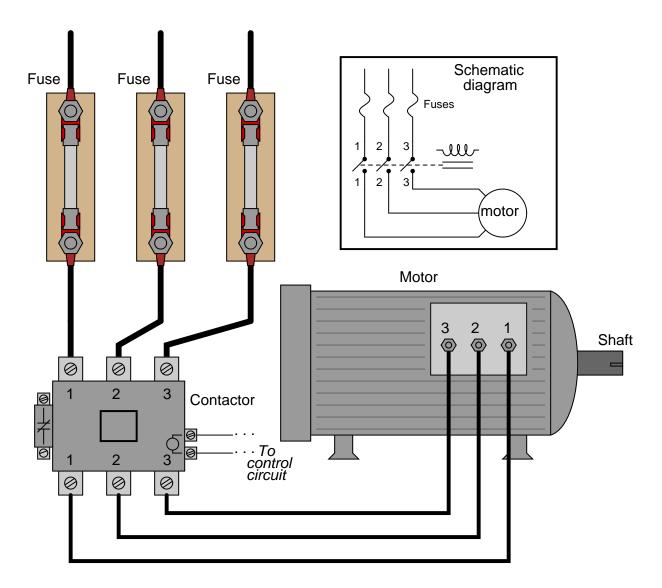

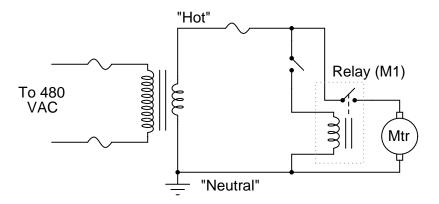

There is something wrong in this motor control circuit. When the start button is pressed, the contactor energizes but the motor itself does not run:

Identify a good place to check with your multimeter to diagnose the nature of the fault, and explain your reasoning.

$\underline{\mathrm{file}~03828}$

Identify at least three independent faults that could cause this motor not to start:

For each of the proposed faults, explain why they would prevent the motor from starting.  $\underline{file~03829}$

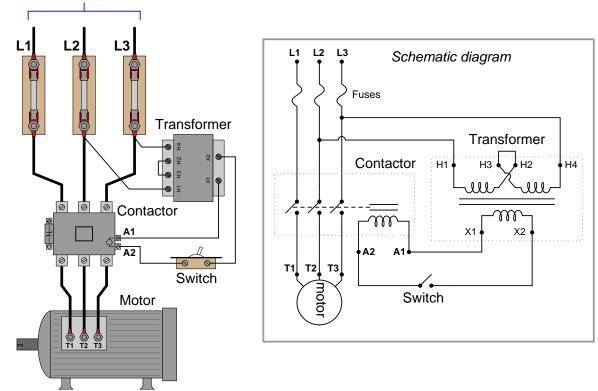

# To $3-\phi$ , 480 volt power source

A student builds the following circuit to demonstrate the behavior of a NAND gate:

When the student tests the circuit, though, something is wrong:

- Both switches LOW, no light.

- One switch HIGH, the other switch LOW; LED lights up.

- One switch LOW, the other switch HIGH; LED lights up.

- Both switches HIGH, no light.

Instead of acting as a NAND gate should, it seems to behave as if it were an Exclusive-OR gate! Examining the circuit for mistakes, the student discovers missing power connections to the chip – in other words, neither  $V_{DD}$  nor  $V_{SS}$  are connected to the power source.

While this certainly is a problem, the student is left to wonder, "How did the circuit ever function *at all*?" With no power connected to the chip, how is it possible that the LED ever lit in *any* condition?

<u>file 01561</u>

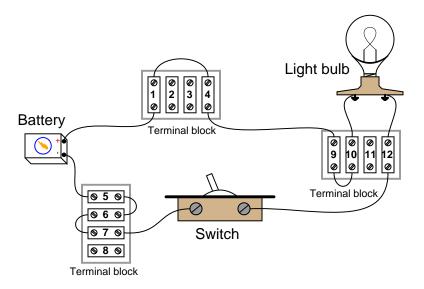

Examine the following illustration of a simple battery-switch-lamp circuit, connected together using screw-terminal blocks, each connection point on each terminal block identified by a unique number:

Determine whether or not voltage should be present between the following pairs of terminal block points with the switch in the ON position:

- Points 1 and 5:

- Points 6 and 7:

- Points 4 and 10:

- Points 9 and 12:

- Points 6 and 12:

- Points 9 and 10:

- Points 4 and 7:

Now, determine whether or not voltage should be present between the following pairs of terminal block points with the switch in the OFF position:

- Points 1 and 5:

- Points 6 and 7:

- Points 4 and 10:

- Points 9 and 12:

- Points 6 and 12:

- Points 9 and 10:

- Points 4 and 7:

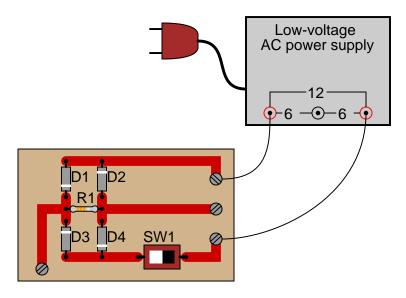

The circuit shown here is called a "bridge rectifier," and its purpose is to convert alternating current (from the "power-supply" unit) into direct current. Suppose you were instructed to check the continuity of the switch (SW1) mounted on the printed circuit board. What would be a fast and effective way of testing this switch's continuity (ideally, without removing the switch from the circuit board)?

#### file 00100

#### Question 69

Identify which of these are true statements:

- 1. Between two points that are electrically common to each other, there is guaranteed to be zero voltage.

- 2. If zero voltage is measured between two points, those points must be electrically common to each other.

- 3. Between two points that are not electrically common to each other, there is guaranteed to be voltage.

- 4. If voltage is measured between two points, those points must not be electrically common to each other.

<u>file 00184</u>

# $\overline{\text{Question 70}}$

| Bodily effect                        | Gender | DC     | 60 Hz AC | 10 kHz AC |

|--------------------------------------|--------|--------|----------|-----------|

| Slight sensation at                  | Men    | 1 mA   | 0.4 mA   | 7 mA      |

| point(s) of contact                  | Women  | 0.6 mA | 0.3 mA   | 5 mA      |

| Threshold of bodily                  | Men    | 5.2 mA | 1.1 mA   | 12 mA     |

| perception                           | Women  | 3.5 mA | 0.7 mA   | 8 mA      |

| Pain, with voluntary muscle control  | Men    | 62 mA  | 9 mA     | 55 mA     |

| maintained                           | Women  | 41 mA  | 6 mA     | 37 mA     |

| Pain, with loss of                   | Men    | 76 mA  | 16 mA    | 75 mA     |

| voluntary muscle<br>control          | Women  | 51 mA  | 10.5 mA  | 50 mA     |

| Severe pain,                         | Men    | 90 mA  | 23 mA    | 94 mA     |

| difficulty breathing                 | Women  | 60 mA  | 15 mA    | 63 mA     |

| Possible heart<br>fibrillation after | Men    | 500 mA | 100 mA   | $\geq$    |

| three seconds                        | Women  | 500 mA | 100 mA   | $\geq$    |

An American researcher named Charles Dalziel performed experiments with both human and animal subjects to determine the effects of electric currents on the body. A table showing his research data is presented here:

**Important Note:** Dalziel's human test subjects were men and women in good health, with no known heart conditions or any other abnormalities that would have compromised their safety. In other words, these data points represent best-case scenarios, and do not necessarily reflect the risk to persons in poorer states of health.

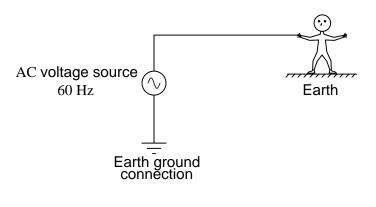

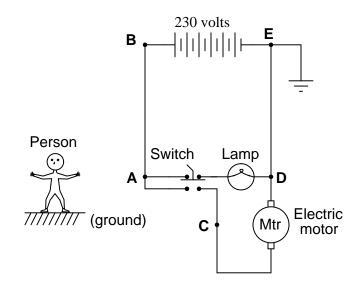

Assuming a wire-to-hand contact resistance of 1500  $\Omega$ , 4400  $\Omega$  of resistance for foot-to-ground contact, 50  $\Omega$  internal body resistance, 200  $\Omega$  of resistance through the soil from the person's location to the earth ground point, and a female victim, calculate the amount of voltage necessary to achieve each of the listed shock conditions (threshold of perception, pain, etc.) for the following circuit:

Determine whether or not a shock hazard exists for a person standing on the ground, by touching any one of the points labeled in this circuit:

- Point "A"

- Point "B"

- Point "C"

- Point "D"

- Point "E"

file 00303

### Question 72

The following recommendations came from a flyer published by an electric power utility. Read and comment on their instructions regarding downed power lines:

Assume any downed line is an energized power line. If a power line falls on your car while you are driving, slowly drive on until you are completely clear of the line (but do not drive over it). If your car is immobilized, stay in it until help arrives. Call for help from a cell phone if you have one.

If you need to escape from a vehicle, such as for a car fire, jump clear of the car. Electricity is not only traveling through the vehicle, but may also be traveling in the ground around the area. Keep your arms crossed over your chest while you jump, and both feet together. Do NOT touch the vehicle and the ground at the same time. Once you land on the ground, shuffle clear of the area, keeping both feet together, on the ground, and touching at all times. Continue shuffling until you're at least 30 feet from the accident site.

Why do you suppose the following actions were recommended?

- Do not drive over a downed power line.

- Stay in the car if possible.

- Do not touch the car and the ground at the same time.

- Shuffle away from the car (rather than walk), with both feet together.

When securing equipment for safe maintenance, special *tags* are attached with the lock(s) used to keep circuit breakers and other disconnect devices in the open (off) state. A typical "lockout" tag looks something like this:

What is the purpose of attaching such a tag to an electrical disconnect device in addition to locking it in the open position? Why is a lock, by itself, not sufficient from a safety perspective?  $\frac{file\ 00573}{file\ 00573}$

#### Question 74

Suppose you are finishing a maintenance project where an electric motor was locked out and tagged, and now the work is complete. Your lock is the last one to be removed from the circuit breaker, everyone else already having taken their locks and tags off. What should you do before removing your lock and turning the circuit breaker back on?

# Question 75

file 00575

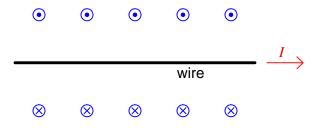

When engineers and physicists draw pictures illustrating the magnetic field produced by a straight current-carrying wire, they usually do so using this notation:

Explain what the circle-and-dot and circle-and-cross symbols mean, with reference to the *right-hand* rule.

<u>file 03498</u>

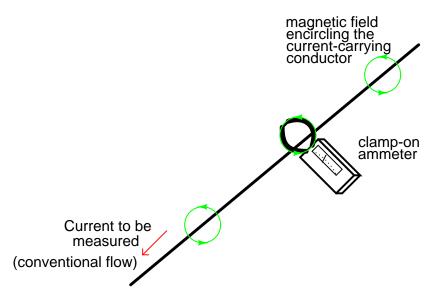

A very useful method of measuring current through a wire is to measure the strength of the magnetic field around it. This type of ammeter is known as a *clamp-on* ammeter:

Knowing the principle behind this meter's operation, describe what current values will be indicated by the three clamp-on ammeters in this circuit:

file 00262

•

Write an equation that expresses the amount of magnetic flux  $(\Phi)$  produced by an electromagnet, given the amount of electric current (I), the number of turns in the wire coil (N), and the reluctance of the core material  $(\Re)$ .

$\underline{\text{file } 00258}$

## Question 78

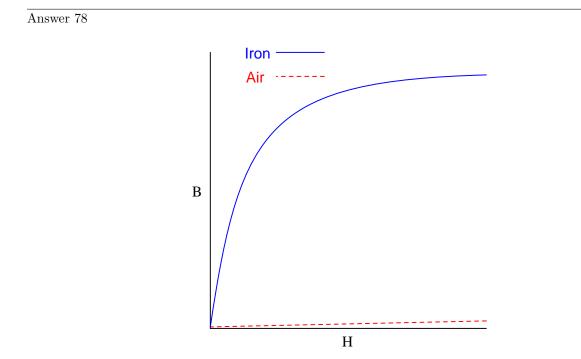

$\int f(x) dx$  Calculus alert!

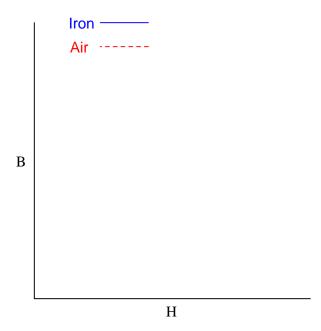

Plot the relative B-H curves for a sample of air and a sample of iron, in proportion to each other (as much as possible):

What do you notice about the slope (also called the derivative, or  $\frac{dB}{dH}$ ) of each plot? <u>file 03515</u>

## Question 79

If a wire coil with 450 turns is exposed to a magnetic flux increasing at a rate of 0.008 Webers per second, how much voltage will be induced across the coil?

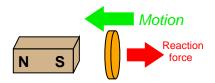

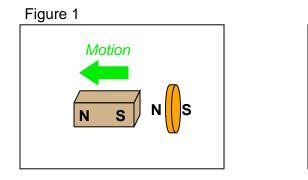

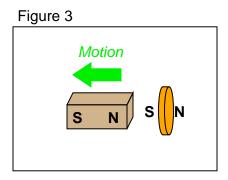

Lenz's Law describes the opposition to changes in magnetic flux resulting from electromagnetic induction between a magnetic field and an electrical conductor. One apparatus capable of demonstrating Lenz's Law is a copper or aluminum disk (electrically conductive, but non-magnetic) positioned close to the end of a powerful permanent magnet. There is no attraction or repulsion between the disk and magnet when there is no motion, but a force will develop between the two objects if either is suddenly moved. This force will be in such a direction that it tries to resist the motion (i.e. the force tries to maintain the gap constant between the two objects):

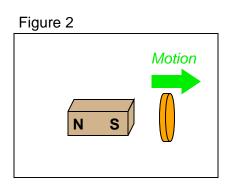

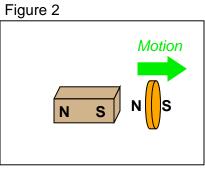

We know this force is magnetic in nature. That is, the induced current causes the disk itself to *become* a magnet in order to react against the permanent magnet's field and produce the opposing force. For each of the following scenarios, label the disk's induced magnetic poles (North and South) as it reacts to the motion imposed by an outside force:

Figure 3

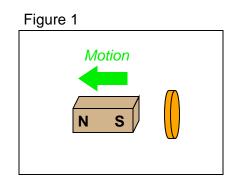

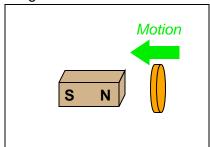

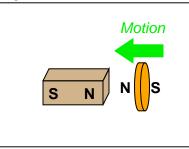

Combining Lenz's Law with the right-hand rule (or left-hand rule, if you follow electron flow instead of conventional flow) provides a simple and effective means for determining the direction of induced current in an induction coil. In the following examples, trace the direction of current through the load resistor:

<u>file 01787</u>

## ${\it Question}~82$

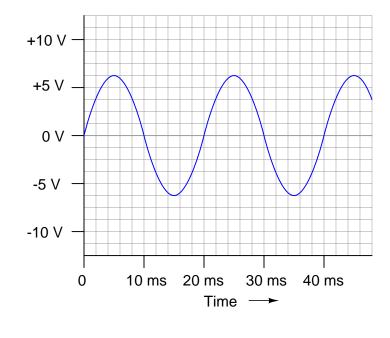

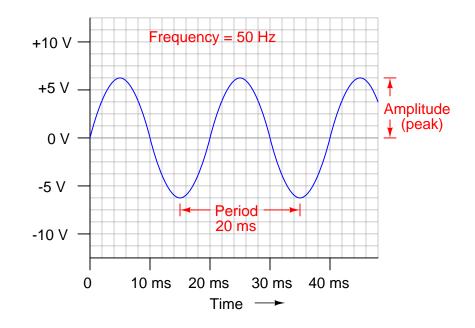

Apply the following terms to this graph of an AC voltage measured over time:

- Frequency

- Period

- Hertz

- Amplitude

<u>file 00054</u>

#### Question 83

*Radio waves* are comprised of oscillating electric and magnetic fields, which radiate away from sources of high-frequency AC at (nearly) the speed of light. An important measure of a radio wave is its *wavelength*, defined as the distance the wave travels in one complete cycle.

Suppose a radio transmitter operates at a fixed frequency of 950 kHz. Calculate the approximate wavelength ( $\lambda$ ) of the radio waves emanating from the transmitter tower, in the metric distance unit of meters. Also, write the equation you used to solve for  $\lambda$ .

## ${\it Question}~84$

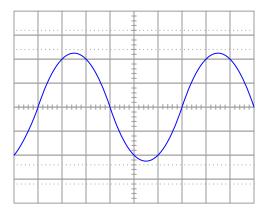

Determine the RMS amplitude of this sinusoidal waveform, as displayed by an oscilloscope with a vertical sensitivity of 0.2 volts per division:

## $\underline{\mathrm{file}~01818}$

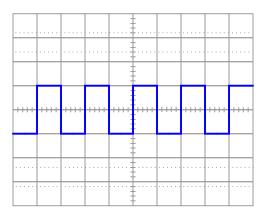

## Question 85

Determine the RMS amplitude of this square-wave signal, as displayed by an oscilloscope with a vertical sensitivity of 0.5 volts per division:

<u>file 01824</u>

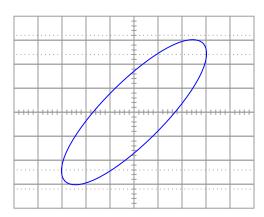

Calculate the amount of phase shift indicated by this Lissajous figure:

file 03577

#### Question 87

Read the following quotation, and then research the term **microcontroller** to see what relevance it has to the quote:

I went to my first computer conference at the New York Hilton about 20 years ago. When somebody there predicted the market for microprocessors would eventually be in the millions, someone else said, "Where are they all going to go? It's not like you need a computer in every doorknob!"

Years later, I went back to the same hotel. I noticed the room keys had been replaced by electronic cards you slide into slots in the doors.

There was a computer in every doorknob.

– Danny Hillis

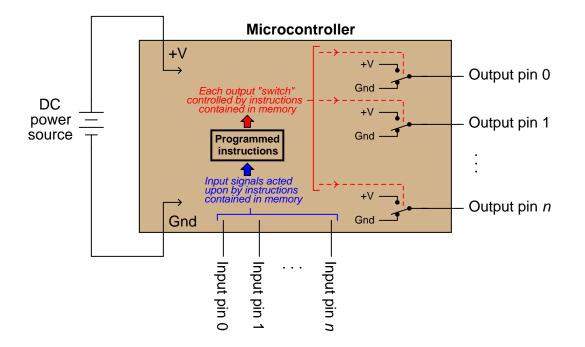

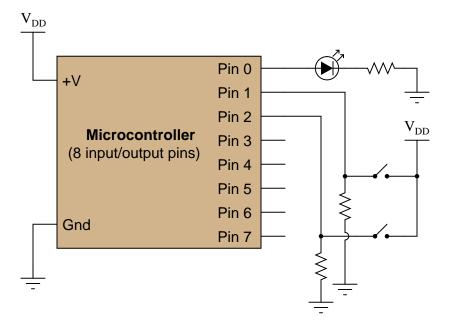

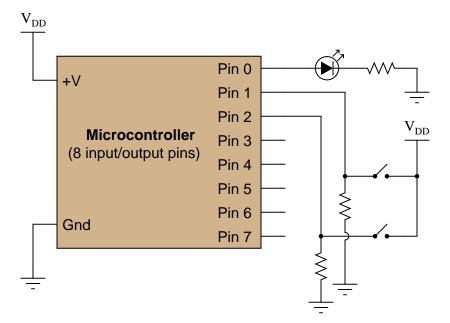

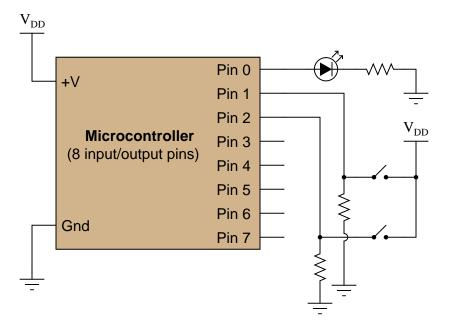

A microcontroller unit, or MCU, is a specialized type of digital computer used to provide automatic sequencing or control of a system. Microcontrollers differ from ordinary digital computers in being very small (typically a single integrated circuit chip), with several dedicated pins for input and/or output of digital signals, and limited memory. Instructions programmed into the microcontroller's memory tell it how to react to input conditions, and what types of signals to send to the outputs.

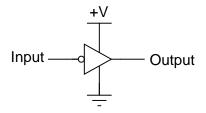

The simplest type of signal "understood" by a microcontroller is a discrete voltage level: either "high" (approximately +V) or "low" (approximately ground potential) measured at a specified pin on the chip. Transistors internal to the microcontroller produce these "high" and "low" signals at the output pins, their actions being modeled by SPDT switches for simplicity's sake:

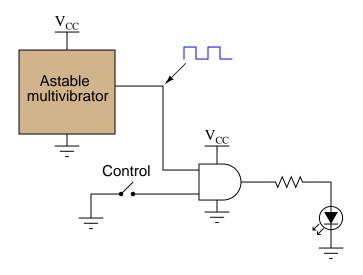

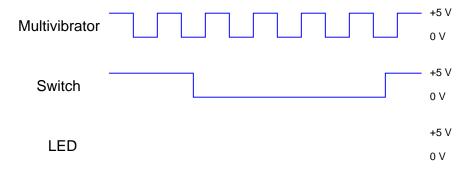

Microcontrollers may be programmed to emulate the functions of digital logic gates (AND, OR, NAND, NOR, etc.) in addition to a wide variety of combinational and multivibrator functions. The only real limits to what a microcontroller can do are memory (how large of a program may be stored) and input/output pins on the MCU chip.

However, microcontrollers are themselves made up of many thousands (or millions!) of logic gate circuits. Why would it make sense to use a microcontroller to perform a logic function that a small fraction of its constituent gates could accomplish directly? In other words, why would anyone bother to program a microcontroller to perform a digital function when they could build the logic network they needed out of fewer gate circuits?

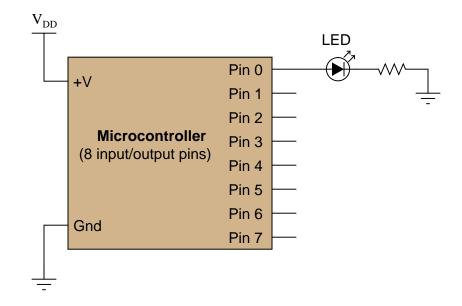

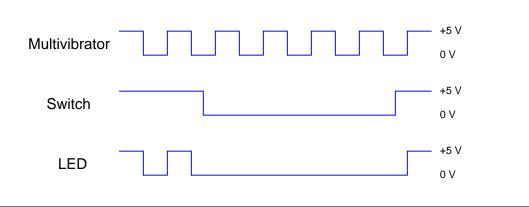

A student decides to build a light-flasher circuit using a microcontroller instead of a 555 timer or some other hard-wired astable circuit. Unfortunately, there is a problem somewhere. When first powered up, the LED lights on for 1 second, then turns off and never turns back on. The only way the LED ever comes back on is if the MCU is reset or its power is cycled off and on:

#### Pseudocode listing

Declare PinO as an output BEGIN Set PinO HIGH Pause for 1 second Set PinO LOW END

A fellow student, when asked for help, modifies the program listing and re-sends it from the personal computer where it is being edited to the microcontroller, through a programming cable. The program listing now reads as such:

#### Pseudocode listing

Declare PinO as an output LOOP Set PinO HIGH Pause for 1 second Set PinO LOW ENDLOOP

When the MCU is reset with the new program, the LED starts blinking on and off . . . sort of. The LED is "on" most of the time, but once every second it turns off and then immediately comes back on. In fact, the "off" period is so brief it is barely noticeable.

What the student wanted was a 50% duty cycle: "on" for 1 second, then "off" for 1 second, repeating that cycle indefinitely. First, explain the significance of the classmate's program modification, and then modify the program listing again so that the LED does what the student wants it to.

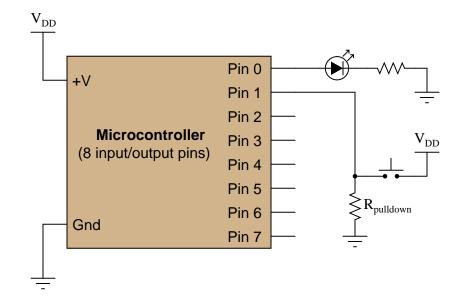

A student decides to build a light-flasher circuit using a microcontroller. The LED is supposed to blink on and off only when the pushbutton switch is depressed. It is supposed to turn off when the switch is released:

#### Pseudocode listing

Declare PinO as an output Declare Pin1 as an input WHILE Pin1 is HIGH Set PinO HIGH Pause for 0.5 seconds Set PinO LOW Pause for 0.5 seconds ENDWHILE

The LED blinks on and off just fine as long as the pushbutton switch is held when the MCU is powered up or reset. As soon as the switch is released, the LED turns off and never comes back on. If the switch was never pressed during start-up, the LED never comes on! Explain what is happening, and modify the program as necessary to fix this problem.

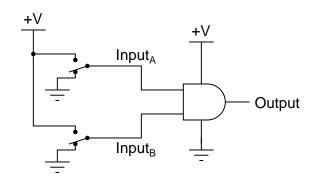

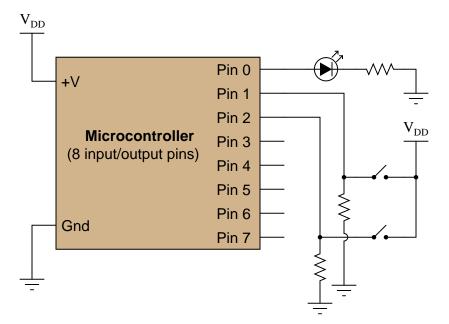

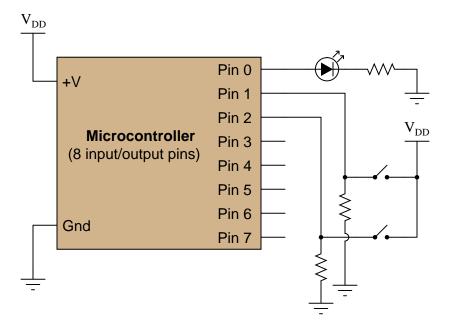

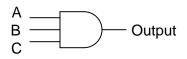

Examine the following schematic diagram and program listing (written in "pseudocode" rather than a formal programming language) to determine what type of basic logic function is being implemented in this microcontroller unit:

#### **Pseudocode listing**

Declare PinO as an output Declare Pin1 and Pin2 as inputs LOOP IF Pin1 is HIGH, set PinO HIGH ELSEIF Pin2 is HIGH, set PinO HIGH ELSE set PinO LOW ENDIF ENDLOOP

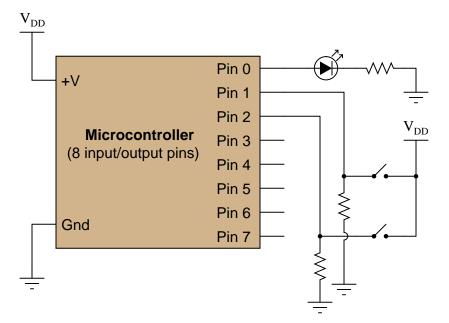

Examine the following schematic diagram and program listing (written in "pseudocode" rather than a formal programming language) to determine what type of basic logic function is being implemented in this microcontroller unit:

## **Pseudocode listing**